Jk триггер принцип работы кратко и схемы

Обновлено: 02.07.2024

Всем доброго времени суток! Сегодняшний мой пост посвящён цифровым микросхемам, которые имеют память. Подобно тому, как человек помнит события из своей жизни, так и эти микросхемы могут долго хранить заложенную в них информацию, а когда необходимо выдавать её.

Такими цифровыми микросхемами являются триггеры (англ. – Trigger или Flip-Flop). В отличие от простых логических микросхем, которые называют комбинационными (НЕ, И-НЕ, ИЛИ и другие) и их сигналы на выходе чётко соответствуют сигналам на входе, то триггеры относятся к последовательным или последовательностным микросхемам, уровень выходного напряжения которых, зависит от того в какой последовательности поступали сигналы на вход триггера. С помощью триггеров строят более сложные цифровые микросхемы.

Для сборки радиоэлектронного устройства можно преобрески DIY KIT набор по ссылке.

Сигналы, поступившие на вход триггера, могут храниться только до тех пор, пока на него подается напряжение питания. После каждого включения триггера на его выходах появляются случайные логические уровни напряжения. Триггеры обладают очень высоким быстродействием, сравнимым с задержками при переключении простейших логических элементов, однако объём хранимой информации мал. Один триггер может хранить только один сигнал или бит.

Внутреннее устройство триггера

Не вдаваясь в глубину схемотехники триггера, скажу сразу, что простейший триггер представляет собой схему из двух логических элементов, взаимодействуя между собой с помощью положительной обратной связи, которая обеспечивает нахождения выходов триггера в одном их двух логических состояний неограниченное время.

Схема триггерной ячейки на логических элементах (RS триггер).

Как говорилось выше, входы триггера R и S реагируют на низкий логический уровень и сигналы на них должны поступать с некоторой разницей во времени. Опишем работу данной схемы. Когда на обоих входах триггера присутствует низкий логический уровень, то это никак не отразится на уровне напряжения на выходах. Когда на вход S поступит сигнал лог. 1, то на выходах Q будет лог. 0, а на –Q – лог. 1. Если теперь на вход R триггера поступит лог. 1, то выходные сигналы не изменятся. И наконец если изменить уровень сигнала на входе S с высокого на низкий уровень, то на выходе триггера Q будет лог. 1, а на –Q – лог. 0. Таким образом, для данной триггерной ячейки можно составить таблицу истинности.

Таблица истинности триггерной ячейки (RS триггер).

Схемы с такой таблицей истинности называются RS триггерами. RS триггеры служат основой для многих динамических устройств: делители частоты, счётчики, регистры. Кроме вышеописанного RS триггера существует ещё несколько типов триггеров, которые отличаются методом управления, входными и выходными сигналами. Все современные триггеры объединены в серии цифровых микросхем:

- RS триггеры – самый простой и редко используемый триггер, имеет обозначение ТР;

- JK триггер – имеет сложное управление, обозначение ТВ;

- D триггер – самый распространённый и имеет сложность среднюю, обозначение ТМ;

RS триггеры

Рассмотрим принцип работы RS триггера возьмём микросхему К555ТР2.

Обозначение RS триггера К555ТР2

Данная микросхема имеет 4 RS триггера, два из которых имеют по одному R входу и одному S входу, а два других – по одному R входу и по два S входа, объединенных по функции И. Все 4 RS триггера данной микросхемы имеют по одному прямому выходу. Принцип работы данных триггеров не отличатся от триггерной ячейки описанной выше. Импульс с низким уровнем на входе триггера R приводит состояние выхода к низкому уровню, а импульс с низким логическим уровнем на входе триггера S – состояние выхода в высоком логическом уровне. В случае появления одновременных сигналов на входах триггера переводит его выход в состояние лог. 1, а после окончания импульсов в одно из устойчивых состояний.

JK триггер

Микросхема типа К555ТВ9, является представителем семейства JK триггеров, который имеет следующий принцип работы.

Обозначение JK триггера К555ТВ9.

Микросхема К555ТВ9 содержит два JK триггера. Триггеры данного типа сложнее по устройству и по управлению по сравнению с RS триггером. В дополнение к стандартным входам R и S, которые работают аналогично с RS триггером, в JK триггере имеются информационные входа J и K, а также вход синхронизации С.

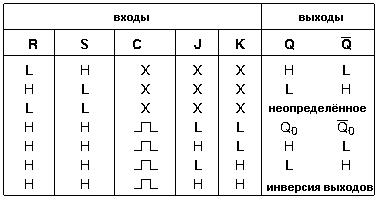

Таблица истинности JK триггера.

D триггер

D триггер является самым используемым, а по управлению он занимает промежуточное положение между RS триггером и JK триггером. Представителем D триггеров является микросхема К555ТМ2.

Обозначение D триггера микросхемы К555ТМ2

В составе данной микросхемы содержится два D триггера, которые имеют два входа сброса и установки R и C, информационный вход D (англ. Dalay – задержка) триггера и один тактируемый вход С триггера, а также два выхода: прямой Q и инверсный –Q. Как и все триггеры, у которых имеется тактируемый вход С, принцип работы D триггера основан на переключении уровней напряжений на выходе триггера только стробированием по входу С. Таким образом можно составить таблицу истинности D триггера.

Таблица истинности D триггера

D триггер является наиболее универсальным потому, что данным триггером можно заменить все остальные RS триггеры и JK триггеры. Для замены RS триггера необходимо просто не использовать входы D и C входы D триггера, а относительно JK триггера, то для большинства схем одной пары входов вполне достаточно. Ниже приведены схемы замены триггеров

Схема замены D триггером: RS триггера (слева) и JK триггера в счётном режиме (справа).

Теория это хорошо, но необходимо отрабатывать это всё практически ПОПРОБЫВАТЬ МОЖНО ЗДЕСЬ

Существует несколько различных типов триггеров, из которых JK считается наиболее универсальным. JK-триггеры находят применение и как отдельные микросхемы, и в качестве элементов для процессоров. Их использование позволяет создавать схемы, действующие по достаточно сложным алгоритмам.

Триггер — что это за устройство

Он представляет собой электронное устройство, способное на протяжении длительного времени сохранять одно из двух или нескольких состояний. Это происходит до тех пор, пока на него подаётся электропитание. Существует несколько типов триггеров, каждый из которых имеет свою сферу применения. Фактически они являются базовыми элементами. На их основе создаются различные цифровые электронные устройства.

Триггер способен на протяжении довольно длительного промежутка времени пребывать в одном устойчивом режиме из нескольких возможных, а затем под действием входных сигналов переходить из одного режима в другой. Состоит он из элементарных логических элементов, функционирующих по правилам математической логики. Это могут быть ИЛИ-НЕ и И-НЕ. Первые из них функционируют в одноединичном прямом коде, то есть, на выходе одного из элементов будет 1, а на выходах других — 0. Устройство с элементами второго вида работает в однонулевом инверсном коде: на выходе одного из них 0, а на выходах других — 1.

Как работает JK-триггер

Это электронное устройство работает строго по определённому алгоритму, предусматривающему поступление входных значений и обеспечивающему формирование выходных.

Как видно из схемы, триггер имеет три входа, на которые поступают следующие сигналы:

- J, K — информационные сигналы. Они принимают значение 0 или 1. Каждой комбинации соответствует определённое выходное значение.

- C — двоичный сигнал, который определяет, будут ли меняться выходные сигналы на основании действующего алгоритма или нет. Обычно срабатывание происходит при переходе от единичного к нулевому значению. Также говорят, что срабатывание происходит при отрицательном фронте сигнала.

В этой схеме имеется два выхода:

- Q — прямой. Выдает значение, которое на данный момент хранится в триггере.

- Q1 также обозначают как Q с горизонтальной чертой сверху — инверсный. Этот сигнал всегда будет противоположным по отношению к Q.

JK-триггер — это своего рода усовершенствованный RS-триггер. В последнем наблюдается одно запрещённое состояние, использование которого приводит к неопределённому результату на выходе. В JK-устройстве такое состояние исключено. В остальном оба элемента действуют аналогично.

JK-триггер — универсальное устройство. На его базе можно построить простой и асинхронный Т-триггер, D-триггер, синхронный RS-триггер

Есть еще комбинированный JK-триггер. От универсального он отличается двумя дополнительными асинхронными входами S и R. Последние позволяют предварительно установить устройство в определенный режим (логического нуля или единицы).

Алгоритм работы

Если на вход C поступает сигнал, равный нулю, то выходные значения будут сохранены. Как только он станет равным единице, формирование значения Q будет происходить по следующим правилам:

- Если J=K=0, режим триггера не меняется.

- Когда J и K равны 1, происходит изменение состояния элемента на противоположное при поступлении каждого тактового импульса. В этом случае триггер функционирует идентично делителю частоты. Такой режим работы называют счётным, поскольку его использование позволяет осуществлять подсчёт определённых событий.

- При K = 1, J = 0 выходное значение принимает нулевое значение.

- Если K = 0, J = 1, тогда на выходе будет получена единица.

Алгоритм работы отображает таблица истинности JK-триггера, так как каждой входной комбинации значений соответствует строго определённая выходная.

Разобраться в работе триггера помогает еще временная диаграмма, на которой графически отображаются сигнальные импульсы, присутствующие одновременно на входах и выходах устройства.

На приведённой диаграмме срабатывание происходит по фронту импульса C с задержкой. Момент, когда это происходит, зависит от конкретной схемы реализации.

Как реализованы функции JK-триггера

Далее рассмотрим принцип работы универсального JK-триггера для каждой из возможных ситуаций. Для удобства описания использования микросхем И-НЕ они будут пронумерованы. Микросхема слева вверху схемы обозначена D1. Та, что под ней — D2. Находящаяся справа вверху — D3, справа внизу — D4.

На J и K нулевые значения

В этом случае на первых двух микросхемах применение логического элемента И приведёт к получению нуля, но поскольку нужно брать дополнительное значение, будет образована единица на обеих микросхемах.

Так как выходное значение от Q и от отрицания Q будет подано на вход микросхем D3 и D4 (значение в момент времени n), то элемент И вместе с логической единицей просто передаст на выход это значение.

При этом необходимо учитывать, что значение отрицания Q будет подано на микросхему для формирования Q и наоборот. После этого на выходе микросхемы будет применено НЕ, которое сохранит прежнее значение. Таким образом, комбинация J = K = 0 приведёт к сохранению прежнего значения. Нужно помнить, что работа в соответствии с указанным алгоритмом возможна лишь в момент поступления отрицательного фронта сигнала на C. На протяжении остального времени ничего происходить не будет.

На J и K единичные значения

Если Q = 0, то отрицание Q будет равняться 1. Если на вход элемента D1 будет подано J = 1 и отрицание Q, тогда на выходе D1 сформируется ноль. С учетом того, что на входе D3 имеется логический 0, на выходе будет получена единица как результат функционирования элемента И-НЕ. Следовательно, в момент времени n + 1 сформируется инвертированное значение.

Для D2 и D4 значения находят аналогичным образом в соответствии с таблицей истинности JK-триггера.

J и K имеют противоположные значения

Если J = 1 и K = 0, то на вход D1 поступят сигналы J = 1 и отрицание Q. Результатом логического И станет отрицание Q. После инвертирования значение приобретает Q. На вход D3 поступят одновременно Q и отрицание Q. Поэтому результатом логического И всегда будет ноль. Этот результат не зависит от предыдущего значения отрицания Q.

В случае, когда J = 0, K = 1 аналогичным образом можно убедиться, что Q = 0.

Области применения триггера

JK-триггер можно рассматривать как ячейку памяти объёмом в 1 бит. Подача управляющих сигналов позволяет устанавливать значение памяти, равное 0 или 1, сохранять или инвертировать его, что наглядно демонстрирует таблица переходов.

На практике JK-устройства выпускают в виде микросхем, действующих в соответствии с таблицей истинности синхронного триггера. Обычно для того, чтобы запрограммировать определённый алгоритм сначала составляют логическую формулу преобразования двоичных сигналов. Затем реализовывают её в виде платы, включающей в себя установку триггеров.

Триггеры нашли широкое применение в таких компонентах вычислительных систем, как счетчики, регистры, процессоры и ОЗУ. Универсальность JK-триггеров позволяет использовать их в устройствах с разным уровнем сложности логики работы. Например, на основе JK-триггера можно собрать делитель частоты на 10. При поступлении на вход данного устройства импульсов частотой 10 кГц на выходе будут получены значения, равные 1 кГц. Подобные схемы получили название декадного делителя или декады.

Использование JK-устройств в составе цифровых счетчиков – это их основная область применения. Цифровые схемы в современной технике собираются на основе микросхем программируемой логики (FPGA) или заказных микросхем (ASIC).

Еще одна область применения JK-триггеров — устройства для обнаружения коротких импульсов. В данном случае импульс после поступления на вход С переходит в единичное состояние, которое затем обнаруживается последующей схемой, например, микропроцессором. Подобно схеме обнаружения КИ работает и схема ждущего мультивибратора.

При создании сложных логических схем нужны приборы разных видов. Поэтому выгоднее использовать универсальный тип устройства, которое может работать в различных режимах. Именно такими устройствами являются JK-триггеры.

Логические микросхемы. Часть 9. JK триггер

Рассказ о JK триггере и несложных опытах для изучения его работы.

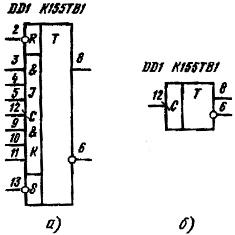

В предыдущих частях статьи было рассказано о триггерах типа RS и D. Этот рассказ будет неполным, если не упомянуть JK триггер. Также как и D триггер он имеет расширенную входную логику. В серии 155 это микросхема К155ТВ1 выпускающаяся в корпусе DIP-14. Ее цоколевка, или как теперь говорят, распиновка (от английского PIN - вывод) показана на рисунке 1а. Зарубежные аналоги SN7472N, SN7472J.

Если, какой-либо вывод в конкретной схеме не используется, то вполне допустимо просто его не показывать, как показано на рисунке 1б.

Описание и назначение выводов

Триггер К155ТВ1 имеет прямой и инверсный выходы. На рисунке это соответственно выводы 8 и 6. Назначение их такое же, как и у ранее рассмотренных триггеров типа D и RS. Инверсный выход начинается маленьким кружочком.

По входам R и S триггер работает так же, как простой RS триггер. Рабочим для этих входов является низкий уровень, что показано кружочками у основания выводов. Как и у D – триггера эти входы являются приоритетными: появление и удержание на каком либо из них низкого уровня запрещает работу остальных входов, а короткий отрицательный импульс переведет триггер в соответствующее состояние вплоть до следующего импульса на входе C.

Рисунок 1. Цоколевка микросхемы К155ТВ1.

J и K - управляющие входы триггера. Они объединены по схеме 3И, что на условном графическом обозначении показано знаком & - логическое И. Достаточно часто в схемах эти входы просто соединяются вместе, получается как будто по одному J и по одному K входу. В некоторых сериях микросхем также имеются JK триггеры, они также называются ТВ1, но в отличие от 155 серии, имеют по одному J и K входу. Логика работы по этим входам совершенно такая же как, и у К155ТВ1, только не надо собирать воедино 3 логических сигнала высокого уровня. Примером таких микросхем могут служить, например, К176ТВ1, К561ТВ1, К1564ТВ1.

Изучение логики работы JK триггера

Чтобы более подробно познакомиться с работой JK триггера, надо просто включить его, как в предыдущей статье, на макетной плате и вручную подать входные сигналы. Ведь, согласитесь, что можно наизусть выучить самоучитель игры на гитаре или баяне, но, не взяв инструмент в руки, играть не научишься. Также и в случае с микросхемами: пока не проведешь простейших опытов, понять смысл работы будет тяжело.

В качестве входных сигналов, так же, как при изучении D триггера, будем использовать проволочную перемычку, соединенную с общим проводом.

Схема для испытания JK триггера К155ТВ1 показана на рисунке 2.

Рисунок 2. Испытания JK триггера К155ТВ1.

Напряжение питания подается как обычно на 14 и 7 выводы микросхемы, что обозначено на схеме в виде проводников со стрелками.

Для визуального наблюдения за состоянием триггера к его выходам, прямому и инверсному, подсоединены светодиодные индикаторы. Такой же индикатор подключен к входу C. Свечение светодиода указывает наличие на данном выходе уровня логической единицы (2,4…5В). На входе C будет индицироваться уровень выходного сигнала генератора импульсов, подключенного к входу C. Конечно, состояние входов и выходов при такой низкой частоте вполне возможно наблюдать с помощью обыкновенного вольтметра, но это не очень удобно.

Работа JK триггера по RS – входам

Хотя схема получилась очень простая перед включением, как обычно, следует проверить ее на отсутствие ошибок, коротких замыканий и обрывов: даже простое включение питания в обратном направлении может привести микросхему у негодность. Это правило следует запомнить и применять его во всех подобных случаях, даже если это просто электрическая схема без полупроводниковых приборов.

Итак включаем. При первом включении обязательно должен зажечься один из светодиодов на выходе, какой неизвестно. Это обусловлено переходными процессами при включении. Теперь будем подавать низкий логический уровень, пользуясь вышеупомянутой проволочной перемычкой, поочередно на R и S входы. При этом светодиоды на выходе должны поочередно переключаться, индицируя состояние триггера. Такой режим работы называется асинхронным – он не требует дополнительных стробирующих (разрешающих, тактирующих) сигналов.

Подавать одновременно низкий уровень сразу на R и S входы не следует: такое состояние для триггера считается запрещенным. Хотя к необратимым последствиям в виде выхода микросхемы из строя не приведет, состояние выходов в таком случае будет неизвестным, не отвечающим логике работы триггера. Если все нормально, то можно перейти к опытам по изучению работы триггера по JK – входам.

Что произойдет, если с помощью проволочной перемычки подавать низкий уровень на JK входы? Ровным счетом ничего: триггер будет хранить предыдущее состояние, что будет видно по свечению индикаторов. Для того, чтобы эти входы могли влиять на состояние триггера, необходимо на вход C подать импульсы от генератора, схема которого показана на рисунке 3. Для его сборки понадобится дополнительная микросхема К155ЛА3. Частота следования и длительность импульсов должна быть такова, чтобы было возможно визуальное наблюдение за состояниями триггера.

Рисунок 3. Генератор тактовых импульсов.

Работа JK триггера в счетном режиме

Если JK входы соединить, как показано на рисунке 2а, то триггер будет работать в счетном режиме: состояние триггера будет изменяться с каждым входным импульсом. Резистор R4 показан на схеме пунктиром – его можно и не ставить, ведь неподключенные входы все равно находятся в состоянии логической единицы. Главным назначением этого резистора является защита от помех через входы JK.

Временная диаграмма работы JK триггера показана на рисунке 2б, и она очень похожа на подобную диаграмму для D – триггера. Основное отличие состоит в том, что изменение состояния триггера происходит не по положительному перепаду уровня на входе C, а по отрицательному – переходу уровня входного импульса из высокого уровня в низкий.

Нетрудно заметить, что частота импульсов на выходе триггера ровно в два раза ниже, чем частота входных импульсов. Поэтому триггеры в счетном режиме часто используются как делители частоты на два. Два триггера включенные последовательно разделят частоту на четыре, а три триггера уже на восемь и так далее по степени числа 2.

Если требуется делитель частоты с нечетным коэффициентом деления, то используются несколько триггеров с обратными связями, но об этом будет рассказано в следующей части статьи о счетчиках и формирователях импульсов.

Из сказанного можно сделать вывод: если JK входы одновременно находятся в состоянии логической единицы (высокого уровня), триггер работает в счетном режиме. Это значит, что по каждому отрицательному перепаду уровня на входе C состояние триггера меняется на противоположное.

Работа триггера по JK – входам

Что произойдет, если на входах JK одновременно будет присутствовать уровень логического нуля? Чтобы это проверить, достаточно хотя бы по одному JK входу (напомним, что К155ТВ1 имеет по 3 J и 3 K входа, объединенных по схеме 3И) замкнуть на общий провод. Но можно соединить с общим проводом и все входы JK, это уже непринципиально. По светодиодным индикаторам увидим, что тактовые импульсы приходят, а состояние триггера не меняется. В состоянии, когда на J и K входах логический нуль, JK – триггер находится в режиме хранения информации.

Осталось рассмотреть два случая. Случай первый – когда на входе J высокий уровень, а на входе K низкий. В этой ситуации триггер по входу C установится в единичное состояние – светится индикатор HL3, присоединенный к прямому выходу триггера. HL2, конечно же, погашен.

Если состояние JK входов в дальнейшем не изменится, то каждый импульс на входе C также будет стремиться установить триггер в единичное состояние, хотя он уже в нем находится. В таком случае говорят, что по входу C просто подтверждается предыдущее состояние триггера в данном случае единичное.

Второй случай, когда на J входе нуль, а на входе K единица. При таком состоянии на JK входах первым же импульсом на входе C триггер установится в нуль (сбросится) – погаснет индикатор HL3 и включится HL2. Если состояние JK входов меняться не будет, то по входу C также происходит подтверждение состояния, как было написано выше, только на этот раз нулевого.

Итак, чтобы было проще запомнить, подведем итог: две единицы на входах JK это счетный режим. Подразумевается, что выполнено условие 3И для JK входов: единица на всех трех входах J, а также единица и на всех трех входах K.

Два нуля на JK входах – режим хранения информации: импульсы на входе C состояния триггера изменить не смогут. Для получения такого состояния достаточно, чтобы хотя бы на одном входе J И хотя бы на одном входе K был уровень логического нуля.

В случае, когда на всех трех J – входах высокий уровень, триггер устанавливается в единичное состояние. При этом хотя бы на одном из 3 входов K должен присутствовать низкий уровень.

Чтобы сбросить триггер, нуль должен присутствовать хотя бы на одном из входов J, а на всех трех входах K должна удерживаться единица.

Все, что было написано выше, можно посмотреть в таблице истинности для триггера К155ТВ1, которая показана на рисунке 4.

Рисунок 4. Таблица истинности для микросхемы К155ТВ1.

Триггеры различных типов применяются также в качестве элементов счетных устройств, или просто счетчиков, а также в качестве формирователей импульсов. Об этом будет рассказано в следующей части статьи о логических микросхемах.

Триггер – элемент цифровой техники, бистабильное устройство, которое переключается в одно из состояний и может находиться в нем бесконечно долго даже при снятии внешних сигналов. Он строится из логических элементов первого уровня (И-НЕ, ИЛИ-НЕ и т.д.) и относится к логическим устройствам второго уровня.

На практике триггеры выпускаются в виде микросхем в отдельном корпусе или входят в качестве элементов в состав больших интегральных схем (БИС) или программируемых логических матриц (ПЛМ).

Классификация и типы синхронизации триггеров

Триггеры делятся на два больших класса:

Принципиальное различие между ними в том, что у первой категории устройств уровень выходного сигнала меняется одновременно с изменением сигнала на входе (входах). У синхронных триггеров изменение состояния происходит только при наличии сихронизирующего (тактового, стробирующего) сигнала на предусмотренном для этого входе. Для этого предусмотрен специальный вывод, обозначаемый буквой С (clock). По виду стробирования синхронные элементы делятся на два класса:

У первого типа уровень выхода меняется в зависимости от конфигурации входных сигналов в момент появления фронта (переднего края) или спада тактового импульса (зависит от конкретного вида триггера). Между появлением синхронизирующих фронтов (спадов) на входы можно подавать любые сигналы, состояние триггера не изменится. У второго варианта признаком тактирования является не изменение уровня, а наличие единицы или нуля на входе Clock. Также существуют сложные триггерные устройства, классифицируемые по:

- числу устойчивых состояний (3 и более, в отличие от 2 у основных элементов);

- числу уровней (также более 3);

- другим характеристикам.

Сложные элементы имеет ограниченное применение в специфических устройствах.

Типы триггеров и принцип их работы

Существует несколько основных типов триггеров. Перед тем, как разобраться в различиях, следует отметить общее свойство: при подаче питания выход любого устройства устанавливается в произвольное состояние. Если это критично для общей работы схемы, надо предусматривать цепи предустановки. В простейшем случае это RC-цепочка, которая формирует сигнал установки начального состояния.

RS-триггеры

Самый распространенный тип асинхронного бистабильного устройства – RS-триггер. Он относится к триггерам с раздельной установкой состояния 0 и 1. Для этого имеется два входа:

Имеется прямой выход Q, также может быть инверсный выход Q1. Логический уровень на нём всегда противоположен уровню на Q – это бывает удобно при разработке схем.

При подаче положительного уровня на вход S на выходе Q установится логическая единица (если есть инверсный выход, он перейдет на уровень 0). После этого на входе установки сигнал может меняться как угодно – на выходной уровень это не повлияет. До тех пор, пока единица не появится на входе R. Это установит триггер в состояние 0 (1 на инверсном выводе). Теперь изменение сигнала на входе сброса никак не повлияет на дальнейшее состояние элемента.

Важно! Вариант, когда на обоих входах присутствует логическая единица, является запретным. Триггер установится в произвольное состояние. При разработке схем такой ситуации надо избегать.

RS-триггер можно построить на основе широко распространенных двухвходовых элементов И-НЕ. Такой способ реализуем как на обычных микросхемах, так и внутри программируемых матриц.

Один или оба входа могут быть инверсными. Это означает, что по этим выводам триггер управляется появлением не высокого, а низкого уровня.

Если построить RS-триггер на двухвходовых элементах И-НЕ, то оба входа будут инверсными – управляться подачей логического нуля.

Существует стробируемый вариант RS-триггера. У него имеется дополнительный вход С. Переключение происходит при выполнении двух условий:

- присутствие высокого уровня на входе Set или Reset;

- наличие тактового сигнала.

Такой элемент применяют в случаях, когда переключение надо задержать, например, на время окончания переходных процессов.

D-триггеры

Пока на входе для синхронизации присутствует логическая единица, сигнал на выходе Q повторяет сигнал на входе данных (режим прозрачности). Как только уровень строба перейдет в состояние 0, на выходе Q уровень останется тем же, что был в момент перепада (защелкнется). Так можно зафиксировать входной уровень на входе в любой момент времени. Также существуют D-триггеры с тактированием по фронту. Они защёлкивают сигнал по положительному перепаду строба.

На практике в одной микросхеме могут объединять два типа бистабильных устройств. Например, D и RS-триггер. В этом случае входы Set/Reset являются приоритетными. Если на них присутствует логический ноль, то элемент ведёт себя как обычный D-триггер. При появлении хотя бы на одном входе высокого уровня, выход устанавливается в 0 или 1 независимо от сигналов на входах С и D.

T-триггеры

T-триггер относится к классу счётных бистабильных элементов. Логика его работы проста – он изменяет своё состояние каждый раз, когда на его вход приходит очередная логическая единица. Если на вход подать импульсный сигнал, выходная частота будет в два раза выше входной. На инверсном выходе сигнал будет противофазен прямому.

Так работает асинхронный Т-триггер. Также существует синхронный вариант. При подаче импульсного сигнала на тактирующий вход и при наличии логической единицы на выводе T, элемент ведёт себя так же, как и асинхронный – делит входную частоту пополам. Если на выводе Т логический ноль, то выход Q устанавливается в низкий уровень независимо от наличия стробов.

![Схема работы синхронного T-триггера.]()

JK-триггеры

Этот бистабильный элемент относится к категории универсальных. Он может управляться раздельно по входам. Логика работы JK-триггера похожа на работу RS-элемента. Для установки выхода в единицу используется вход J (Job). Появление высокого уровня на выводе K (Keep) сбрасывает выход в ноль. Принципиальным отличием от RS-триггера является то, что одновременное появление единиц на двух управляющих входах не является запретным. В этом случае выход элемента меняет свое состояние на противоположное.

Если выходы Job и Keep соединить, то JK-триггер превращается в асинхронный счётный Т-триггер. Когда на объединённый вход подаётся меандр, на выходе будет в два раза меньшая частота. Как и у RS-элемента, существует тактируемый вариант JK-триггера. На практике применяются, в основном, именно стробируемые элементы такого типа.

Практическое использование

Свойство триггеров сохранять записанную информацию даже при снятии внешних сигналов позволяет применять их в качестве ячеек памяти ёмкостью в 1 бит. Из единичных элементов можно построить матрицу для запоминания двоичных состояний – по такому принципу строятся статические оперативные запоминающие устройства (SRAM). Особенностью такой памяти является простая схемотехника, не требующая дополнительных контроллеров. Поэтому такие SRAM применяются в контроллерах и ПЛМ. Но невысокая плотность записи препятствует использованию таких матриц в ПК и других мощных вычислительных системах.

Выше упоминалось использование триггеров в качестве делителей частоты. Бистабильные элементы можно соединять в цепочки и получать различные коэффициенты деления. Та же цепочка может быть использована в качестве счетчика импульсов. Для этого надо считывать с промежуточных элементов состояние выходов в каждый момент времени – получится двоичный код, соответствующий количеству пришедших на вход первого элемента импульсов.

В зависимости от типа примененных триггеров, счетчики могут быть синхронными и асинхронными. По такому же принципу строятся преобразователи последовательного кода в параллельный, но здесь используются только стробируемые элементы. Также на триггерах строятся цифровые линии задержки и другие элементы двоичной техники.

RS-триггеры используются в качестве фиксаторов уровня (подавителей дребезга контактов). Если в качестве источников логического уровня применяются механические коммутаторы (кнопки, переключатели), то при нажатии эффект дребезга сформирует множество сигналов место одного. RS-триггер с этим успешно борется.

Область применения бистабильных устройств широка. Круг решаемых с их помощью задач во многом зависит от фантазии конструктора, особенно в сфере нетиповых решений.

Что такое компаратор напряжения и для чего он нужен

Режимы работы, описание характеристик и назначение выводов микросхемы NE555

Что такое операционный усилитель?

Что такое термистор, их разновидности, принцип работы и способы проверки на работоспособность

Читайте также: