Кэш память реферат презентация

Обновлено: 02.07.2024

Презентация на тему: " Кэш - память. Кэш-память это высокоскоростная память произвольного доступа, используемая процессором компьютера для временного хранения информации." — Транскрипт:

2 Кэш-память это высокоскоростная память произвольного доступа, используемая процессором компьютера для временного хранения информации.

3 Кэш - память : имеет небольшой объем; размещается непосредственно на процессорном кристалле; скорость работы гораздо выше, чем у динамической памяти (модули ОЗУ), но ниже, чем работают регистры общего назначения (РОН) центрального процессора. Основное достоинство быстродействие. Основной недостаток большой физический объем, занимаемый памятью и высокое энергопотребление.

4 Система кэш - памяти AMD на процессоре K6-III (L1 = 64 Kb, L2 = 256 Kb). кэш первого уровня (L1) память на кристалле кэш второго уровня (L2) память на материнской плате

5 кэш - архитектуры инклюзивная эксклюзивная

6 Инклюзивная кэш - память Дублирование информации, находящейся в L1 и L2. Применяется в тех системах, где разница в объемах кэшей первого и второго уровня велика. Например, Pentium 3 (Coppermine): L1 = 16 Kb, L2 = 256 Kb; Pentium 4: L1 = 16 Kb, L2 = 1024 Kb.

7 Эксклюзивная кэш - память Уникальность информации, находящейся в L1 и L2. Применяется в системах, где разность между объемами кэшей первого и второго уровня относительно невелика. Например, Athlon XP: L1 = 64 Kb, L2 = 256 Kb.

8 Схемы взаимодействия кэш - памяти и основной оперативной памяти

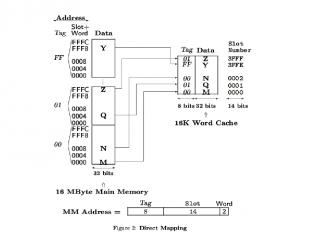

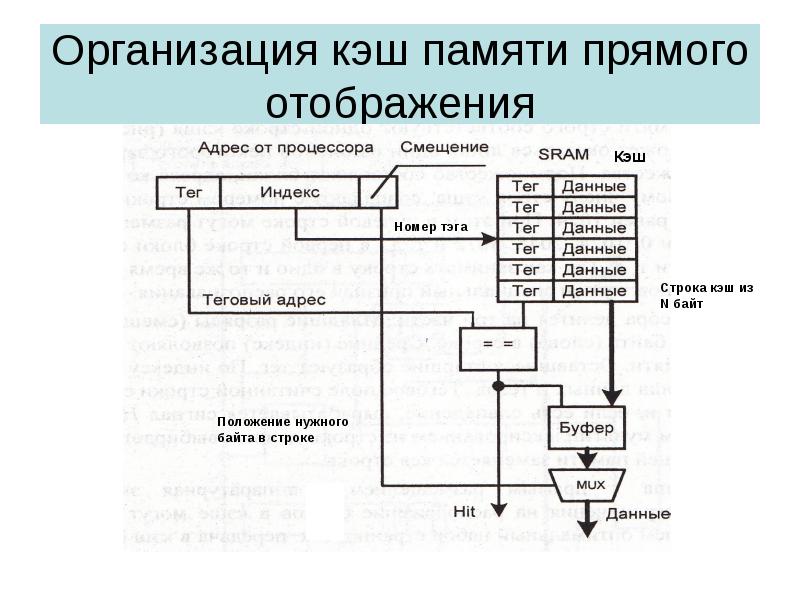

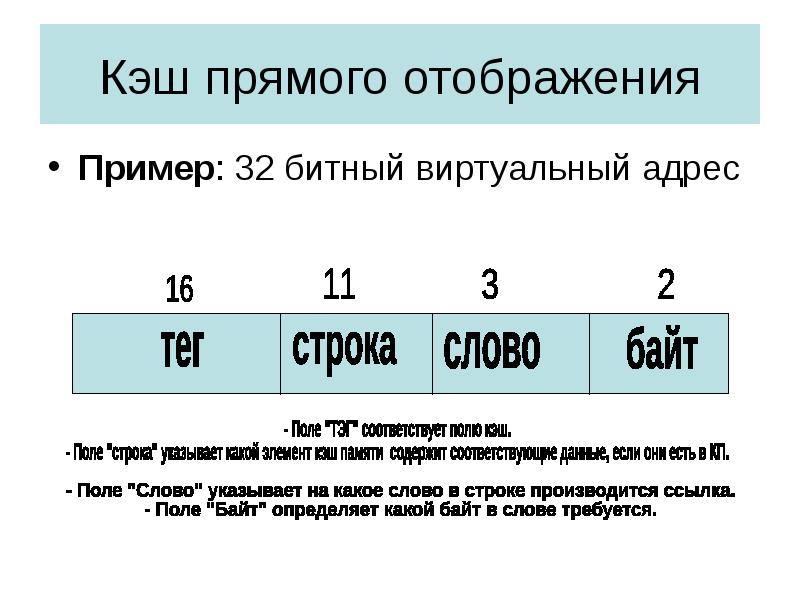

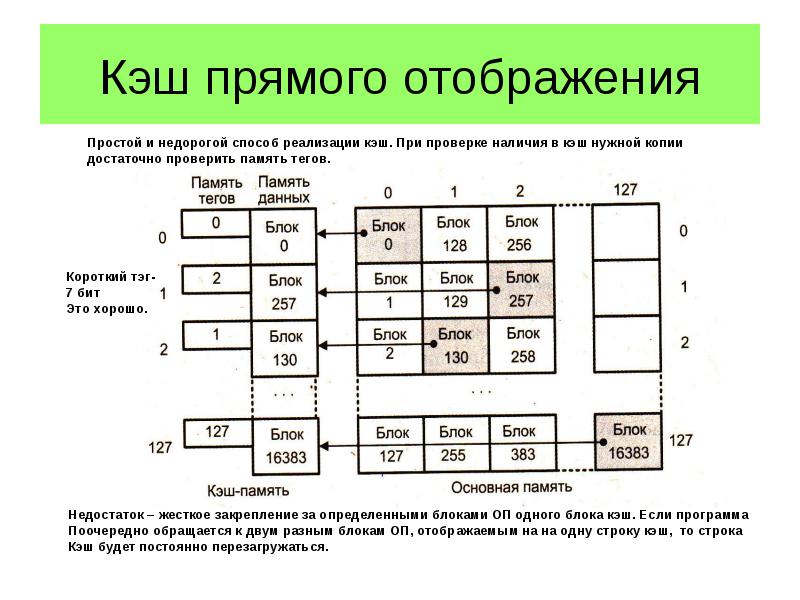

9 Кэш - память с прямым отображением Самый простой вариант взаимодействия кэша с ОЗУ. Объем ОЗУ делится на сегменты (страницы), по объему равные объему всего кэша (например, при объеме кэша 64 Кб и ОЗУ разбивается на страницы по 64 Кб). При взаимодействии кэша с ОЗУ, одна страница ОЗУ размещается в кэш-памяти, начиная с нулевого адреса (т.е., с самого начала кэша). При повторной операции взаимодействия, следующая страница накладывается поверх существующей - т.е., фактически прежние данные заменяются на текущие.

10 Кэш - память с прямым отображением Достоинства: простая организация массива, минимальное время поиска. Недостатки: неэффективное использование всего объема кэш- памяти.

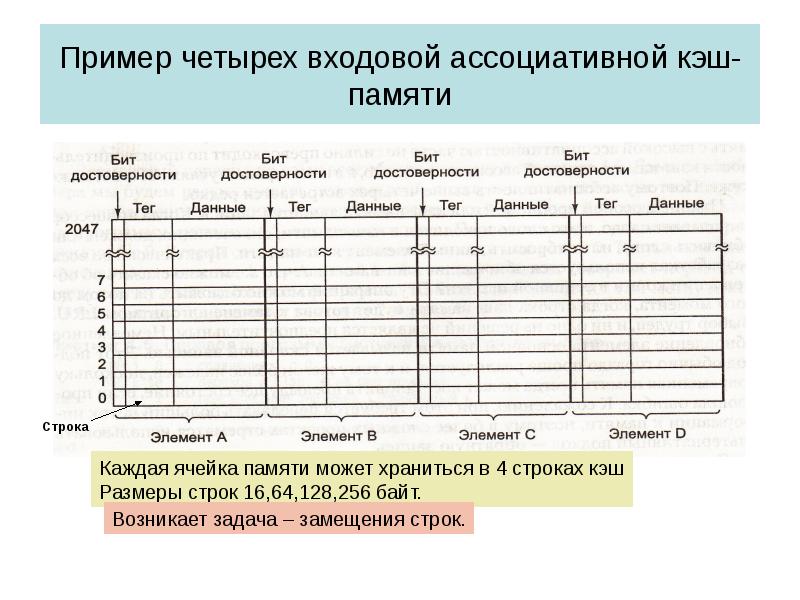

12 Наборно - ассоциативная кэш - память Достоинства: повышается эффективность использования всего объема кэша - чем больше кэш-банков, тем выше эффективность. Недостатки: более сложная схема управления работой кэша; дополнительное время на анализ информации.

13 Ассоциативная кэш - память Объем кэш-банка становится равным одной строке кэш-памяти. При этом любая строка ОЗУ может быть сохранена в любом месте кэш-памяти. Запоминающий кэш-массив состоит из строк равной длины. Емкость такой строки равна размеру пакета, считываемого из ОЗУ за 1 цикл (например, Pentium байта; Pentium байта). Строка загружается в кэш и извлекается только целиком.

14 Ассоциативная кэш - память Достоинства: максимальная эффективность использования пространства кэш-памяти. Недостатки: наибольшие затраты времени на поиск информации.

15 Некоторые данные по популярным процессорам от Intel и AMD: Pentium III Процессор содержит 32 Kб неблокируемой кэш-памяти первого уровня (16Кб/16Кб) и унифицированную неблокируемую кэш-память второго уровня емкостью 512 Кб, функционирующую на вдвое меньшей частоте, чем ядро.

16 Pentium IV ( на ядре Northwood Кбайт кэш- памяти L2). - Механизм ускоренной обработки команд; - Кэш-память первого уровня с отслеживанием исполнения команд; - Кэш-память с улучшенной передачей данных

17 AMD-K6®-III Задействована встроенная быстродействующая кэш-память второго уровня (L2). В процессорный кристалл интегрированной 256 Кб кэш-памяти второго уровня, работающей на полной тактовой частоте процессора. Объем кэш- памяти первого уровня (L1), как у всего семейства K6, равен 64Кб.

18 AMD Athlon Имеет наибольший для платформ x86 кэш L1 (128KB) - в четыре раза превосходящий L1 кэш процессора Pentium III (32KB). Также включает высокоскоростной, 64- битный контроллер кэш памяти второго уровня (L2), поддерживающий объем кэш- памяти второго уровня от 512Kб до 8Mб. В настоящее время процессор AMD Athlon является самым быстрым процессором в мире.

- Для учеников 1-11 классов и дошкольников

- Бесплатные сертификаты учителям и участникам

Описание презентации по отдельным слайдам:

Кэш-память — это высокоскоростная память произвольного доступа, используемая процессором компьютера для временного хранения информации.

Кэш-память: имеет небольшой объем; размещается непосредственно на процессорном кристалле; скорость работы гораздо выше, чем у динамической памяти (модули ОЗУ), но ниже, чем работают регистры общего назначения (РОН) центрального процессора. Основное достоинство быстродействие. Основной недостаток большой физический объем, занимаемый памятью и высокое энергопотребление.

Система кэш-памяти AMD на процессоре K6-III (L1 = 64 Kb, L2 = 256 Kb). кэш первого уровня (L1) память на кристалле кэш второго уровня (L2) память на материнской плате

кэш-архитектуры инклюзивная эксклюзивная

Инклюзивная кэш-память Дублирование информации, находящейся в L1 и L2. Применяется в тех системах, где разница в объемах кэшей первого и второго уровня велика. Например, Pentium 3 (Coppermine): L1 = 16 Kb, L2 = 256 Kb; Pentium 4: L1 = 16 Kb, L2 = 1024 Kb.

Эксклюзивная кэш-память Уникальность информации, находящейся в L1 и L2. Применяется в системах, где разность между объемами кэшей первого и второго уровня относительно невелика. Например, Athlon XP: L1 = 64 Kb, L2 = 256 Kb.

Схемы взаимодействия кэш-памяти и основной оперативной памяти

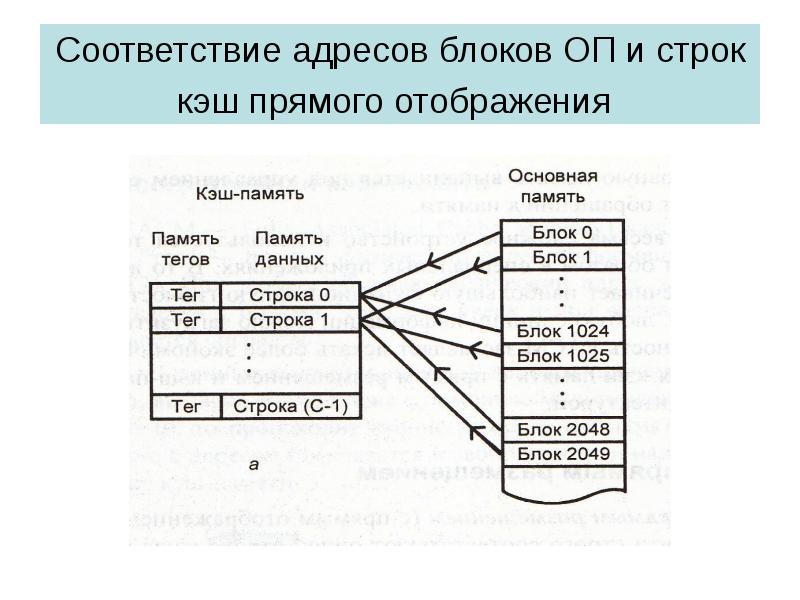

Кэш-память с прямым отображением Самый простой вариант взаимодействия кэша с ОЗУ. Объем ОЗУ делится на сегменты (страницы), по объему равные объему всего кэша (например, при объеме кэша 64 Кб и ОЗУ разбивается на страницы по 64 Кб). При взаимодействии кэша с ОЗУ, одна страница ОЗУ размещается в кэш-памяти, начиная с нулевого адреса (т.е., с самого начала кэша). При повторной операции взаимодействия, следующая страница накладывается поверх существующей - т.е., фактически прежние данные заменяются на текущие.

Кэш-память с прямым отображением Достоинства: простая организация массива, минимальное время поиска. Недостатки: неэффективное использование всего объема кэш-памяти.

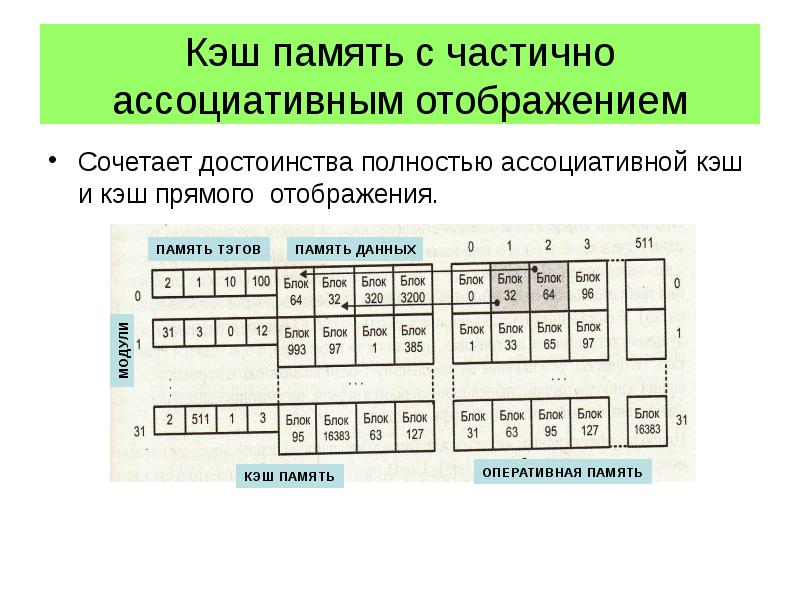

Наборно-ассоциативная кэш-память Достоинства: повышается эффективность использования всего объема кэша - чем больше кэш-банков, тем выше эффективность. Недостатки: более сложная схема управления работой кэша; дополнительное время на анализ информации.

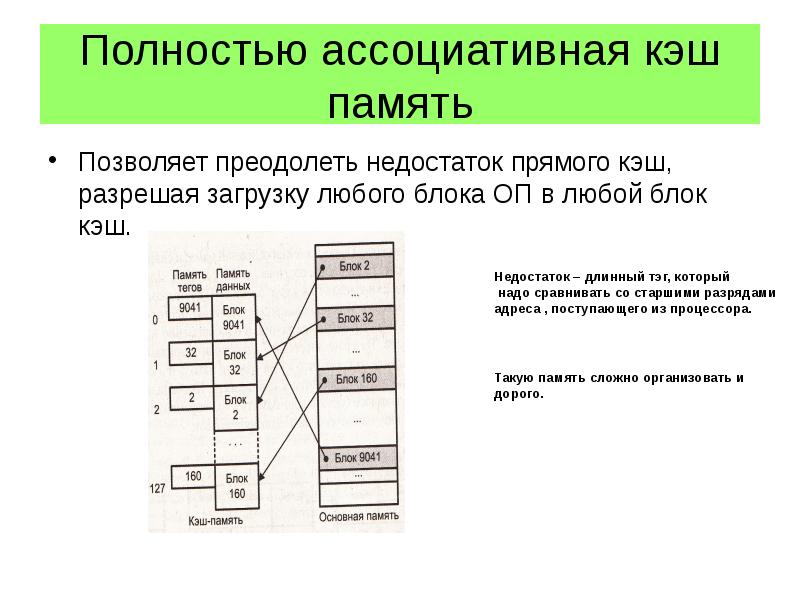

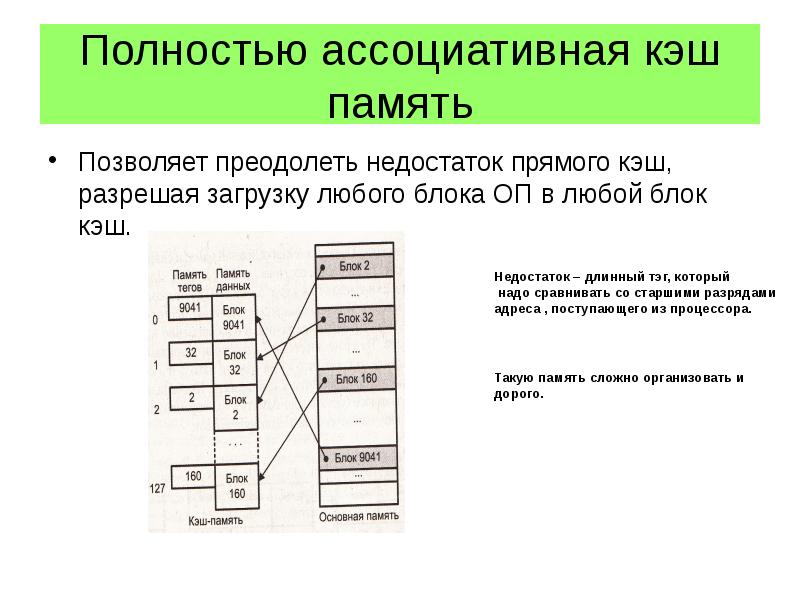

Ассоциативная кэш-память Объем кэш-банка становится равным одной строке кэш-памяти. При этом любая строка ОЗУ может быть сохранена в любом месте кэш-памяти. Запоминающий кэш-массив состоит из строк равной длины. Емкость такой строки равна размеру пакета, считываемого из ОЗУ за 1 цикл (например, Pentium 3 - 32 байта; Pentium 4 - 64 байта). Строка загружается в кэш и извлекается только целиком.

Ассоциативная кэш-память Достоинства: максимальная эффективность использования пространства кэш-памяти. Недостатки: наибольшие затраты времени на поиск информации.

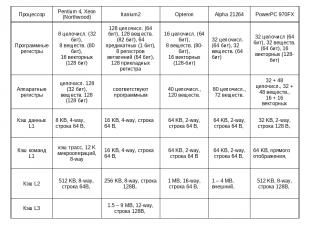

Некоторые данные по популярным процессорам от Intel и AMD: Pentium III Процессор содержит 32 Kб неблокируемой кэш-памяти первого уровня (16Кб/16Кб) и унифицированную неблокируемую кэш-память второго уровня емкостью 512 Кб, функционирующую на вдвое меньшей частоте, чем ядро.

Pentium IV ( на ядре Northwood - 512 Кбайт кэш-памяти L2). - Механизм ускоренной обработки команд; - Кэш-память первого уровня с отслеживанием исполнения команд; - Кэш-память с улучшенной передачей данных

AMD-K6®-III Задействована встроенная быстродействующая кэш-память второго уровня (L2). В процессорный кристалл интегрированно 256 Кб кэш-памяти второго уровня, работающей на полной тактовой частоте процессора. Объем кэш-памяти первого уровня (L1), как у всего семейства K6, равен 64Кб.

AMD Athlon™ Имеет наибольший для платформ x86 кэш L1 (128KB) - в четыре раза превосходящий L1 кэш процессора Pentium III (32KB). Также включает высокоскоростной, 64-битный контроллер кэш памяти второго уровня (L2), поддерживающий объем кэш-памяти второго уровня от 512Kб до 8Mб. В настоящее время процессор AMD Athlon является самым быстрым процессором в мире.

№ слайда 1

№ слайда 2

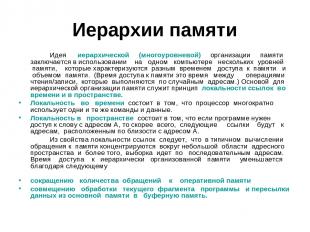

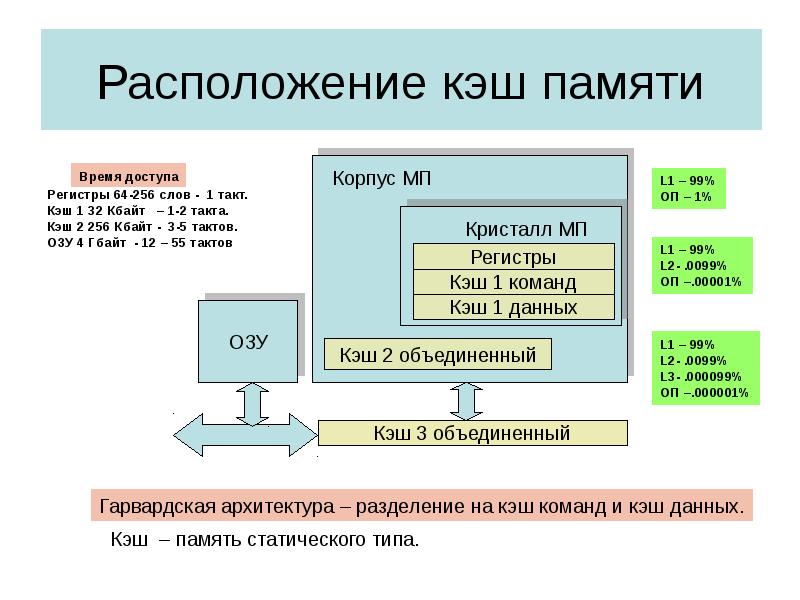

Иерархии памяти Идея иерархической (многоуровневой) организации памяти заключается в использовании на одном компьютере нескольких уровней памяти, которые характеризуются разным временем доступа к памяти и объемом памяти. (Время доступа к памяти это время между операциями чтения/записи, которые выполняются по случайным адресам.) Основой для иерархической организации памяти служит принцип локальности ссылок во времени и в пространстве. Локальность во времени состоит в том, что процессор многократно использует одни и те же команды и данные. Локальность в пространстве состоит в том, что если программе нужен доступ к слову с адресом A, то скорее всего, следующие ссылки будут к адресам, расположенным по близости с адресом A. Из свойства локальности ссылок следует, что в типичном вычислении обращения к памяти концентрируются вокруг небольшой области адресного пространства и более того, выборка идет по последовательным адресам. Время доступа к иерархически организованной памяти уменьшается благодаря следующему сокращению количества обращений к оперативной памяти совмещению обработки текущего фрагмента программы и пересылки данных из основной памяти в буферную память.

№ слайда 3

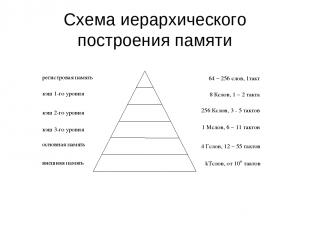

Схема иерархического построения памяти

№ слайда 4

№ слайда 5

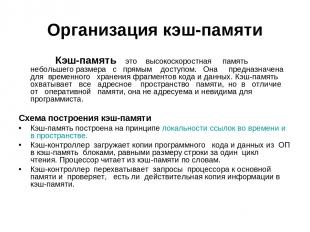

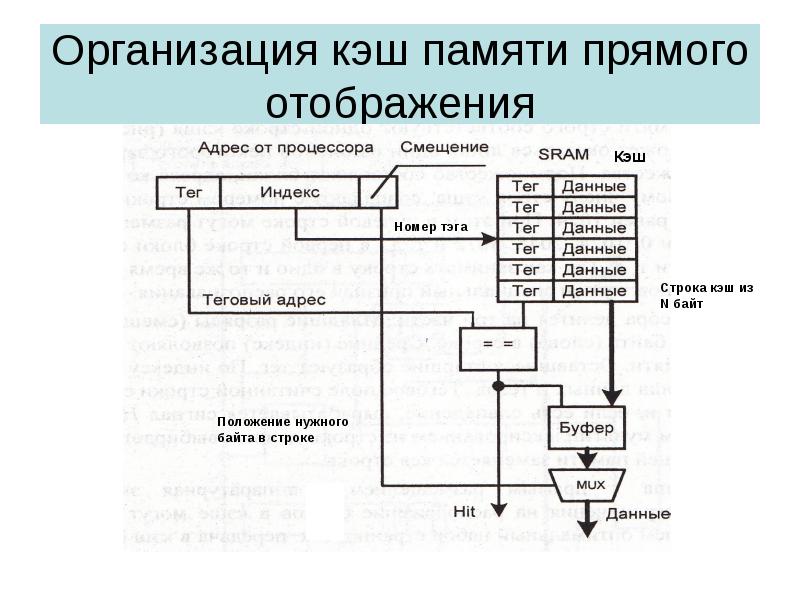

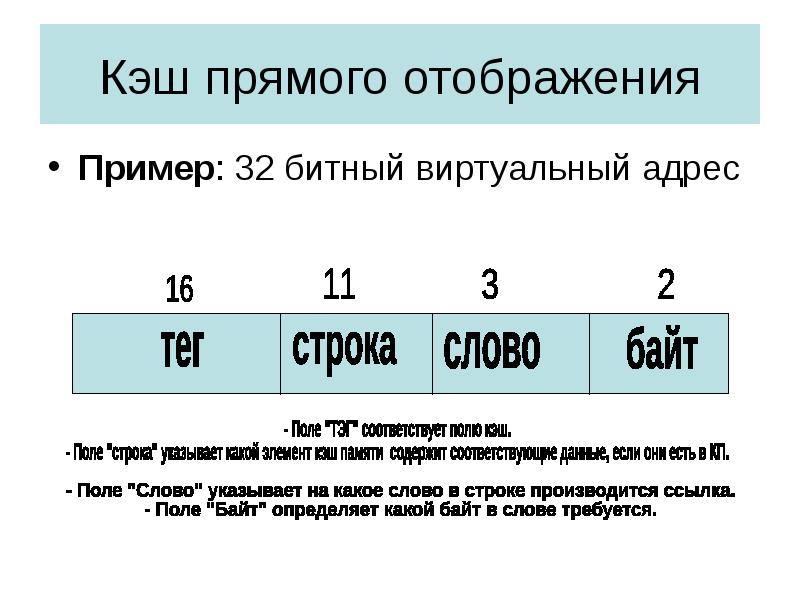

Организация кэш-памяти Кэш-память это высокоскоростная память небольшeго размера с прямым доступом. Она предназначена для временного хранения фрагментов кода и данных. Кэш-память охватывает все адресное пространство памяти, но в отличие от оперативной памяти, она не адресуема и невидима для программиста. Схема построения кэш-памяти Кэш-память построена на принципе локальности ссылок во времени и в пространстве. Кэш-контроллер загружает копии программного кода и данных из ОП в кэш-память блоками, равными размеру строки за один цикл чтения. Процессор читает из кэш-памяти по словам. Кэш-контроллер перехватывает запросы процессора к основной памяти и проверяет, есть ли действительная копия информации в кэш-памяти.

№ слайда 6

№ слайда 7

Схема иерархического построения памяти Оперативная память (RAM) Кэш 3-го уровня (L3) Кэш 2-го уровня (L2) Кэш инструкций 1-го уровня (L1I) Кэш данных 1-го уровня (L1D) Регистры

№ слайда 8

Организация кэш-памяти Когда контроллер помещает данные в кэш- память? Загрузка по требованию (on demand). Спекулятивная загрузка (speculative load). Алгоритм предполагает помещать данные в кэш-память задолго до того, как к ним произойдет реальное обращение. У кэш-контроллера есть несколько алгоритмов, которые указывают, какие ячейки памяти потребуются процессору в ближайшее время.

№ слайда 9

Организация кэш-памяти Когда контроллер выполняет поиск данных в памяти? после фиксации промаха (сквозной просмотр). одновременно с поиском блока в кэш-памяти, в случае кэш-попадания, обращение к оперативной памяти прерывается (отложенный просмотр).

№ слайда 10

Основные вопросы организации кэш-памяти Алгоритм отображения адресов основной памяти в кэш-память. Алгоритм записи данных и команд из кэш-памяти в основную память. Алгоритм замещения строки в кэш-памяти. Размер кэш-памяти. Длина строки в кэш-памяти.

№ слайда 11

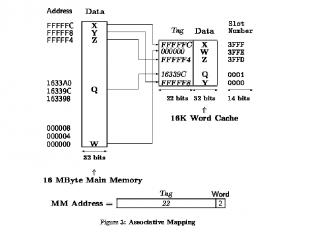

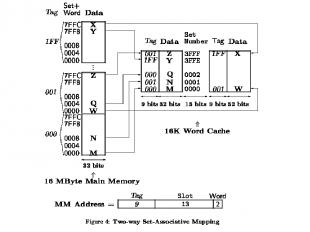

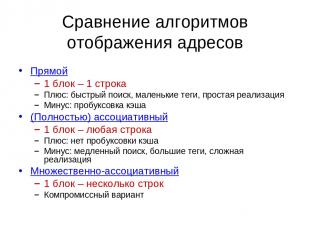

Алгоритмы отображения Прямой (direct mapping). Ассоциативный (full associative mapping). Множественно-ассоциативный (set-associative mapping).

№ слайда 12

№ слайда 14

№ слайда 15

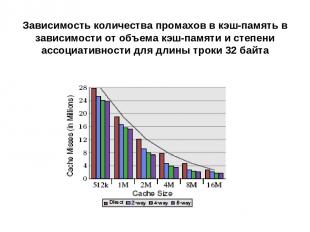

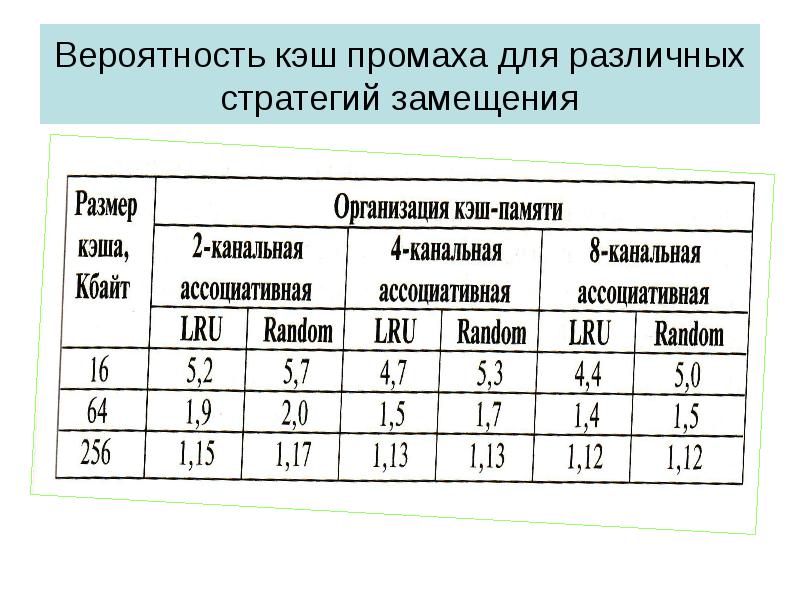

Зависимость количества промахов в кэш-память в зависимости от объема кэш-памяти и степени ассоциативности для длины троки 32 байта

№ слайда 16

№ слайда 17

Сравнение алгоритмов отображения адресов Прямой 1 блок – 1 строка Плюс: быстрый поиск, маленькие теги, простая реализация Минус: пробуксовка кэша (Полностью) ассоциативный 1 блок – любая строка Плюс: нет пробуксовки кэша Минус: медленный поиск, большие теги, сложная реализация Множественно-ассоциативный 1 блок – несколько строк Компромиссный вариант

№ слайда 18

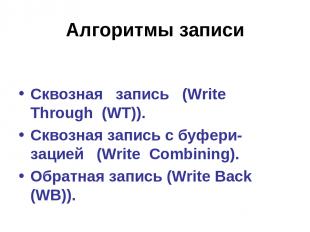

Алгоритмы записи Сквозная запись (Write Through (WT)). Сквозная запись с буфери-зацией (Write Combining). Обратная запись (Write Back (WB)).

№ слайда 19

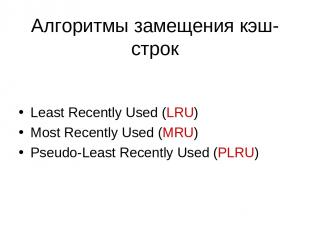

Алгоритмы замещения кэш-строк Least Recently Used (LRU) Most Recently Used (MRU) Pseudo-Least Recently Used (PLRU)

№ слайда 20

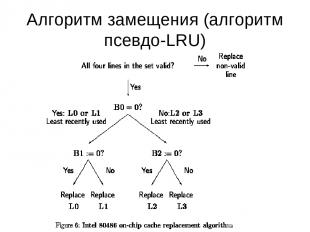

Алгоритм замещения (алгоритм псевдо-LRU)

№ слайда 21

№ слайда 22

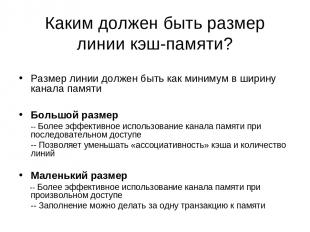

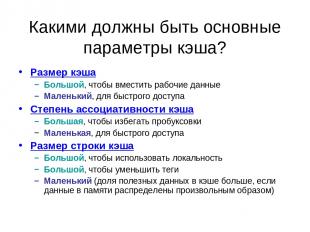

Какими должны быть основные параметры кэша? Размер кэша Большой, чтобы вместить рабочие данные Маленький, для быстрого доступа Степень ассоциативности кэша Большая, чтобы избегать пробуксовки Маленькая, для быстрого доступа Размер строки кэша Большой, чтобы использовать локальность Большой, чтобы уменьшить теги Маленький (доля полезных данных в кэше больше, если данные в памяти распределены произвольным образом)

№ слайда 23

№ слайда 24

Эффективное использование иерархии памяти Объем обрабатываемых данных Обход данных

Схема иерархической памяти int prog() < . . . . for (i…) for (j…) . . > Программа: Оперативная память (медленная) Кэш-память (быстрая) Регистры (сверхбыстрая память) 2 Гб L1: 64Кб L2: 2Мб 32 целочисл. 32 веществ.

№ слайда 26

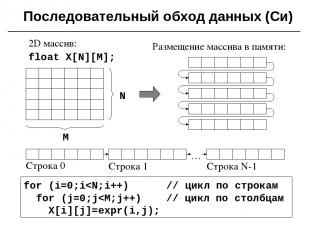

Последовательный обход данных (Си) 2D массив: Размещение массива в памяти: float X[N][M]; for (i=0;i

№ слайда 27

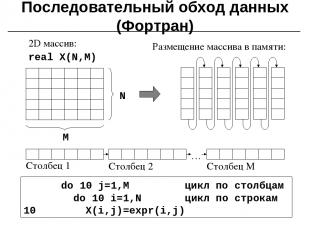

Последовательный обход данных (Фортран) 2D массив: Размещение массива в памяти: real X(N,M) do 10 j=1,M цикл по столбцам do 10 i=1,N цикл по строкам 10 X(i,j)=expr(i,j)

![Пример обхода данных Перемножение матриц: C[Nx][Nz]=A[Nx][Ny]*B[Ny][Nz] for(i=0;](https://fs3.ppt4web.ru/images/132016/202557/310/img27.jpg)

№ слайда 28

Пример обхода данных Перемножение матриц: C[Nx][Nz]=A[Nx][Ny]*B[Ny][Nz] for(i=0;i

№ слайда 29

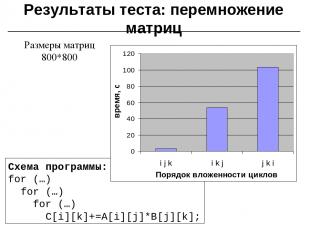

Результаты теста: перемножение матриц Размеры матриц 800*800 Схема программы: for (…) for (…) for (…) C[i][k]+=A[i][j]*B[j][k];

№ слайда 33

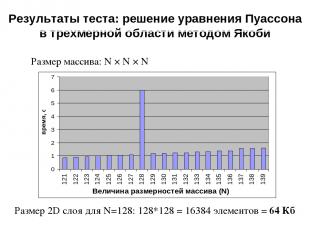

Результаты теста: решение уравнения Пуассона в трехмерной области методом Якоби Размер 2D слоя для N=128: 128*128 = 16384 элементов = 64 Кб Размер массива: N × N × N

№ слайда 34

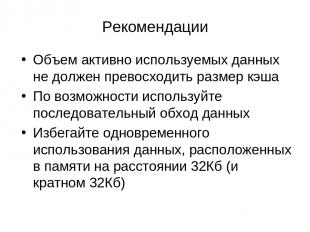

Рекомендации Объем активно используемых данных не должен превосходить размер кэша По возможности используйте последовательный обход данных Избегайте одновременного использования данных, расположенных в памяти на расстоянии 32Кб (и кратном 32Кб)

№ слайда 35

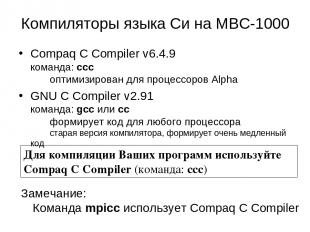

Компиляторы языка Си на МВС-1000 Compaq C Compiler v6.4.9 команда: ccc оптимизирован для процессоров Alpha GNU C Compiler v2.91 команда: gcc или cc формирует код для любого процессора старая версия компилятора, формирует очень медленный код Замечание: Команда mpicc использует Compaq C Compiler Для компиляции Ваших программ используйте Compaq C Compiler (команда: ссс)

№ слайда 36

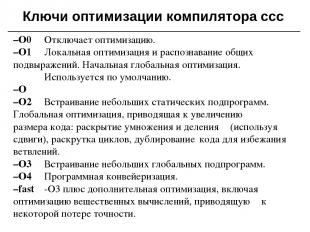

Ключи оптимизации компилятора ccc –O0 Отключает оптимизацию. –O1 Локальная оптимизация и распознавание общих подвыражений. Начальная глобальная оптимизация. Используется по умолчанию. –O –O2 Встраивание небольших статических подпрограмм. Глобальная оптимизация, приводящая к увеличению размера кода: раскрытие умножения и деления (используя сдвиги), раскрутка циклов, дублирование кода для избежания ветвлений. –O3 Встраивание небольших глобальных подпрограмм. –O4 Программная конвейеризация. –fast -O3 плюс дополнительная оптимизация, включая оптимизацию вещественных вычислений, приводящую к некоторой потере точности.

№ слайда 37

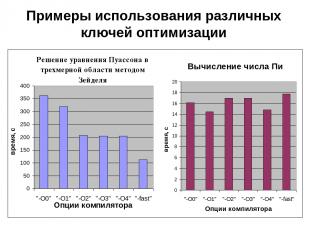

Примеры использования различных ключей оптимизации

№ слайда 38

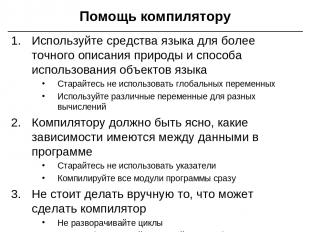

Помощь компилятору Используйте средства языка для более точного описания природы и способа использования объектов языка Старайтесь не использовать глобальных переменных Используйте различные переменные для разных вычислений Компилятору должно быть ясно, какие зависимости имеются между данными в программе Старайтесь не использовать указатели Компилируйте все модули программы сразу Не стоит делать вручную то, что может сделать компилятор Не разворачивайте циклы Пишите более ясный и простой код, особенно внутри циклов

№ слайда 39

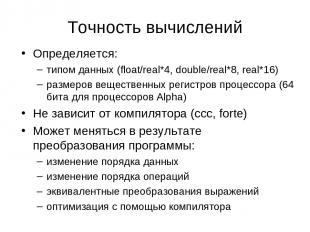

Точность вычислений Определяется: типом данных (float/real*4, double/real*8, real*16) размеров вещественных регистров процессора (64 бита для процессоров Alpha) Не зависит от компилятора (ccc, forte) Может меняться в результате преобразования программы: изменение порядка данных изменение порядка операций эквивалентные преобразования выражений оптимизация с помощью компилятора

Слайд 1

Кэш память Цель лекции: рассмотреть назначение, принципы построения кэш-памяти, особенности ее использования в мультипроцессорных системах

Слайд 3

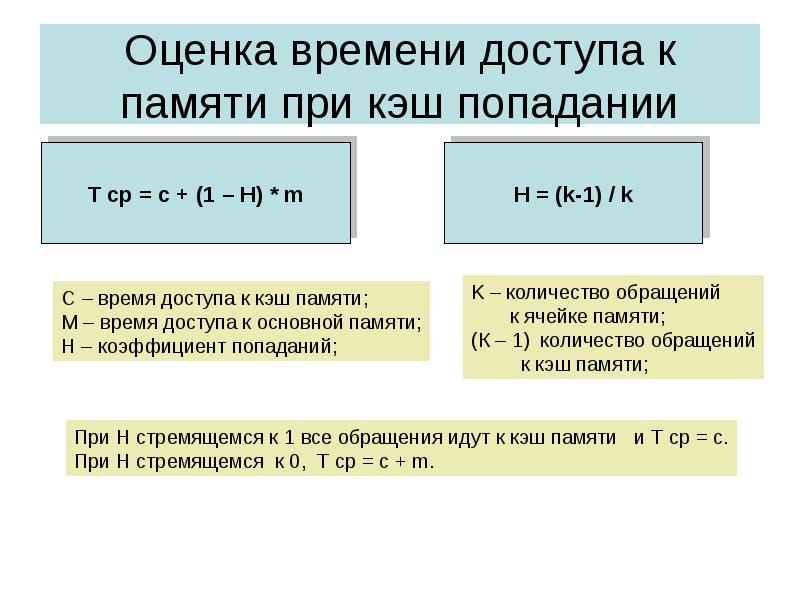

Слайд 4

Слайд 5

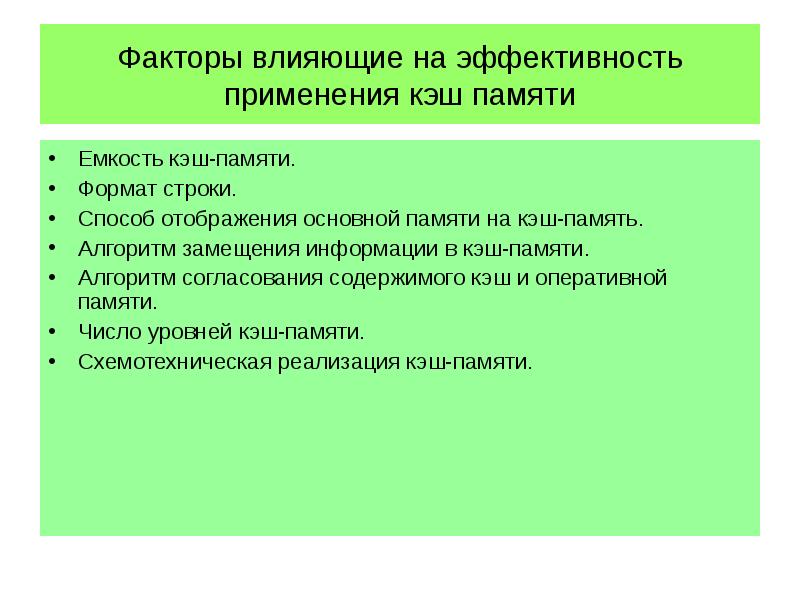

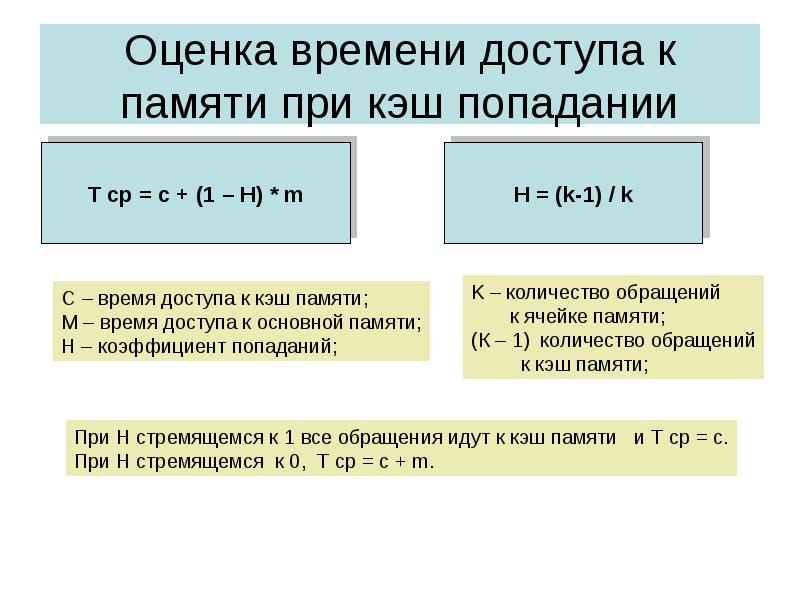

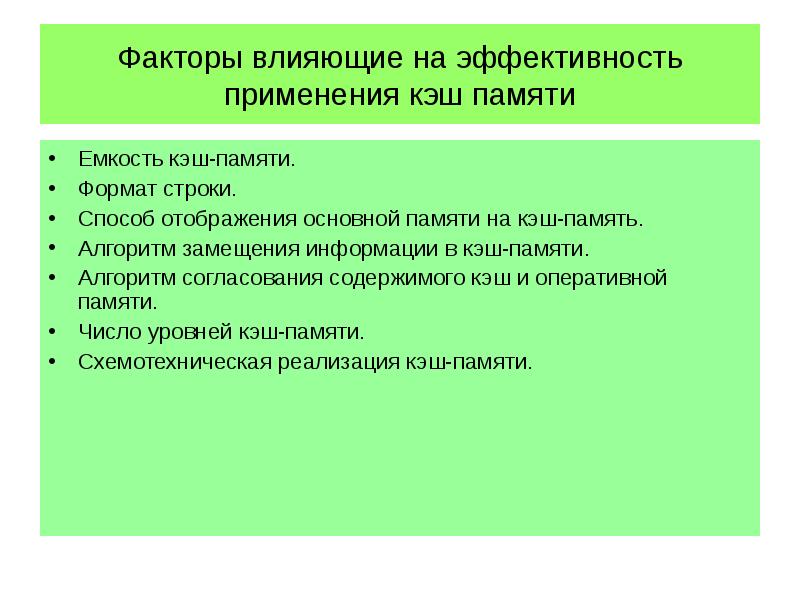

Факторы влияющие на эффективность применения кэш памяти Емкость кэш-памяти. Формат строки. Способ отображения основной памяти на кэш-память. Алгоритм замещения информации в кэш-памяти. Алгоритм согласования содержимого кэш и оперативной памяти. Число уровней кэш-памяти. Схемотехническая реализация кэш-памяти.

Слайд 6

Слайд 7

Слайд 8

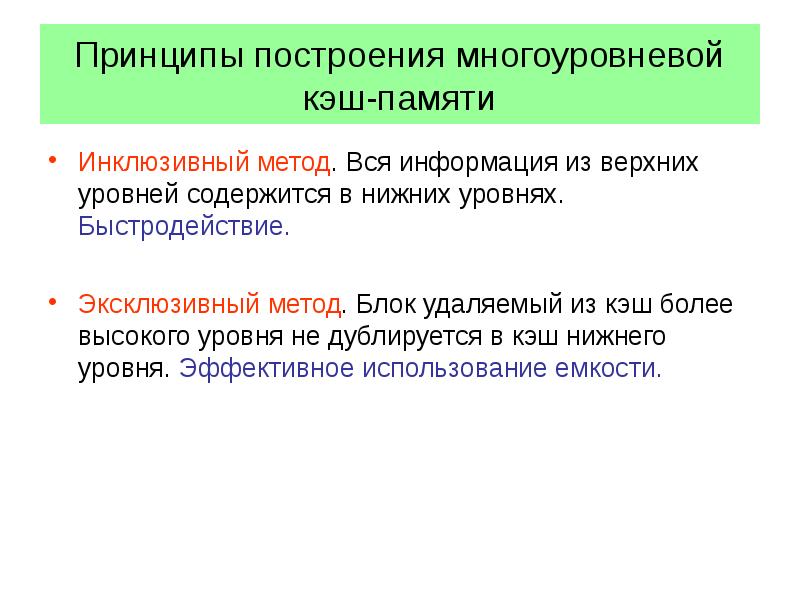

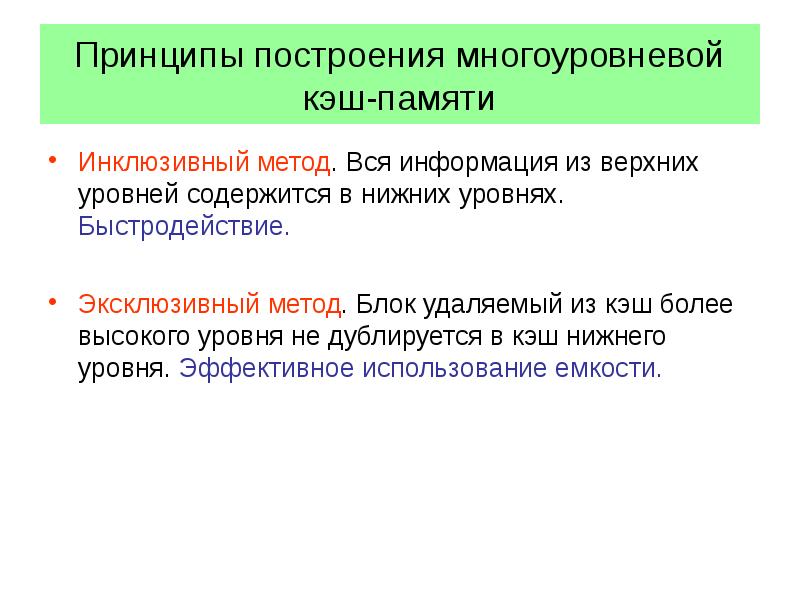

Принципы построения многоуровневой кэш-памяти Инклюзивный метод. Вся информация из верхних уровней содержится в нижних уровнях. Быстродействие. Эксклюзивный метод. Блок удаляемый из кэш более высокого уровня не дублируется в кэш нижнего уровня. Эффективное использование емкости.

Слайд 9

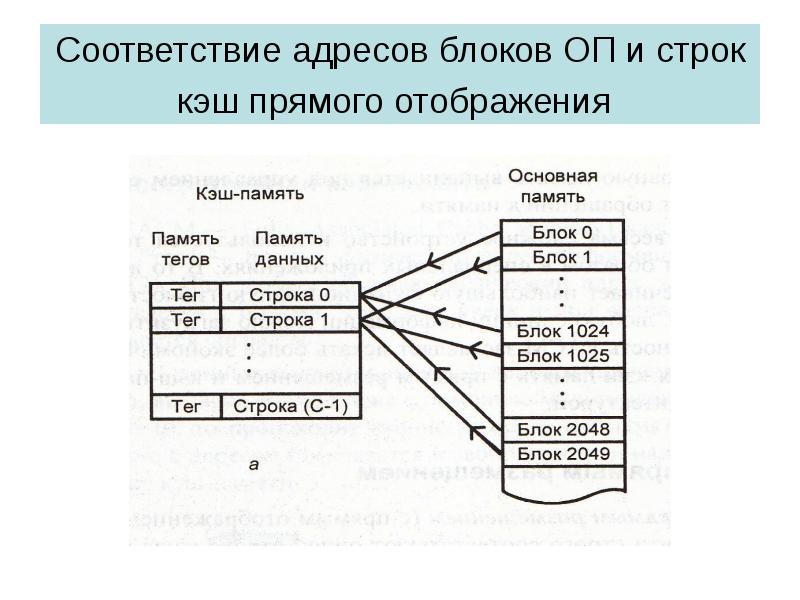

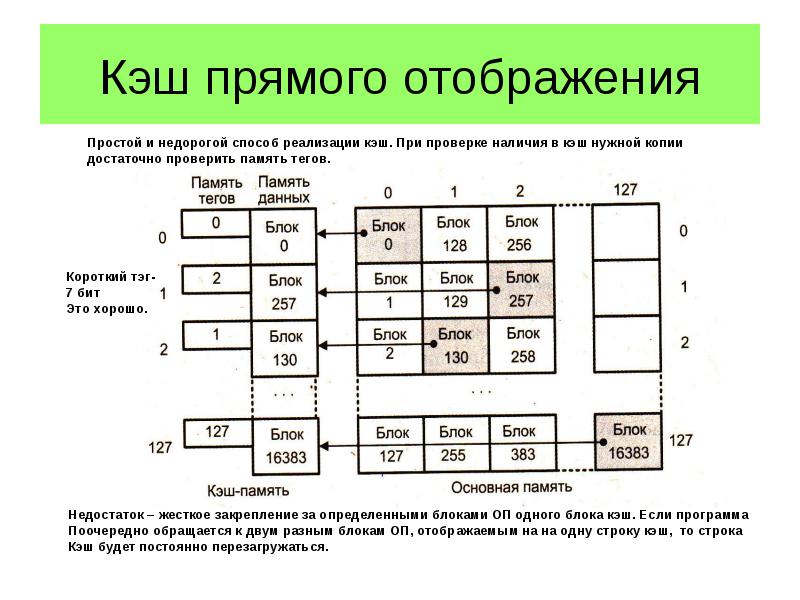

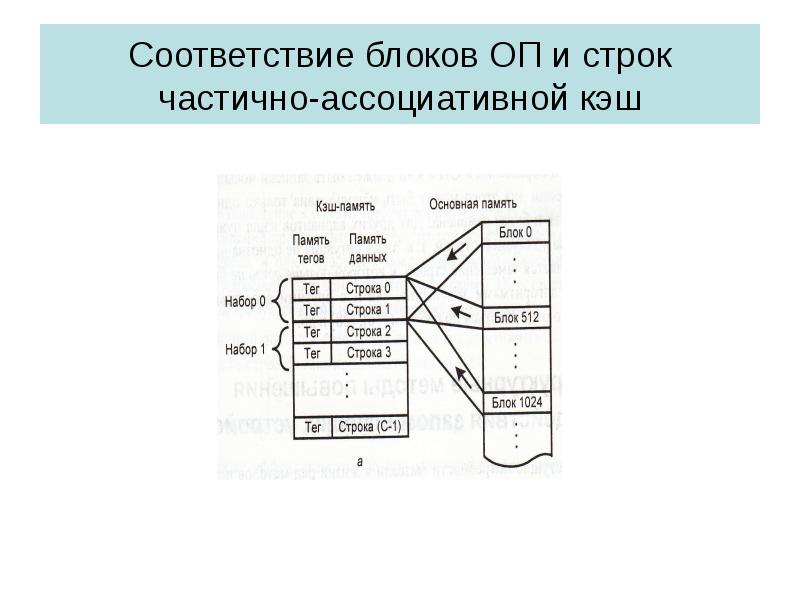

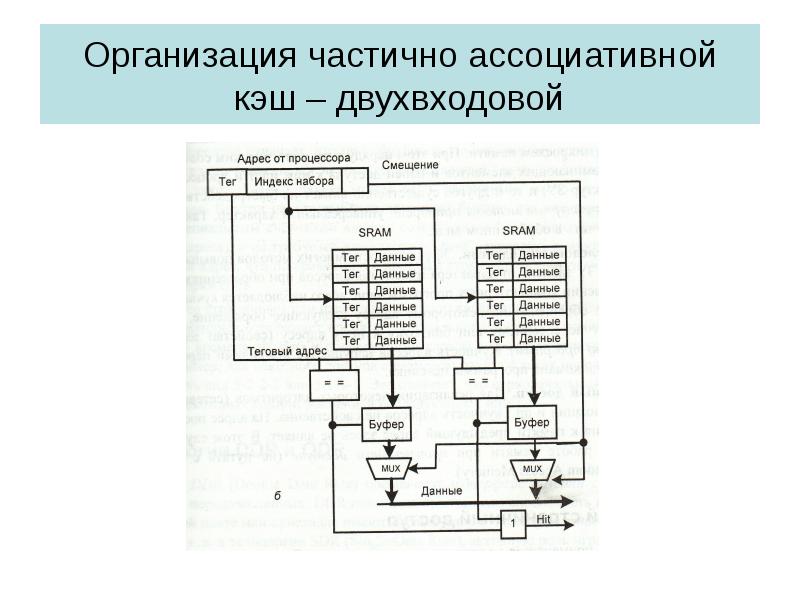

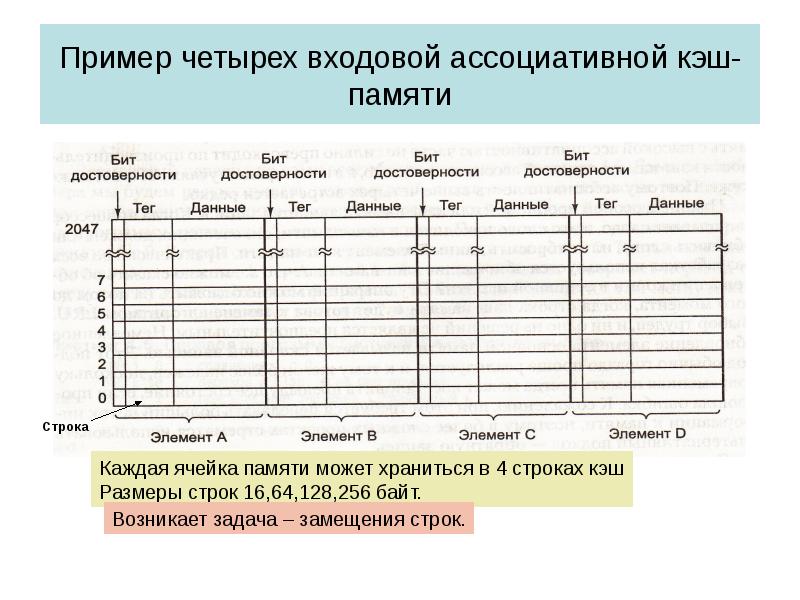

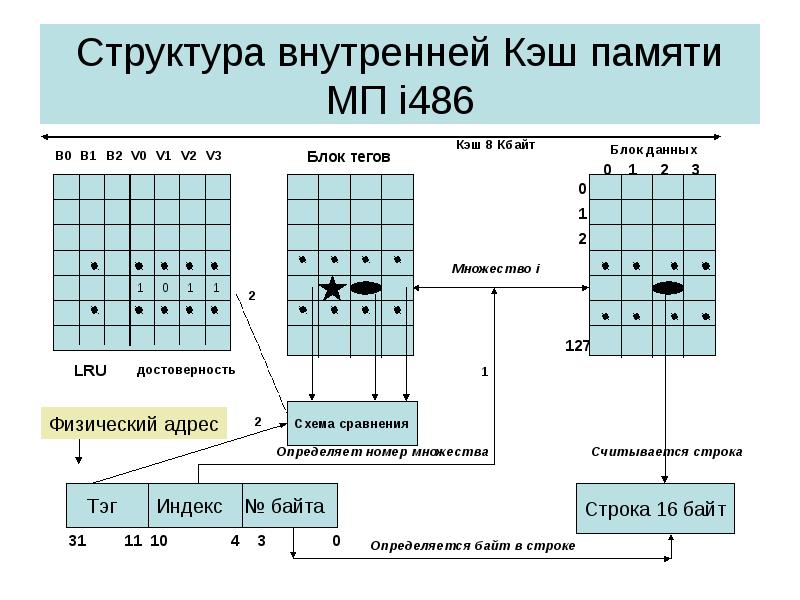

Классификация КЭШ по способу отображения основной памяти Кэш память прямого отображения. Кэш память ассоциативная с множественным доступом или частично ассоциативная. Кэш память полностью ассоциативная.

Слайд 10

Слайд 11

Слайд 12

Слайд 13

Слайд 14

Слайд 15

Слайд 16

Полностью ассоциативная кэш память Позволяет преодолеть недостаток прямого кэш, разрешая загрузку любого блока ОП в любой блок кэш.

Слайд 17

Слайд 18

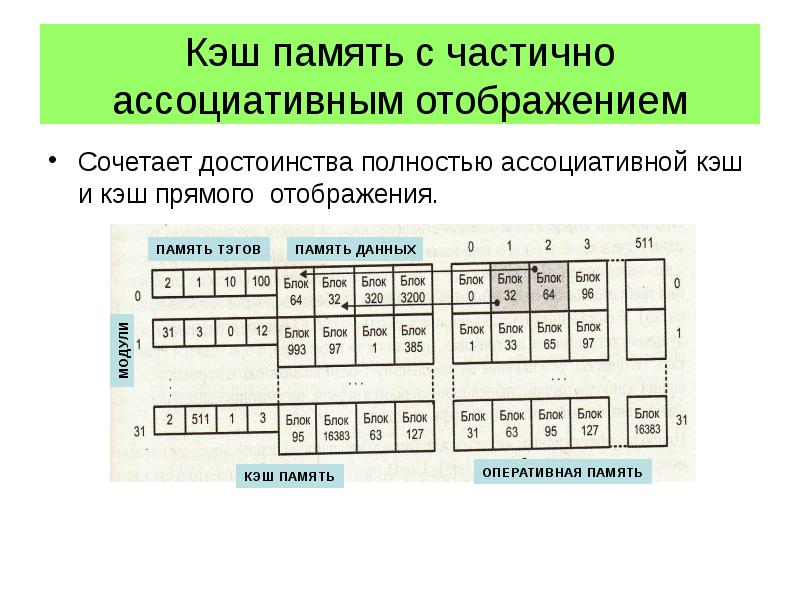

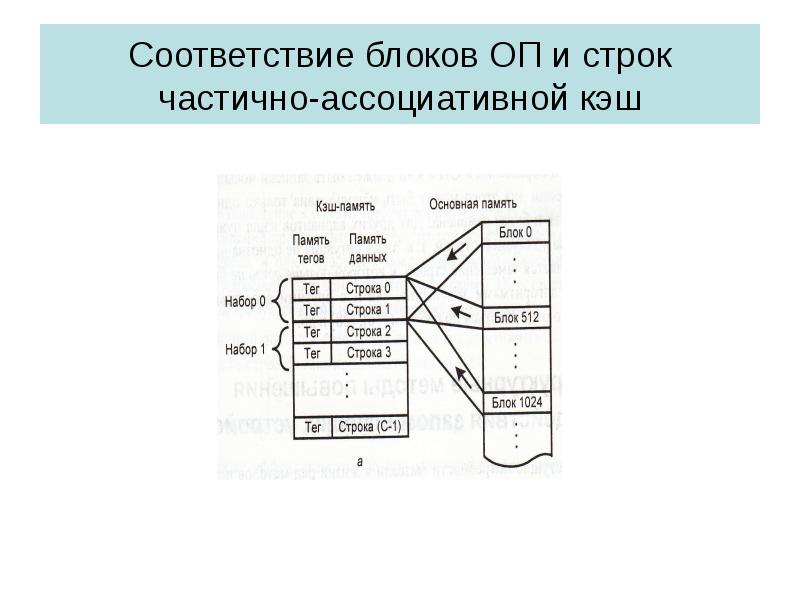

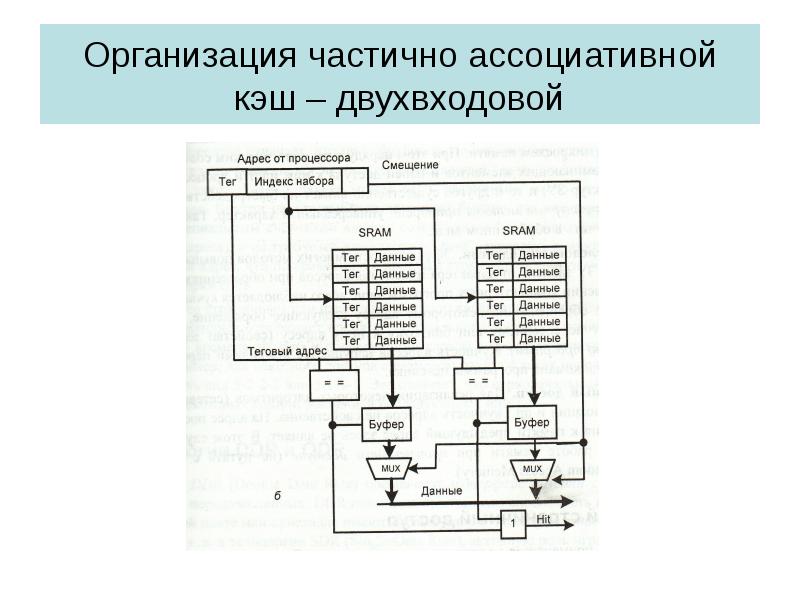

Кэш память с частично ассоциативным отображением Сочетает достоинства полностью ассоциативной кэш и кэш прямого отображения.

Слайд 19

Слайд 20

Слайд 21

Слайд 22

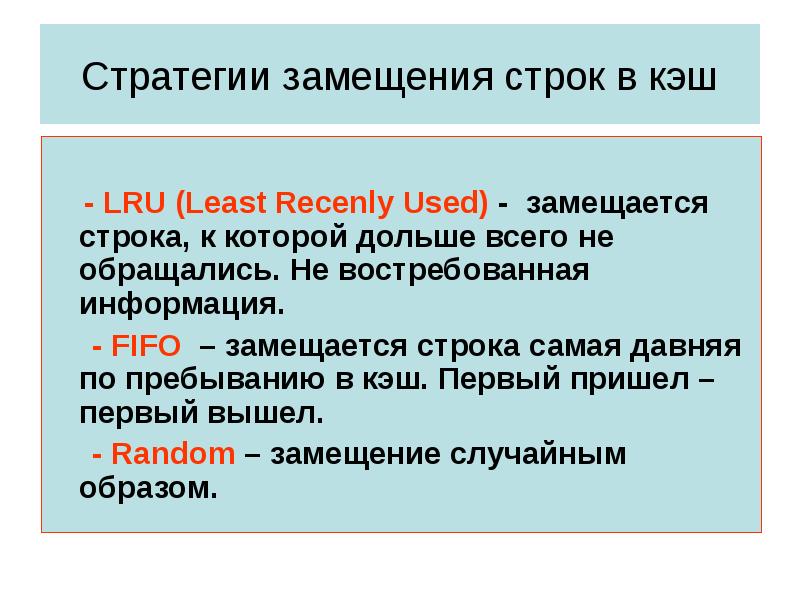

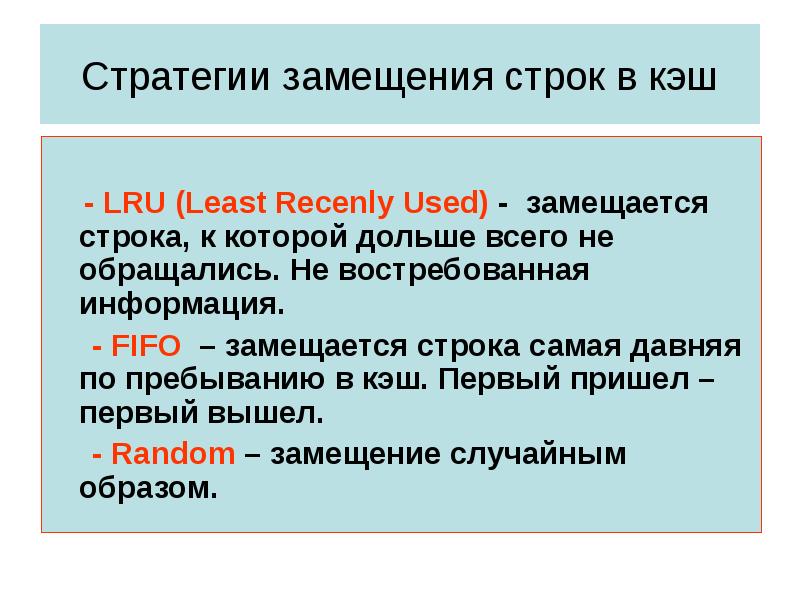

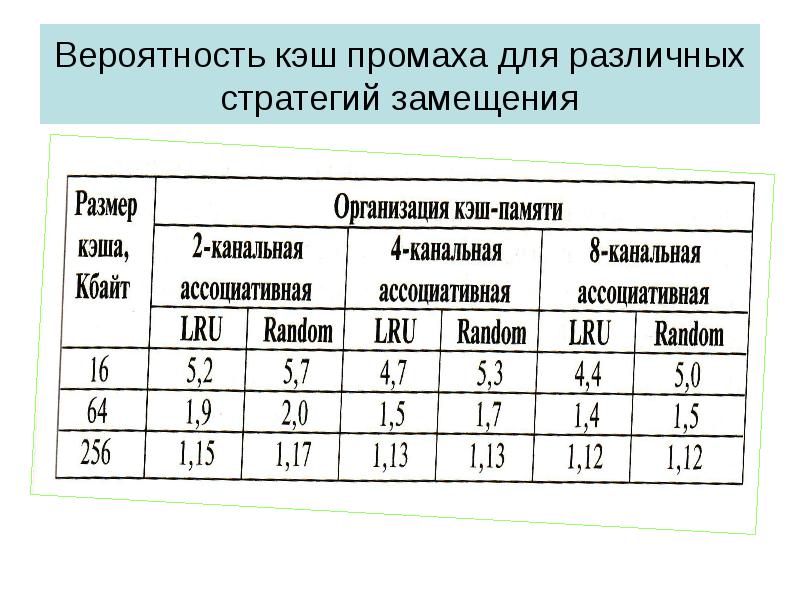

Стратегии замещения строк в кэш - LRU (Least Recenly Used) - замещается строка, к которой дольше всего не обращались. Не востребованная информация. - FIFO – замещается строка самая давняя по пребыванию в кэш. Первый пришел – первый вышел. - Random – замещение случайным образом.

Слайд 23

Слайд 24

Слайд 25

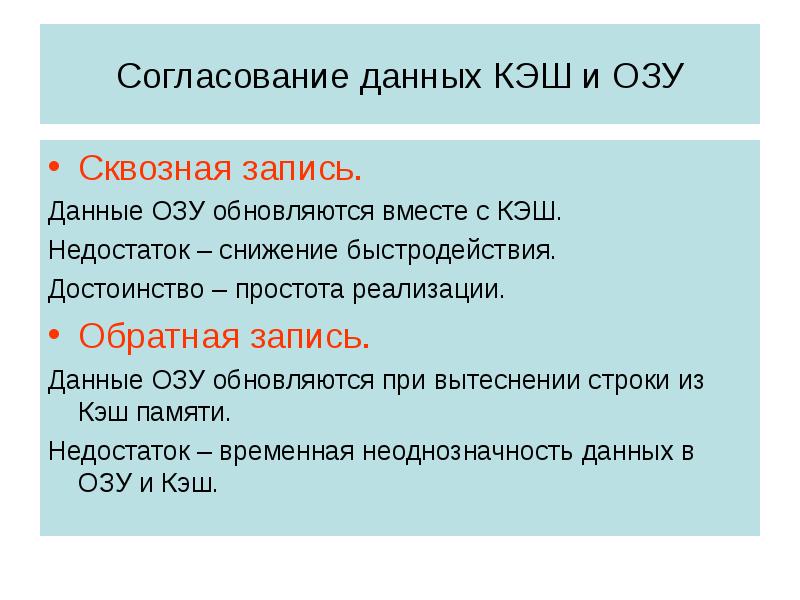

Согласование данных КЭШ и ОЗУ Сквозная запись. Данные ОЗУ обновляются вместе с КЭШ. Недостаток – снижение быстродействия. Достоинство – простота реализации. Обратная запись. Данные ОЗУ обновляются при вытеснении строки из Кэш памяти. Недостаток – временная неоднозначность данных в ОЗУ и Кэш.

Слайд 26

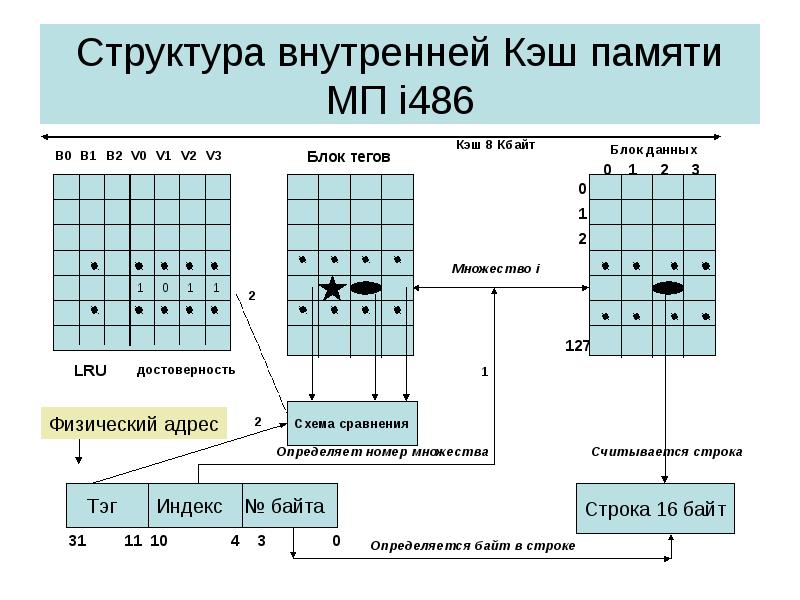

Режим работы кэш Задается программной установкой разрядов CD (запрет кэширования) и NW (запрет сквозной записи) в управляющем регистре CR0.

Слайд 27

Слайд 28

Слайд 29

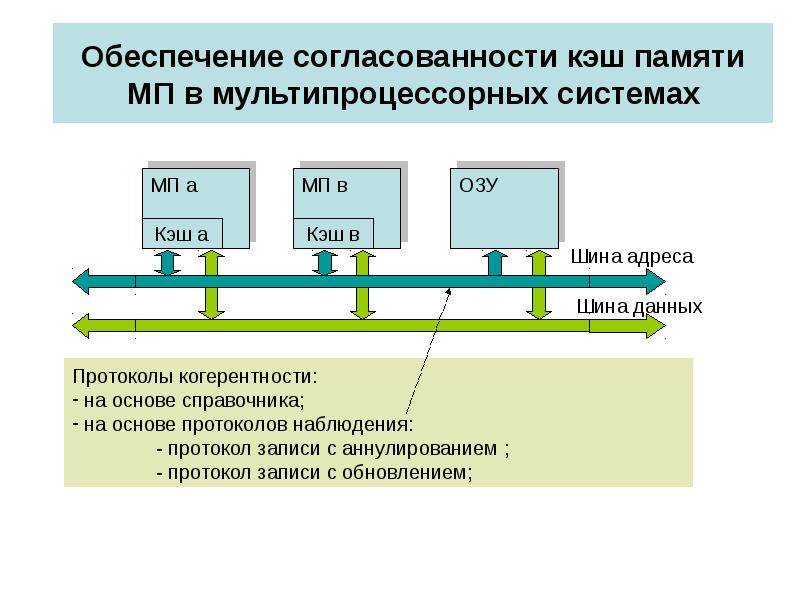

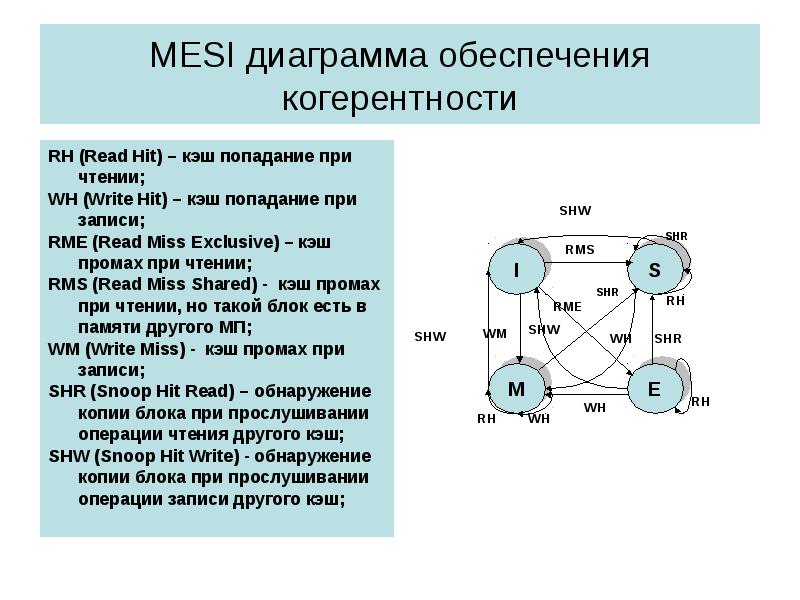

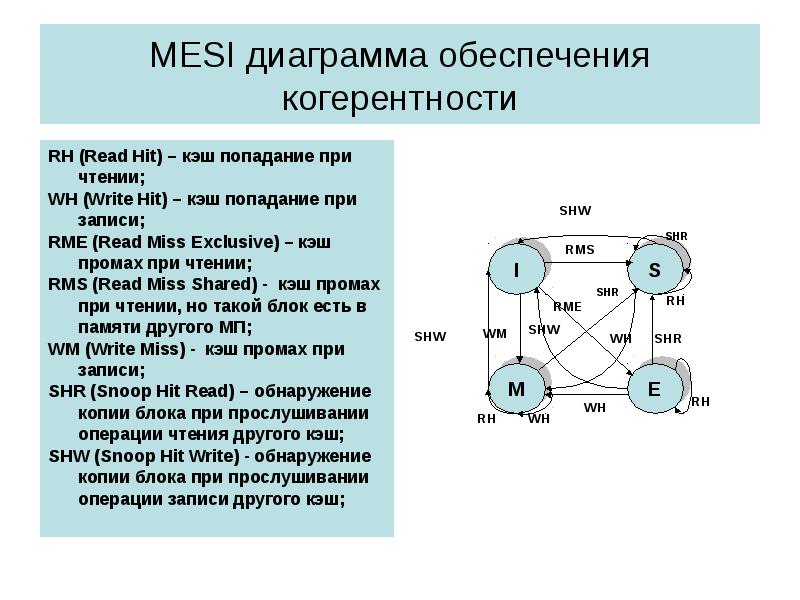

MESI диаграмма обеспечения когерентности RH (Read Hit) – кэш попадание при чтении; WH (Write Hit) – кэш попадание при записи; RME (Read Miss Exclusive) – кэш промах при чтении; RMS (Read Miss Shared) - кэш промах при чтении, но такой блок есть в памяти другого МП; WM (Write Miss) - кэш промах при записи; SHR (Snoop Hit Read) – обнаружение копии блока при прослушивании операции чтения другого кэш; SHW (Snoop Hit Write) - обнаружение копии блока при прослушивании операции записи другого кэш;

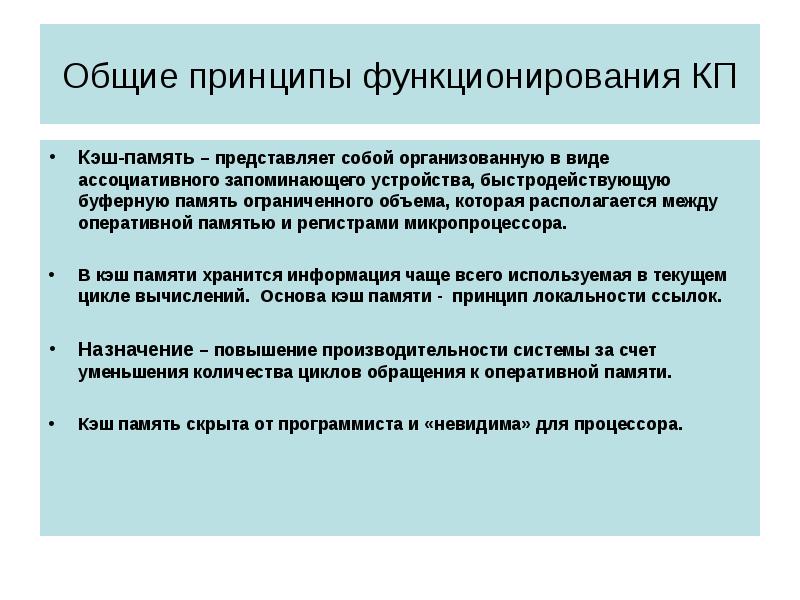

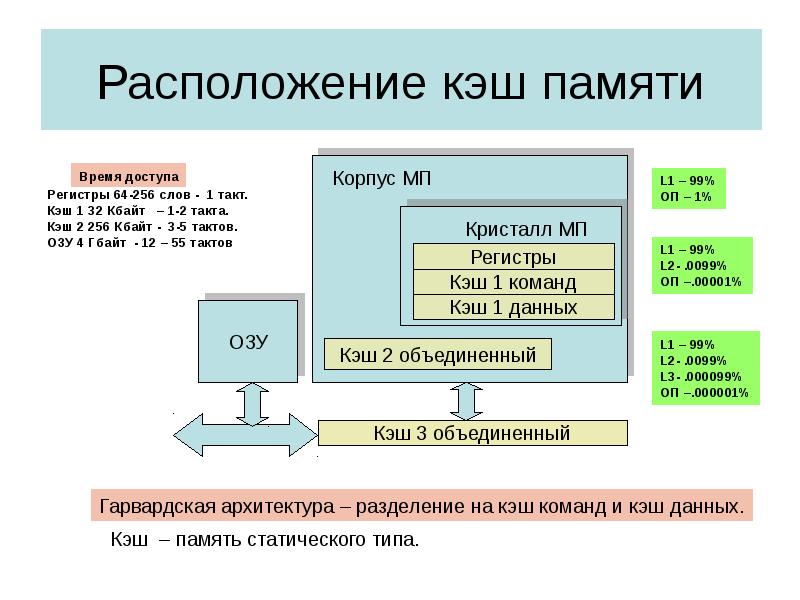

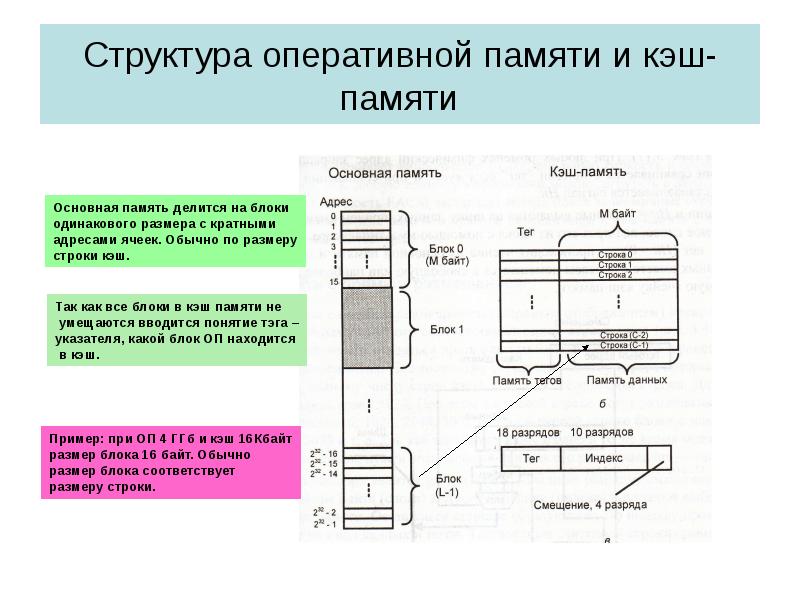

Концепции кэш-памяти Кэш-память является чисто аппаратным средством, “прозрачным” для выполняемых программ и представляет собой своеобразный буфер между основной памятью и центральным процессором (далее ЦП). Как правило, соотношение между емкостью кэш-памяти и оперативной памятью (далее ОП) составляет 1/100 – 1/1000 – в зависимости от типа ЭВМ. Как правило, передача данных между основной памятью и процессором производится через кэш-память, хотя в принципе возможна прямая передача (на рисунке показана пунктиром).

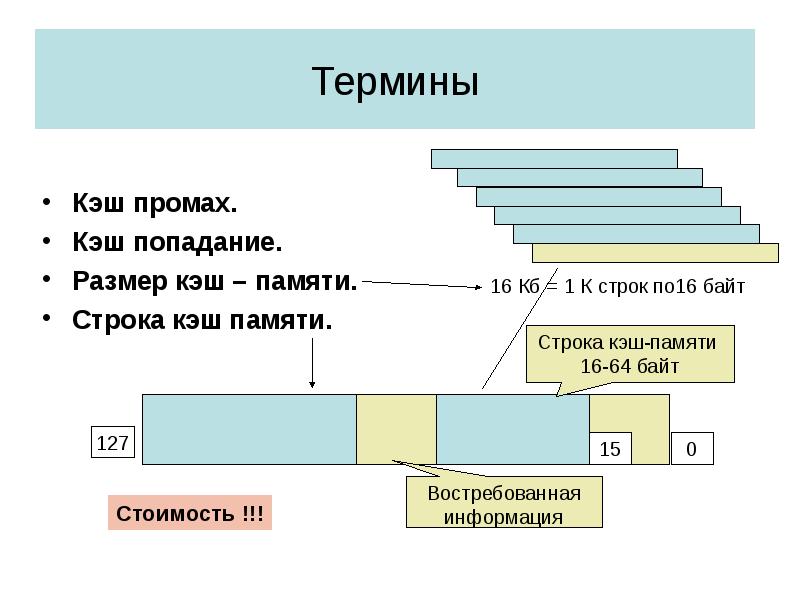

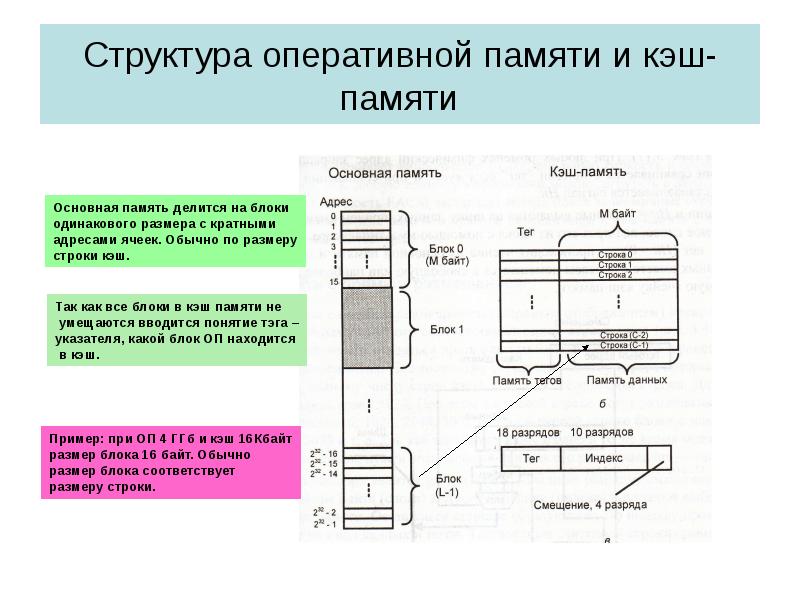

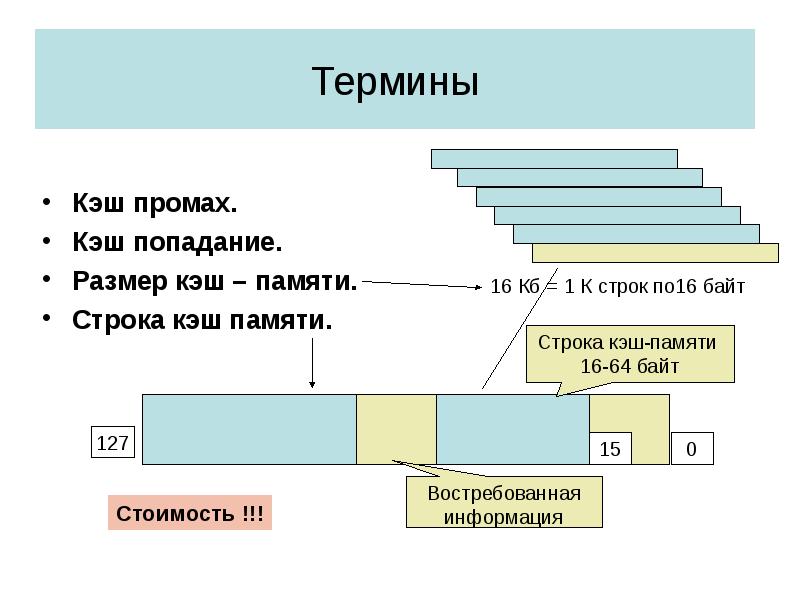

Кэш-память строится на основе элементов статической памяти (SRAM – Static Random Access Memory), а ОП – на элементах динамической памяти (DRAM – Dynamic RAM). Элементы SRAM представляют собой триггеры, а DRAM – по принципу действия подобны конденсатору. В связи со стеканием заряда во времени память типа DRAM требует периодической перезаписи (refresh). Кэш-память и основная память разделяются на блоки одинакового объема, размер которых обычно составляет 8.128 байт. Обычно блок ОП и кэш-памяти называют строкой (line). Обмен между ОП и кэш-памятью носит блочный характер. В кэш-памяти содержатся копии тех блоков ОП, к которым в последнее время выполнялись обращения со стороны ЦП. При любом обращении процессора к основной памяти определяется наличие блока, к которому производится обращение, в кэш-памяти. При нахождении блока в кэш-памяти (такая ситуация называется кэш-попаданием – cache-hit), осуществляется быстрое обращение (чтение или запись) со стороны ЦП в кэш-память; Обмен между ЦП и кэш-памятью осуществляется не на уровне блоков, а на уровне слов. Под словом в данном случае понимается объём данных, участвующих в одной пересылке между ЦП и кэш-памятью или ЦП и ОП. Разрядность слова определяется разрядностью шины данных между ЦП и кэш-памятью или ЦП и основной памятью; При отсутствии в кэш-памяти блока, к которому осуществляется обращение (такая ситуация называется кэш-промахом – cache-miss), сначала инициируется пересылка блока, содержащего затребованное слово, из ОП в кэш-память, а затем осуществляется обращение к этому слову из кэш-памяти. Как правило, подобный подход имеет место при обращении по чтению. При обращении по записи в случае отсутствия блока в кэш-памяти, запись может производиться и непосредственно в оперативную память без предварительной пересылки блока в кэш-память; Эффективность использования кэш-памяти определяется так называемым принципом локальности ссылок (доступа, обращений). Причем выделяются два вида локальности: пространственная и временная. Кроме того, принцип локальности рассматривается как в отношении команд, так и в отношении данных.

Пространственная локальность в отношении команд характеризуется тем, что вероятность выборки команды по следующему адресу, по сравнению с адресом исполняемой команды, намного больше, чем вероятность выборки команды по любому другому адресу. Этот принцип проявляется на линейных участках программы. По статистическим данным, средняя длина линейных участков большинства программ научно-технического профиля составляет 5-7 машинных команд. Пространственная локальность в отношении данных выражается в том, что вероятность обращения к слову данных по следующему адресу намного больше вероятности обращения к данным по любому другому адресу. Этот принцип проявляется, например, при обработке массивов данных. Временной аспект принципа локальности обращений в отношении команд предполагает большую вероятность обращения к команде по одному и тому же адресу в течение небольшого интервала времени. Этот аспект проявляется при выполнении программных циклов. В отношении данных временной аспект принципа локальности обращений означает большое значение вероятности обращений к одному и тому же слову данных в течение небольшого интервала времени. Этот аспект проявляется при многократной обработке массивов данных. В соответствии с принципом локальности ссылок, к слову, однажды прочитанному из ОП в кэш-память, будет выполняться несколько повторных обращений (временной аспект) и, кроме того, так как вместе с одним словом из ОП в кэш-память передается целый блок, состоящий из нескольких последовательных слов, то с большой вероятностью, ряд последующих обращений будет локализован в пределах этого блока (пространственный аспект).

Численной оценкой эффективности принятого принципа построения кэш-памяти является процент удачных обращений (процент кэш-попаданий), определяемый как отношение числа обращений к памяти, реализуемых через кэш, к общему числу обращений. Как правило, в современных компьютерах процент кэш-попаданий составляет 95.98 %. При построении кэш-памяти необходимо решить следующие задачи, определяющие её организацию: 1) выбор принципа отображения блоков основной памяти на блоки кэш-памяти (стратегия отображения \ распределения); 2) выбор принципа удаления блоков из кэш-памяти (стратегия замещения); 3) выбор принципа поддержания актуальности копий блоков кэш-памяти в блоках основной памяти (стратегия обновления ОП).

Читайте также: