Асинхронная память это кратко

Обновлено: 07.07.2024

SDRAM: Определение

Микросхемы SDRAM: Физическая организация и принцип работы

Схема обращения к ячейке памяти в самом общем случае может быть представлена следующим образом:

В современных микросхемах SDRAM схема обращения к ячейкам памяти выглядит аналогично. Далее, в связи с обсуждением задержек при доступе в память (таймингов памяти), мы рассмотрим ее более подробно.

Микросхемы SDRAM: Логическая организация

Модули SDRAM: Организация

Модули памяти: Микросхема SPD

Тайминги памяти

Схема доступа к данным микросхемы SDRAM

1. Активизация строки

2. Чтение/запись данных

3. Подзарядка строки

Соотношения между таймингами

В заключение этой части, посвященной задержкам при доступе к данным, рассмотрим основные соотношения между важнейшими параметрами таймингов на примере более простых операций чтения данных. Как мы рассмотрели выше, в самом простейшем и самом общем случае — для пакетного считывания заданного количества данных (2, 4 или 8 элементов) необходимо осуществить следующие операции:

1) активизировать строку в банке памяти с помощью команды ACTIVATE;

2) подать команду чтения данных READ;

3) считать данные, поступающие на внешнюю шину данных микросхемы;

В то же время, минимальному времени активности строки (от подачи команды ACTIVATE до подачи команды PRECHARGE, tRAS), по его определению, как раз отвечает промежуток времени между началом первой и началом четвертой операции. Отсюда вытекает первое важное соотношение между таймингами памяти:

где tRCD время выполнения первой операции, tCL второй, (tBL — (tCL — 1)) третьей, наконец, вычитание единицы производится вследствие того, что период tRAS не включает в себя такт, на котором осуществляется подача команды PRECHARGE. Сокращая это выражение, получаем:

Сегодня на очереди у нас история ОЗУ – что в расшифровке значит оперативное запоминающее устройство. От самых первых до самых передовых, всё как вы любите.

Для полноценного понимания давайте сначала определимся, что же такое оперативная память. ОЗУ на английском Random Access Memory, RAM —

если очень упростить, это такая память, которая хранит временные данные (запущенные игры, программы, операционную систему). ОЗУ является неким соединяющим звеном между процессором и накопителем, будь то ссд или хдд. А нужна она для того, чтобы оперативно и быстро выполнять задачи, так как те же накопители, как правило, имеют низкую скорость ввода-вывода информации; и в теории, если убрать оперативку из этого звена, то задачи бы исполнялись в несколько раз дольше. И еще данные ОЗУ хранятся только во время непосредственно работы самой программы/операционной системы, то есть во время отключения компьютера данные с неё стираются.

В большинстве случаев - энергозависимая часть системы компьютерной памяти, в которой во время работы компьютера хранится выполняемый машинный код (программы), а также входные, выходные и промежуточные данные, обрабатываемые процессором. Обмен данными между процессором и оперативной памятью производится как непосредственно, так и через сверхбыструю память нулевого уровня либо при наличии аппаратного кэша процессора — через кэш.

Содержащиеся в полупроводниковой оперативной памяти данные доступны и сохраняются только тогда, когда на модули памяти подаётся напряжение. Выключение питания оперативной памяти, даже кратковременное, приводит к потере хранимой информации.

Итак, с чего всё началось?

В ЭВМ первого поколения использовалось множество разновидностей и конструкций запоминающих устройств, основанных на различных физических принципах:

- на электромагнитных реле

- на акустических линиях задержки

- на электронно-лучевых трубках

- на электронно-лучевых трубках

В качестве ОЗУ использовались также магнитные барабаны, обеспечивавшие достаточно малое для ранних компьютеров время доступа; также они использовались в качестве основной памяти для хранения программ и данных.

Второе поколение требовало более технологичных, дешёвых и быстродействующих ОЗУ. Наиболее распространённым видом ОЗУ в то время стала ферритовая память на магнитных сердечниках.

Начиная с третьего поколения, большинство электронных узлов компьютеров стали выполнять на микросхемах, в том числе и ОЗУ. Наибольшее распространение получили два вида ОЗУ:

- статическая память (SRAM) в виде массива триггеров;

- динамическая память (DRAM) в виде массива конденсаторов.

SRAM хранит бит данных в виде состояния триггера. Этот вид памяти является более дорогим в расчёте на хранение 1 бита; как правило, имеет меньшее время доступа, но большее энергопотребление, чем DRAM. В современных компьютерах SRAM часто используется в качестве кэш-памяти процессора.

DRAM хранит бит данных в виде заряда конденсатора. Однобитовая ячейка памяти содержит конденсатор и транзистор. Конденсатор заряжается до высокого или низкого напряжения (логические 1 или 0). Транзистор выполняет функцию ключа, соединяющего конденсатор к схеме управления, расположенной на том же чипе. Схема управления позволяет считывать состояние заряда конденсатора или изменять его. Так как хранение 1 бита информации в этом виде памяти дешевле, DRAM преобладает в компьютерах третьего поколения.

DRAM хранит бит данных в виде заряда конденсатора. Однобитовая ячейка памяти содержит конденсатор и транзистор. Конденсатор заряжается до высокого или низкого напряжения (логические 1 или 0). Транзистор выполняет функцию ключа, соединяющего конденсатор к схеме управления, расположенной на том же чипе. Схема управления позволяет считывать состояние заряда конденсатора или изменять его. Так как хранение 1 бита информации в этом виде памяти дешевле, DRAM преобладает в компьютерах третьего поколения.

Но что до современной памяти? С чего всё началось?

Память на микросхемах.

Революция на оперативном поприще случилась в 1970 году, когда были освоены микросхемы. Память на них выпустили сразу два производителя – уже крупный и известный игрок IBM и молодая ещё никому неизвестная конторка Intel. В IBM большую роль в появлении памяти сыграл доктор Роберт Деннард.

Впрочем, история сложилась так, что именно Intel представила в последствии самый популярный на тот момент чип памяти i1103 ёмкостью 1 кбит.

Появление подобных компактных чипов памяти позволило появится на свет первым микропроцессорам и относительно компактным калькуляторам. А в 1972 году однотранзисторная DRAM вытеснила ферромагнитную память с рынка. И скоро начали уходить в прошлое и громоздкие компьютеры величиной с комнату, передавая место пусть и увесистым, но всё же настольным персональным компьютерам. Да и объём памяти стал расти, дойдя на пике своего развития от 64 кб до 1 Мб.

Первые планки памяти.

Кстати о ней. Её разработала компания Micron и выпускала с 1995 по 1996 год в компьютерах на основе Intel Pentium. Имела объём 16Мб, частоту 40 МГц, а пропускную способность - 320 Мб/сек. Напряжение было внушительным – 5 Вольт. В отличии от FPM памяти, в памяти EDO при выставлении сигнала CAS в линию продолжали выдаваться данные с текущего такта, что позволило сократить длительность цикла чтения. Что, впрочем, продержаться на плаву типу памяти не помогло – уже в 1996 году её окончательно вытеснила SDRAM.

Но вернёмся в 1993 год. Именно тогда компания Samsung представляет SDRAM. Такое деловитое слово означает Синхронная Динамическая Память с Произвольным Доступом. Память на отдельных микросхемах, которую можно менять самостоятельно в случае необходимости. Первоначально память предлагалась как альтернатива дорогущей VRAM, однако быстро прижилась в качестве оперативной памяти и стала очень быстро вытеснять остальные виды динамической памяти. К 2000 году SDRAM стала единственным видом ОЗУ. Первые планки имели объём в 16 Мб и частоту 66, 100 или 133 МГц. Время доступа к данным составляло 10 наносекунд. В отличии от других типов DRAM, использовавших асинхронный обмен данными, ответ на поступивший в устройство управляющий сигнал возвращается не сразу, а лишь при получении следующего тактового сигнала.

Там же, в нулевых, появилась комиссия JEDEC – участники рынка памяти сформировали стандарты и спецификации памяти, утвердили частотные и электрические характеристики.

И впрочем, был ещё один тип памяти, который прожил не долгую, но яркую и насыщенную жизнь – RDRAM. Появилась на свет божий этот тип в 1996 году силами производителей Rambus и Intel. Память имела революционные характеристики – высокие частоты обеспечивали 99% загрузку канала памяти, когда у конкурентов это значение не превышало 70%. Пропускная способность первых планок равнялась немыслимым 1 гбит/Сек, а позже появились планки с пропускной способностью аж 4 гбит/Сек. Память ринулись закупать крупнейшие производители, такие как Samsung, LG, и AMD. В 1999 году на выставке IDF вновь показали RDRAM плашки с частотой в 800 МГц. Вы только вдумайтесь: 800 МГц против 133 МГц у конкурентов! Были даже готовые первые матплаты с поддержкой данной памяти, однако за 2 дня до презентации мероприятие было перенесено на неопределённый срок из-за вскрывшейся ошибки памяти memory bit error. В тот момент из-за переносов Intel потеряла около 100 млн долларов. Это, на минуточку, 1999 год - деньжищи были огромные!

Ну, разумеется, память тогда не умерла, а смогла добраться до рынка и даже прописаться в двух игровых консолях - PlayStation 2 и Nintendo 64. Однако к началу нулевых её доля рынка уменьшилась до нескольких процентов: тип RDRAM была весьма производительной, но жутко дорогой, а производители к тому времени уже сконцентрировались на другом типе памяти – DDR.

DDR память - синхронная динамическая память с произвольным доступом и удвоенной скоростью передачи данных.

Прототипы памяти нового поколения показала Samsung в 1997 году, а в 1998 присоединилась и Hyundai Electronics (ныне SK Hynix). Однако широко использоваться они стали только в 2000 году, когда были выпущены первые матплаты с поддержкой нового стандарта.

DDR является улучшением синхронной памяти с произвольным доступом SDRAM, например, скорость передачи данных была удвоена.

Однако, в отличии от первой SDRAM, считывание данных происходит не только по фронту, но и по спаду тактового сигнала. То есть удвоение скорости достигается не за счёт повышения частот. При фактических 100 МГц мы получаем 200 МГц эффективной частоты – вот откуда берутся корни разделения частоты на фактическую и эффективную, вплоть до наших дней.

Что по характеристикам, то тактовые частоты варьировались от 100 до 200 МГц. Теперь эти значения надо было умножать на 2. Техпроцесс 130-нм. Объём от 512 Мб до 1Гб.

Тут ещё стоит сделать сноску о том, что было 2 типа DRAM: синхронная и асинхронная память.

Синхронная DRAM использует системные часы для доступа к памяти, из-за чего ЦП знает время или точное количество циклов, в течение которых данные будут доступны из ОЗУ на ввод-вывод. Что, как вы понимаете, положительно влияет на производительность системы.

Асинхронная же память к системным часам не обращается, считывая сигналы с входной и выходной шины, что вызывает высокие задержки и падение скорости работы.

К слову, еще стоит немного упомянуть графическую память – GDDR. Общими отличиями GDDR от DDR являются более высокие номинальные частоты работы первой. Также GDDR содержит упрощения электрического интерфейса и применение ряда специальных приёмов управления буфером ввода-вывода, что позволяет достичь несколько бо́льшей пропускной способности и более высоких рабочих частот по сравнению с DDR SDRAM. Кроме этого, GDDR имеет по сравнению с DDR более низкое энергопотребление и тепловыделение при работе на равных частотах.

DDR2 и DDR3

Представлен новый стандарт был в 2003 году. Частоты выросли – теперь диапазон составлял от 100 до 266 МГц тактовой частоты (200 – 533 МГц эффективной), а объём довели до 2 Гб, хотя были в продаже и модули по 8 Гб. Ну и напряжение снизили во многом благодаря 90-нм техпроцессу. Позже для видеокарт появится GDDR2. GDDR2 по сути является DDR2 с интерфейсом и упаковкой, спроектированными специально для работы на максимально возможных частотах и для коротких шин.

Далее в 2007 году вышла DDR3, которая используется по сей день многими пользователями. Виток развития, если коротко, был тот же: увеличить память и частоту, снизить напряжение, в том числе за счёт более тонкого техпроцесса. Первые партии шли на 90-нм, затем память переехала на 65-нм, далее на 50-нм и наконец на 40-нм. Ну и увеличение буфера предварительной выборки с 4 пакетов DDR2 до 8 пакетов в DDR3. Выросли вдвое тактовые частоты до 400 и 1200 МГц, и 800 и 2400 МГц эффективной частоты. А объём варьировался от 1 до 16 Гб.

Также была и GDDR3 для графических карт, но при этом имела такое же технологическое ядро, как DDR2, но более высокую эффективную частоту

В 2014 году на публичный рынок выходит DDR4.

На данный момент последнее поколение памяти, использующееся на широком потребительском рынке.

До сегодняшнего дня планки памяти прошли путь от 36-нм до 16-нм техпроцесса. Выросли и тактовые частоты – от 800 до 1600 МГц (эффективная - от 1600 до 3200 МГц). Хотя, конечно, со временем во всех поколениях, и в DDR4 в том числе, производители умудряются разгонять свои планки свыше обозначенных рамок, что весьма хорошечно.

Что на счёт GDDR4? Она вообще является аналогом DDR3, но как полагается для графической памяти имеет более высокую эффективную частоту. Работала на частотах от 1 ГГц (2 Ггц эффективной) и вплоть до 2,2-2,4 Ггц (4-4,8 эффективной ), но этот тип памяти широкого распространения не получил из-за цены и несущественного прироста в сравнении с GDDR3.

DDR5 – игра стоит свеч?

Новый стандарт памяти по сути дебютировал на рынке вместе с 12 поколением Intel Alder Lake, ведь именно тогда производители активно стали анонсировать свои планки памяти, а на рынке появились процессоры и матплаты с поддержкой новой памяти.

Согласно спецификациям Hynix, пропускная способность DDR5 почти в 2 раза выше, чем у DDR4 – до 5600 мбит/Сек на линию. Скорость работы тоже увеличилась в 2 раза – с 3,2 до 6,4 гбит/Сек. Плотность ядра увеличилась с 16 до 64 гбит. Вольтаж снова снизили – стандартная планка работает с напряжением в 1,1В. Релиз ожидается либо в конце 2021 года, либо уже в 2022 году. Первые планки имеют скорость от 4800 до 6800 мгц, однако в будущем появятся и более скоростные планки с частотой около 8000 мгц. За частотами увеличились и тайминги. Они выше, чем у DDR4, но на производительности это не отразится - всё же рост частот и пропускной способности с головой перекрывают такой досадный элемент, да и опять же, потенциал новой памяти пока не раскрыт. Так уж вышло, что старт новой памяти пришёлся на релиз 11 Windows, которая по сложившейся традиции оказалась, скажем так, сыроватой. В будущем, когда оптимизируют новую винду, допилят биосы новых гибридных Alder Lake, всё может поменяться. Тем более, что в планках реализована поддержка ЕСС – коррекция ошибок в реальном времени, так что неудивительно, что задержки и тайминги стали повыше.

Увеличился и объём. Теперь 1 планка даёт сборке от 16 Гб памяти, а максимальный объём при помощи технологии производства Through-Silicon-Via - аж 256тГб.

Что интересно, на рынке уже давно существуют GDDR5 и GDDR5X, а недавно появилась и GDDR6. Это, конечно, не одно и тоже, но просто любопытно, как была нарушена преемственность поколений и видеопамять по своему развитию ускакала далеко вперёд, по крайней мере в номерном порядке.

Взглянув на путь развития памяти, можно увидеть, как возрастала их производительность. И, как видим, память прошла огромный путь - от самых простых до самых быстрых и инновационных. Это прогресс, детка!

Теперь поговорим о ней чуть детальнее.

Что интересно, GDDR5 соответствует DDR3, имеет удвоенные каналы связи, а также буферы предварительной выборки шириной 8 битов, как у GDDR4. Память типа GDDR5 обеспечивает вдвое большую пропускную способность по сравнению с GDDR3. Однако на данный момент из GDDR5 выжаты почти все соки, начиная от 900 Мгц (3600 эффективной) в HD 4870 до 2500 Мгц (10000 эффективной) в GTX 1080. В последствии была представлена и GDDR5X. Говоря конкретнее, в GDDR5X возможны скорости передачи 10-14 Гбит/с, что вдвое превосходит возможности GDDR5.

Следующим шагом в развитии стала уже GDDR6, что по заверениям JEDEC снова в два раза быстрее, чем GDDR5. Выходит, где-то на уровне GDDR5X? Можно сказать и так. Но рабочее напряжение снижено на 10 %. Также одной из отличительных особенностей новой памяти является работа каждой микросхемы в двухканальном режиме. Появилась данная память с анонсом Nvidia RTX 2000. А что было дальше? Все мы уже знаем, что с анонсом RTX 3000 была показана GDDR6X c впечатляющей пропускной способностью. Скорость передачи данных для одного контакта GDDR6X достигает 21 Гбит/с, тогда как у GDDR6 этот показатель составлял лишь 16 Гбит/с. В результате пропускная способность всей подсистемы памяти раньше (имеется в виду с GDDR6) могла достигать порядка 700 Гбайт/с, а теперь этот показатель может доходить до 1 Тбайт/с. Вот такие вот сверхскорости! Однако энергопотребление возросло существенно, как и температуры самих чипов.

Пожалуй, на этом у нас всё! Данный материал является ознакомительным и содержит упущения в угоду его усвояемости, более подробно вам всегда всё расскажет Гугл. Мы кратенько прошлись по истории оперативной памяти и надеемся, что вам всё понравилось.

Издано: 2003, BHV

Твердый переплет, 560 стр..

Принципы функционирования SRAM

История

История создания статической памяти уходит своими корнями в глубину веков. Память первых релейных компьютеров по своей природе была статической и долгое время не претерпевала практически никаких изменений (во всяком случае - концептуальных), - менялась лишь элементарная база: на смену реле пришли электронные лампы, впоследствии вытесненные сначала транзисторами, а затем TTL- и CMOS-микросхемами… но идея, лежащая в основе статической памяти, была и остается прежней…

Динамическая память, изобретенная, кстати, значительно позднее, в силу фундаментальных физических ограничений, так и не смогла сравняться со статической памятью в скорости.

В ядре

Ядро микросхемы статической оперативной памяти (SRAM - Static Random Access Memory) представляет собой совокупность триггеров - логических устройств, имеющих два устойчивых состояния, одно из которых условно соответствует логическому нулю, а другое - логической единице. Другими словами, каждый триггер хранит один бит информации, - ровно столько же, сколько и ячейка динамической памяти (см. статью "Устройство и принципы функционирования оперативной памяти. В ядре").

Между тем, триггер как минимум по двум позициям обыгрывает конденсатор: а) состояния триггера устойчивы и при наличии питания могут сохраняться бесконечно долго, в то время как конденсатор требует периодической регенерации; б) триггер, обладая мизерной инертностью, без проблем работает на частотах вплоть до нескольких ГГц, тогда как конденсаторы "сваливаются" уже на 75-100 МГц.

К недостаткам триггеров следует отнести их высокую стоимость и низкую плотность хранения информации. Если для создания ячейки динамической памяти достаточного всего одного транзистора и одного конденсатора, то ячейка статической памяти состоит как минимум из четырех, а в среднем шести - восьми транзисторов, поэтому мегабайт статической памяти оказывается по меньшей мере в несколько раз дороже.

Устройство триггера

В основе всех триггеров лежит кольцо из двух логических элементов "НЕ" (инверторов), соединенных по типу "защелки" (см. рис. 1). Рассмотрим, как он работает. Если подать на линию Q сигнал, соответствующий единице, то, пройдя сквозь элемент D.D1 он обратится в ноль. Но, поступив на вход следующего элемента, - D.D2 - этот ноль вновь превратится в единицу. Поскольку, выход элемента D.D2 подключен ко входу элемента D.D1, то даже после исчезновения сигнала с линии Q, он будет поддерживать себя самостоятельно, т.е. триггер перейдет в устойчивое состояние. Образно это можно уподобить дракону, кусающему себя за хвост.

Естественно, если на линию Q подать сигнал, соответствующий логическому нулю, - все будет происходить точно так же, но наоборот!

Рис. 1. Устройство простейшего триггера (слева). Образно это можно представить драконом, кусающим свой хвост

Устройство элемента "НЕ" (инвертора)

Как устроен элемент "НЕ"? На этот вопрос нельзя ответить однозначно. В зависимости от имеющейся у нас элементарной базы, конечная реализация варьируется в очень широких пределах. Ниже в качестве примера приведена принципиальная схема простейшего инвертора, сконструированного из двух последовательно соединенных комплементарых /* взаимно дополняемых */ CMOS-транзисторов - p- и n- канального (см. рис. 2). Если на затворы подается нулевой уровень, то открывается только p-канал, а n-канал остается разомкнутым. В результате, на выходе мы имеем питающее напряжение (т. е. высокий уровень). Напротив, если на затворы подается высокий уровень, размыкается n-канал, а p-канал - замыкается. Выход оказывается закорочен на массу и на нем устанавливается нулевое напряжение (т. е. низкий уровень).

Рис. 2. Устройство элемента НЕ (инвертора)

Устройство матрицы статической памяти

Подобно ячейкам динамической памяти (см. статью "Устройство и принципы функционирования оперативной памяти. Conventional DRAM Page Mode DRAM - "обычная" DRAM"), триггеры объединяются в единую матрицу, состоящую из строк (row) и столбцов (column), последние из которых так же называются битами (bit).

В отличии от ячейки динамической памяти, для управления которой достаточно всего одного ключевого транзистора, ячейка статической памяти управляется как минимум двумя. Это не покажется удивительным, если вспомнить, что триггер, в отличии от конденсатора, имеет раздельные входы для записи логического нуля и единицы соответственно. Таким образом, на ячейку статической памяти расходуется целых шесть транзисторов (см. рис. 3) - четыре идут, собственно, на сам триггер и еще два - на управляющие "защелки".

Рис. 3. Устройство 6-транзисторной одно-портовой ячейки SRAM-памяти

Причем, шесть транзисторов на ячейку - это еще не предел! Существуют и более сложные конструкции! Основной недостаток шести транзисторной ячейки заключается в том, что в каждый момент времени может обрабатываться всего лишь одна строка матрицы памяти. Параллельное чтение ячеек, расположенных в различных строках одного и того же банка невозможно, равно как невозможно и чтение одной ячейки одновременно с записью другой.

Этого ограничения лишена многопортовая память. Каждая ячейка многопортовой памяти содержит один-единственный триггер, но имеет несколько комплектов управляющих транзисторов, каждый из которых подключен к "своим" линиям ROW и BIT, благодаря чему различные ячейки матрицы могут обрабатываться независимо. Такой подход намного более прогрессивен, чем деление памяти на банки. Ведь, в последнем случае параллелизм достигается лишь при обращении к ячейкам различных банков, что не всегда выполнимо, а много портовая память допускает одновременную обработку любых ячеек, избавляя программиста от необходимости вникать в особенности ее архитектуры. (Замечание: печально, но кэш-память x86-процессор не истинно многопортовая, а состоит из восьми одно-портовых матриц, подключенных к двух портовой интерфейсной обвязке)

Наиболее часто встречается двух - портовая память, устройство ячейки которой изображено на рис. 4. (внимание! это совсем не та память которая, в частности, применяется в кэше первого уровня микропроцессоров Intel Pentium). Нетрудно подсчитать, что для создания одной ячейки двух - портовой памяти расходуется аж восемь транзисторов. Пусть емкость кэш-памяти составляет 32 Кб, тогда только на одно ядро уйдет свыше двух миллионов транзисторов!

Рис. 5, 6. Ячейка динамической памяти воплощенная в кристалле

Устройство интерфейсной обвязки

По своему устройству, интерфейсная обвязка матрицы статической памяти, практически ничем не отличается от аналогичной ей обвязки матрицы динамической памяти (см. статью Устройство и принципы функционирования оперативной памяти. Conventional DRAM Page Mode DRAM - обычная DRAM") Поэтому, не будем подробно останавливаться на этом вопросе и рассмотрим его лишь в общих чертах.

Пожалуй, единственное различие в интерфейсах статической и динамической памяти заключается в том, что микросхемы статической памяти имея значительно меньшую емкость (а, следовательно - и меньшее количество адресных линий) и геометрически располагаясь гораздо ближе к процессору, могут позволить себе роскошь не прибегать к мультиплексированию. И потому, для достижения наивысшей производительности, номера строк и столбцов чаще всего передаются одновременно.

Если статическая память выполнена в виде самостоятельной микросхемы, а не располагается непосредственно на кристалле процессора, линии ее входа зачастую объединяют с линиями выхода, и требуемый режим работы приходится определять по состоянию специального вывода WE (Write Enable). Высокое состояние вывода WE готовит микросхему к чтению данных, а низкое - к записи. Статическая память, размещенную на одном кристалле вместе с процессором, обычно не мультиплексирует, и в этом случае содержимое одной ячейки можно читать параллельно с записью другой (линии входа и выхода ведь раздельные!).

Номера столбцов и строк поступают на декодеры столбца и строки соответственно (см. рис. 7). После декодирования расшифрованный номер строки поступает на дополнительный декодер, вычисляющий, принадлежащую ей матрицу. Оттуда он попадает непосредственно на выборщик строки, который открывает "защелки" требуемой страницы. В зависимости от выбранного режима работы чувствительный усилитель, подсоединенный к битовым линейкам матрицы, либо считывает состояние триггеров соответствующей raw-линейки, либо "перещелкает" их согласно записываемой информации.

Рис. 7. Устройство типовой микросхемы SRAM-памяти

Временные диаграммы чтения/записи

Временные диаграммы чтения/записи статической памяти практически ничем не отличаются от аналогичных им диаграмм микросхем динамической памяти (что и неудивительно, т. к. интерфейсная обвязка в обоих случаях схожа).

Цикл чтения

Цикл чтения начинается со сброса сигнала CS (Chip Select - Выбор Чипа) в низкое состояние, давая понять тем самым микросхеме, что чип "выбран" и сейчас с ним будут работать (и работать будут, и прорабатывать!).

К тому моменту, когда сигнал стабилизируется, на адресных линиях должен находиться готовый к употреблению адрес ячейки (т.е. номер строки и номер столбца), а сигнал WE должен быть переведен в высокое состояние (соответствующее операции чтения ячейки). Уровень сигнала OE (Output Enable - разрешение вывода) не играет никакой роли, т.к. на выходе пока ничего не содержится, точнее выходные линии находятся в, так называемом, высоко импедансом состоянии.

Спустя некоторое время (tAddress Access), определяемое быстродействием управляющей логики и быстротечностью переходных процессорах в инверторах, на линиях выхода появляются долгожданные данные, которые вплоть до окончания рабочего цикла (tCycle) могут быть непосредственно считаны. Обычно время доступа к ячейке статической памяти не превышает 1 - 2 нс., а зачастую бывает и меньше того!

Цикл записи

Цикл записи происходит в обратном порядке. Сначала мы выставляем на шину адрес записываемой ячейки и одновременно с этим сбрасываем сигнал WE в низкое состояние. Затем, дождавшись, когда наш адрес декодируется, усилиться и поступит на соответствующие битовые линии, сбрасываем CS в низкий уровень, приказывая микросхеме подать сигнал высокого уровня на требуемую линию row. Защелка, удерживающая триггер, откроется и в зависимости от состоянии bit-линии, триггер переключится в то или иное состояние.

Рис. 8. Временные диаграммы чтения/записи асинхронной статической памяти

Типы статической памяти

Существует как минимум три типа статической памяти: асинхронная (только что рассмотренная выше), синхронная и конвейерная. Все они практически ничем не отличаются от соответствующих им типов динамической памяти (см. статью "Устройство и принципы функционирования оперативной памяти"), поэтому, во избежание никому не нужного повторения ниже приведено лишь краткое их описание.

Асинхронная статическая память

Асинхронная статическая память работает независимо от контроллера и потому, контроллер не может быть уверен, что окончание цикла обмена совпадет с началом очередного тактового импульса. В результате, цикл обмена удлиняется по крайней мере на один такт, снижая тем самым эффективную производительность. "Благодаря" последнему обстоятельству, в настоящее время асинхронная память практически нигде не применяется (последними компьютерами, на которых она еще использовались в качестве кэша второго уровня, стали "трешки" - машины, построенные на базе процессора Intel 80386).

Синхронная статическая память

Синхронная статическая память выполняет все операции одновременно с тактовыми сигналами, в результате чего время доступа к ячейке укладывается в один-единственный такт. Именно на синхронной статической памяти реализуется кэш первого уровня современных процессоров.

Конвейерная статическая память

Конвейерная статическая память представляет собой синхронную статическую память, оснащенную специальными "защелками", удерживающими линии данных, что позволяет читать (записывать) содержимое одной ячейки параллельно с передачей адреса другой.

Так же, конвейерная память может обрабатывать несколько смежных ячеек за один рабочий цикл. Достаточно передать лишь адрес первой ячейки пакета, а адреса остальных микросхема вычислит самостоятельно, - только успевай подавать (забирать) записывание (считанные) данные!

За счет большей аппаратной сложности конвейерной памяти, время доступа к первой ячейке пакета увеличивается на один такт, однако, это практически не снижает производительности, т.к. все последующие ячейки пакета обрабатываются без задержек.

Конвейерная статическая память используется в частности в кэше второго уровня микропроцессоров Pentium-II и ее формула (см. статью "Устройство и принципы функционирования оперативной памяти Формула памяти") выглядит так: 2 - 1 - 1 - 1.

Поводом написания данной статьи послужила публикация материала американских неврологов на тему измерения емкости памяти головного мозга человека, и представленная на GeekTimes днем ранее.

В подготовленном материале постараюсь объяснить механизмы, особенности, функциональность, структурные взаимодействия и особенности в работе памяти. Так же, почему нельзя проводить аналогии с компьютерами в работе мозга и вести исчисления в единицах измерения машинного языка. В статье используются материалы взятые из трудов людей, посвятившим жизнь не легкому труду в изучении цитоархитектоники и морфогенетике, подтвержденный на практике и имеющие результаты в доказательной медицине. В частности используются данные Савельева С.В. учёного, эволюциониста, палеоневролога, доктора биологических наук, профессора, заведующего лабораторией развития нервной системы Института морфологии человека РАН.

Прежде, чем преступить к рассмотрению вопроса и проблемы в целом, мы сформулируем базовые представления о мозге и сделаем ряд пояснений, позволяющих в полной мере оценить представленную точку зрения.

Первое что вы должны знать: мозг человека — самый изменчивый орган, он различается у мужчин и женщин, расовому признаку и этническим группам, изменчивость носит как количественный (масса мозга) так и качественный (организация борозд и извилин) характер, в различных вариациях эта разница оказывается более чем двукратной.

Второе: мозг самый энергозатратный орган в человеческом организме. При весе 1/50 от массы тела он потребляет 9% энергии всего организма в спокойном состоянии, например, когда вы лежите на диване и 25% энергии всего организма, когда вы активно начинаете думать, огромные затраты.

Третье: в силу большой энергозатраты мозг хитер и избирателен, любой энергозависимый процесс невыгоден организму, это значит, что без крайней биологической необходимости такой процесс поддерживаться не будет и мозг любыми способами старается экономить ресурсы организма.

Вот, пожалуй, три основных момента из далеко не полного списка особенностей мозга, которые понадобится при анализе механизмов и процессов памяти человека.

Что же такое память? Память – это функция нервных клеток. У памяти нет отдельной, пассивной эноргонезатратной локализации, что является излюбленной темой физиологов и психологов, сторонников идеи нематериальных форм памяти, что опровергается печальным опытом клинической смерти, когда мозг перестает получать необходимое кровоснабжение и примерно через 6 минут после клинической смерти начинаются необратимые процессы и безвозвратно исчезают воспоминания. Если бы у памяти был энергонезависимый источник она могла бы восстановиться, но этого не происходит, что означает динамичность памяти и постоянные энергозатраты на ее поддержание.

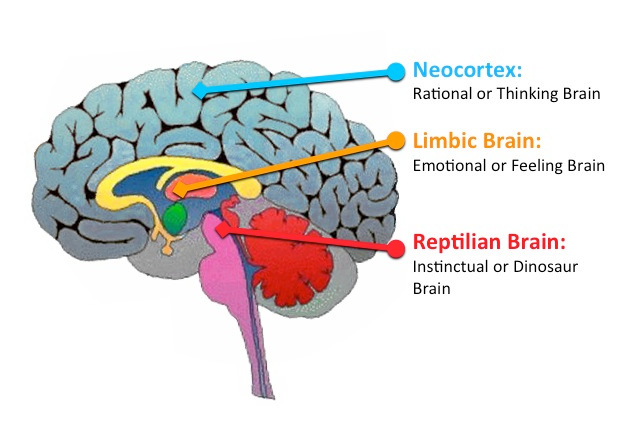

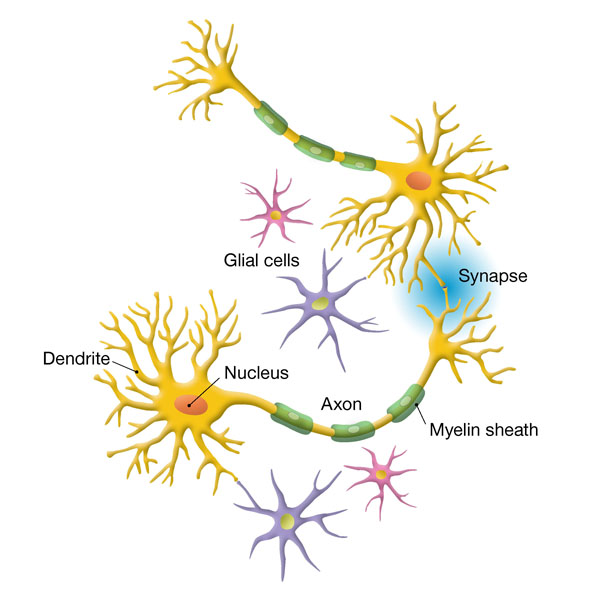

Важно знать, что нейроны, определяющие память человека, находятся преимущественно в неокортоксе. Неокортекс содержит порядка 11млрд. нейронов и в разы больше глии. (Глия – тип клеток нервной системы. Глия является средой для нейронов глиальные клетки служат опорным и защитным аппаратом для нейронов. Метаболизм глиальных клеток тесно связан с метаболизмом нейронов, которые они окружают.

Глии, связи нейронов:

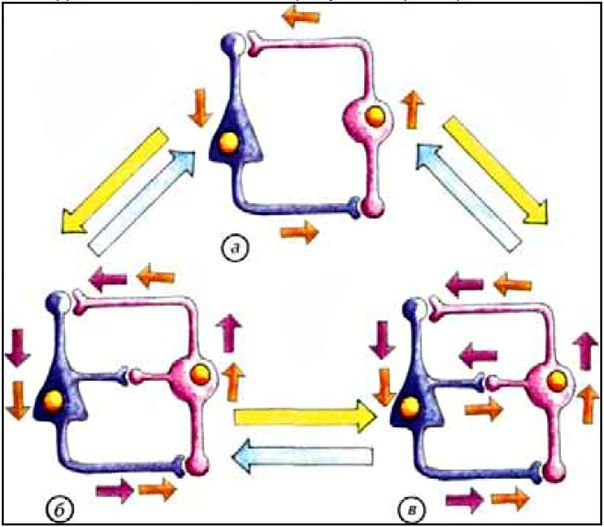

Хорошо известно, что в памяти информация хранится разное время, существуют такие понятия как долговременная и кратковременная память. События и явления быстро забываются, если не обновляются и не повторяются, что очередное подтверждение динамичности памяти. Информация определенным образом удерживается, но в отсутствии востребованности исчезает.

Как говорилось ранее, память – энергозависимый процесс. Нет энергии – нет памяти. Следствием энергозависимости памяти является нестабильность ее содержательной части. Воспоминания о прошедших событиях фальсифицируются во времени вплоть до полной неадекватности. Счета времени у памяти нет, но его заменяет скорость забывания. Память о любом событии уменьшается обратно пропорционально времени. Через час забывается ½ от всего попавшего в память, через сутки – 2/3, через месяц – 4/5.

Память мозга – вынужденная компенсаторная реакция нервной системы. Любая информация переходит во временное хранение. Поддержка стабильности кратковременной памяти и восприятия сигналов от внешнего энергетически крайне затратна, к тем же клеткам приходят новые возбуждающие сигналы и, накапливаются ошибки передачи и происходит перерасход энергетических ресурсов. Однако ситуация не так плоха, как выглядит. Нервная система обладает долговременной памятью. Зачастую она так трансформирует реальность, что делает исходные объекты неузнаваемыми. Степень модификации хранимого в памяти объекта зависит от времени хранения. Память сохраняет воспоминания, но изменяет их так, как хочется обладателю. В основе долговременной памяти лежат простые и случайные процессы. Дело в том, что нейроны всю жизнь формируют и разрушают свои связи. Синапсы постоянно образуются и исчезают. Довольно приблизительные данные говорят о том, что этот процесс спонтанного образования одного нейронного синапса может происходить у млекопитающих примерно 3-4 раза в 2-5 дней. Несколько реже происходит ветвление коллатералей, содержащих сотни различных синапсов. Новая полисинаптическая коллатераль формируется за 40-45 дней. Поскольку эти процессы происходят в каждом нейроне, вполне можно оценить ежедневную емкость долговременной памяти для любого из животных. Можно ожидать, что в коре мозга человека ежедневно будет образовываться около 800 млн. новых связей между клетками и примерно столько же будет разрушено. Долговременным запоминанием является включение в новообразованную сеть участков с совершенно не использованными, новообразованными контактами между клетками. Чем больше новых синаптических контактов участвует в сети первичной (кратковременной) памяти, тем больше у этой сети шансов сохраниться надолго.

Из выше сказанного ясно, что мозг динамическая структура, постоянно перестраивается и имеет определенные физиологические пределы, так же мозг чрезмерно энергозатратный орган. Мозг не физиологичен, а морфогенетичен, потому его активности некорректно и неправильно измерять в системах, используемых и применимых в информационных технологиях. Из за индивидуальной изменчивости мозга не представляется возможным делать какие либо выводы обобщающие различные функциональные показатели мозга человека. Математические методы так же не применимы в расчете структурного взаимодействия в работе мозга человека, из за постоянного изменения, взаимодействия и перестраивания нервных клеток и связей между ними, что в свою очередь доводит до абсурда работу американских ученых в исследовании емкости памяти головного мозга человека.

Читайте также: