Реверсивный двоичный счетчик импульсов реферат

Обновлено: 05.07.2024

Счетчик импульсов — это последовательностное цифровое устройство, обеспечивающее хранение слова информации и выполнение над ним микрооперации счета, заключающейся в изменении значения числа в счетчике на 1. По существу счетчик представляет собой совокупность соединенных определенным образом триггеров. Основной параметр счетчика — модуль счета. Это максимальное число единичных сигналов, которое может быть сосчитано счетчиком.

Счётчики используются для построения таймеров или для выборки инструкций из ПЗУ в микропроцессорах. Они могут использоваться как делители частоты в управляемых генераторах частоты (синтезаторах). При использовании в цепи ФАП счётчики могут быть использованы для умножения частоты как в синтезаторах, так и в микропроцессорах. Счетчики импульсов - непременные узлы электронных часов, микрокалькуляторов, частотомеров и многих других приборов и устройств цифровой техники. Основой их служат триггеры со счетным входом. По логике действия и функциональному назначению счетчики импульсов подразделяют на цифровые счетчики и делители частоты. Первые из них обычно называют просто счетчиками.

Простейшим одноразрядным счетчиком импульсов может быть JK-триггер и D-триггер, работающий в счетном режиме. Он считает входные импульсы по модулю 2-каждый импульс переключает триггер в противоположное состояние. Один триггер считает до двух, два соединенных последовательно считают до четырех, n триггеров - до 2 n импульсов. Результат счета формируется в заданном коде, который может храниться в памяти счетчика или быть считанным другим устройством цифровой техники-дешифратором.

Счетчики импульсов классифицируют

по модулю счета:

- двоично-десятичные;

- двоичные;

- с произвольным постоянным модулем счета;

- с переменным модулем счета;

по направлению счета:

- суммирующие;

- вычитающие;

- реверсивные;

по способу формирования внутренних связей:

- с последовательным переносом;

- с параллельным переносом;

- с комбинированным переносом;

- кольцевые.

Двоичные асинхронные счётчики

Простейший вид счётчика - двоичный может быть построен на основе T-триггера. T-триггер изменяет своё состояние на прямо противоположное при поступлении на его вход синхронизации импульсов. Для реализации T-триггера можно воспользоваться универсальным D-триггером с обратной связью, как это показано на рисунке 1.

Рис. 1 - Построение счетного T-триггера на универсальном D-триггере.

В этой схеме, так как на вход триггера подается сигнал с инверсного выхода микросхемы, при поступлении тактовых импульсов сигнал на выходе будет меняться с 0 на 1 и наоборот. Временная диаграмма сигналов на входе и выходах триггера приведена на рисунке 2.

Рис. 2 - Временная диаграмма работы T-триггера

Таким образом у нас появился счётчик, считающий до двух. Обычно требуется посчитать количество импульсов, которое больше двух. В этом случае можно использовать выходной сигнал счетного триггера как входной сигнал для следующего триггера, то есть соединить триггеры последовательно. Так можно построить любой счётчик, считающий до максимального числа, кратного степени два.

Схема счётчика, позволяющего посчитать до 16 импульсов приведена на рисунке 3, а временная диаграмма сигналов на входе и выходах этого счётчика приведена на рисунке 4.

Рис. 3 - Схема четырёхразрядного счётчика, построенного на универсальных D-триггерах.

Рис. 4 - Временная диаграмма четырёхразрядного счётчика.

Как видно из временной диаграммы, на выходах этого двоичного счётчика последовательно появляются цифры от 0 до 15. Естественно эти цифры записаны в двоичном виде. Они приведены в таблице 1. То есть, при поступлении на счётный вход очередного импульса, содержимое счётчика увеличивается на 1. Поэтому такие счётчики получили название суммирующих двоичных счётчиков.

| Номер входного импульса | Q3 | Q2 | Q1 | Q0 |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 2 | 0 | 0 | 1 | 0 |

| 3 | 0 | 0 | 1 | 1 |

| 4 | 0 | 1 | 0 | 0 |

| 5 | 0 | 1 | 0 | 1 |

| 6 | 0 | 1 | 1 | 0 |

| 7 | 0 | 1 | 1 | 1 |

| 8 | 1 | 0 | 0 | 0 |

| 9 | 1 | 0 | 0 | 1 |

| 10 | 1 | 0 | 1 | 0 |

| 11 | 1 | 0 | 1 | 1 |

| 12 | 1 | 1 | 0 | 0 |

| 13 | 1 | 1 | 0 | 1 |

| 14 | 1 | 1 | 1 | 0 |

| 15 | 1 | 1 | 1 | 1 |

Существуют готовые микросхемы асинхронных двоичных счётчиков. Классическим примером такого счётчика является микросхема 555ИЕ5. Её изображение на принципиальных схемах приведено на рисунке 5. В этой микросхеме существует вход обнуления микросхемы R, который позволяет записать во все триггеры счётчика нулевое значение.

Рис. 5 - Четырёхразрядный двоичный счётчик.

Двоичные вычитающие асинхронные счётчики

Счётчики могут не только увеличивать своё значение на единицу при поступлении на вход импульсов но и уменьшать его. Такие счётчики получили название вычитающих счётчиков. Для реализации вычитающего счётчика достаточно чтобы T-триггер срабатывал по переднему фронту входного сигнала. Это можно осуществить инвертированием этого сигнала. В схеме, приведенной на рисунке 6, для реализации вычитающего счётчика сигнал на входы последующих триггеров подаются с инверсных выводов предыдущих триггеров.

Рис. 6 - Схема четырёхразрядного двоичного вычитающего счётчика на универсальных D-триггерах.

Временная диаграмма этого счётчика приведена на рисунке 7. По этой диаграмме видно, что при поступлении на вход счётчика первого же импульса на выходах появляется максимально возможное для четырёхразрядного счётчика число 15. При поступлении следующих импульсов содержимое счётчика уменьшается на единицу. Этот процесс продолжается до тех пор, пока содержимое счётчика не станет вновь равно 0.

Рис. 7 - Временная диаграмма четырёхразрядного вычитающего счётчика.

Все возможные состояния сигналов на выходах счётчика при поступлении импульсов на вход микросхемы приведены в таблице 2.

| Номер входного импульса | Q3 | Q2 | Q1 | Q0 |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

| 2 | 1 | 1 | 1 | 0 |

| 3 | 1 | 1 | 0 | 1 |

| 4 | 1 | 1 | 0 | 0 |

| 5 | 1 | 0 | 1 | 1 |

| 6 | 1 | 0 | 1 | 0 |

| 7 | 1 | 0 | 0 | 1 |

| 8 | 1 | 0 | 0 | 0 |

| 9 | 0 | 1 | 1 | 1 |

| 10 | 0 | 1 | 1 | 0 |

| 11 | 0 | 1 | 0 | 1 |

| 12 | 0 | 1 | 0 | 0 |

| 13 | 0 | 0 | 1 | 1 |

| 14 | 0 | 0 | 1 | 0 |

| 15 | 0 | 0 | 0 | 1 |

Для тех, кто привык работать с реально выпускаемыми микросхемами, следует обратить внимание, что для примера были использованы D-триггеры, работающие по заднему фронту. Микросхемы 1533ТМ2 (два D-триггера в одном корпусе) срабатывают по переднему фронту, поэтому схемы для суммирующего и вычитающего счётчика поменяются местами.

Недвоичные счётчики с обратной связью.

Если посмотреть на временную диаграмму сигналов на выходах двоичного счётчика, приведённого на рисунке 4, то можно увидеть, что частота сигналов на его выходах будет уменьшаться в два раза по отношению к предыдущему выходу. Это позволяет использовать счетчики в качестве делителей частоты входного сигнала. Эти делители частоты могут быть использованы в устройствах формирования высокостабильных генераторов частоты (синтезаторов частот). Частоты могут быть использованы либо для синхронизации цифровых устройств (в том числе и микропроцессоров) либо в качестве задающих генераторов радиоприёмных и радиопередающих устройств.

При использовании цифровых счётчиков в качестве устройств формирования опорных частот может потребоваться обеспечить коэффициент деления, отличающийся от степени числа 2. Ещё одна ситуация, когда необходимо применять недвоичные счётчики возникает при отображении информации, записанной в счётчике. Человек, который работает с электронной техникой, привык работать с десятичной системой счисления, поэтому возникает необходимость отображать хранящееся в счётчике число в непосредственно десятичном виде. Это намного проще сделать, если и счет вести сразу в двоично-десятичном коде. Иначе для индикации потребуется перекодировать информацию из двоичного в двоично-десятичный код.

Построить недвоичный счётчик можно из двоичного за счёт выбрасывания лишних комбинаций единиц и нулей. Это может быть осуществлено при помощи обратной связи. Для этого при помощи дешифратора определяется число, соответствующее коэффициенту счёта, и сигнал с выхода этого дешифратора обнуляет содержимое двоичного счётчика. В качестве примера на рисунке 8 приведена схема двоично-десятичного счётчика.

Рис. 8 - Схема десятичного счётчика, построенного на основе двоичного счётчика.

В этой схеме дешифратор построен на двухвходовой схеме "2И", входящей в состав микросхемы двоичного счётчика. Дешифратор декодирует число 10 (1010 в двоичной системе счисления). В соответствии с принципами построения схем по произвольной таблице истинности для построения дешифратора требуется ещё два инвертора, подключённых к выходам 1 и 4. Однако после сброса счётчика числа, большие 10 никогда не смогут появиться на выходах микросхемы. Поэтому схема дешифратора упрощается и вместо четырёхвходовой схемы "4И" можно обойтись двухвходовой схемой. Инверторы тоже оказываются лишними.

При использовании счётчиков в качестве делителей частоты тоже можно воспользоваться обратной связью. Приведём в качестве примера схему делителя частоты на 1000. При разработке делителя прежде всего определим сколько потребуется микросхем двоичных счётчиков. Для этого определим степень числа 2, при которой число M=2 n будет больше требуемого числа 1000. Это будет число 10. При возведении основания системы счисления 2 в 10 степень получится число 1024. То есть, при использовании для построения делителя частоты непосредственно триггеров, достаточно будет десяти триггеров. Однако обычно для построения делителей частоты используют готовые двоичные счётчики, поэтому определим необходимое количество микросхем двоичных счётчиков. При использовании четырёхразрядных двоичных счётчиков достаточно будет трёх микросхем, так как в трёх микросхемах будет 3*4=12 триггеров, что заведомо больше минимального числа триггеров.

Следующим этапом построения делителя частоты будет перевод коэффициента деления 1000 в двоичное представление. Десятичное число 1000 в двоичном виде будет выглядеть как 0011 1110 1000. В этом числе шесть единиц, поэтому для построения делителя будет достаточно шестивходовой схемы "И". Однако такие схемы не выпускаются, поэтому воспользуемся микросхемой "8И-НЕ". Неиспользуемые входы этой микросхемы подключим к питанию. Ненужную нам инверсию сигнала скомпенсируем дополнительным инвертором. Получившаяся схема делителя на 1000 приведена на рисунке 9.

Рис. 9 - Схема делителя на 1000, построенного на основе трёх двоичных счётчиков.

При использовании счётчиков в составе синтезаторов частот может потребоваться формирование целого диапазона частот. В этом случае делитель должен обладать возможностью изменения коэффициента деления (ДПКД). При использовании обратной связи для этого потребуется полный дешифратор и переключатели его выходов на вход сброса счётчика. Схема при этом получается сложной, а управление неудобным. Пример двухразрядного делителя с переменным коэффициентом деления (ДПКД), построенного на десятичных счётчиках приведён на рисунке 4.

Рис. 10 - Схема делителя с переменным коэффициентом деления с максимальным коэффициентом деления 100,

построенного на основе двух десятичных счётчиков.

Двоичные реверсивные счетчики имеют переходы в двух направлениях: в прямом (при счете суммируемых сигналов U + ) и в обратном (при счете вычитаемых сигналов U - ). Текущее значение разности подсчитанных импульсов определяется из соотношения

= N - Nn

Где N— значение кода на прямых выходах триггеров счетчика;

Nn — предварительно записанное в счетчик начальное число.

В процессе счета должно выполняться условие ≤ Nn + ≤ 2 n -1.

Различают одноканальные и двухканальные реверсивные счетчики.

В одноканальных реверсивных счетчиках суммируемые U + и вычитаемые U - сигналы поочередно поступают на общий счетный вход, а направление счета задается направлением цепей межразрядных переносов или заемов. Для переключения межразрядных связей в одноканальном реверсивном счетчике требуются дополнительные управляющие сигналы.

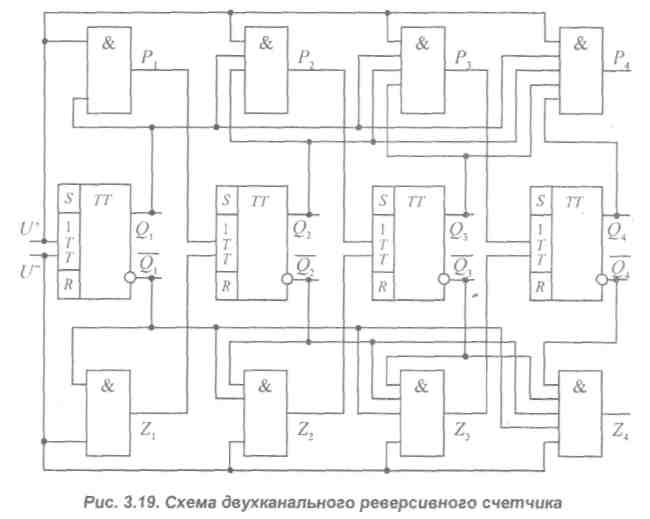

Двухканальные реверсивные счетчики имеют два счетных входы: один для суммируемых импульсов U + , другой — для вычитаемых U - . Переключение цепей межразрядных связей осуществляется автоматически счетными сигналами: для переносов — импульсами U + , для заема — импульсами U - .

Схема одноканального трехразрядного двоичного реверсивного счетчика показана на рис. 5.17.

Рисунок 5.17-Схема одноканального реверсивного счетчика

Межразрядные связи коммутируются с помощью логических элементов И-ИЛИ.

Для задания направления счета используют дополнительный RS-триггер: с его прямого выхода снимается сигнал управления сложением YСл (включает цепи переноса), а с инверсного выхода — сигнал управления вычитанием YВч (включает цепи заема).

На выходах элементов И-ИЛИ (которые называются "схемы реверса") вырабатывается сигнал Тi для счетных входов старших разрядов:

Ti = YД Qi YВ i = 1,2,3. n.

Таким образом, если управляющий RS-триггер находится в состоянии "1", то счетчик реализует режим прямого счета входных импульсов (то есть суммирование), противном случае — обеспечивает режим обратного счета (вычитание). В обоих ежимах работы триггеры переключаются асинхронно.

Схема двухканального четырехразрядного двоичного реверсивного счетчика оказана на рис. 5.18.

Счетные Т-входы в триггерах внутренне связаны схемой ИЛИ. Суммирующие импульсы U + поступают на счетный вход первого (младшего) разряда счетчика и одновременно — на входы всех вентилей в цепи параллельного переноса.

При этом формируются импульсы межразрядных переносов на основе логических выражений:

Вычитаемые импульсы U - поступают на счетный вход первого разряда счетчика и одновременно на входы всех вентилей в цепи параллельных заемов. При этом формируются импульсы межразрядных заемов на основе следующих логических выражений:

Z1=U - ; Z2=U - ; Z3=U - Z4=U -

Таким образом, в двухканальных реверсивных счетчиках направление счета непосредственно задается суммируемыми U + или вычитаемыми U - импульсами. Запрещается одновременное поступления на входы двухканального реверсивного счетчика суммируемых и вычитаемых импульсов.

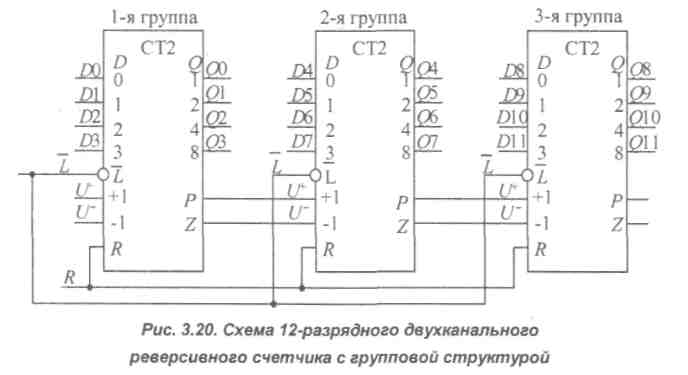

На практике с учетом схемотехнических возможностей микросхем средней степени интеграции многоразрядные реверсивные счетчики строятся в виде групповой структуры. При этом каждая группа представляется, например, микросхемой четырехразрядного реверсивного счетчика с параллельными переносами и заемами. Между группами могут бути образованы последовательные или параллельные связи.

Схема 12-разрядного двухканального реверсивного счетчика групповой структуры с последовательными переносами между группами (микросхемы КР1533ИЕ7) показана на рис. 5.19; СТ2 — функция двоичного счетчика.

Рисунок 5.19-Схема 12-разрядного двухканального реверсивного счетчика с групповой структурой

Микросхема КР1533ИЕ7 — это двоичный четырехразрядный реверсивный синхронный счетчик, имеющий следующие режимы работы:

• параллельная загрузка начальных данных D3-D0 при = 0 ;

• суммирование импульсов U + по входу "+1";

• вычитание импульсов U - по входу "-1";

• сброс в начальное состояние сигналом лог. 1 на R-входе.

Информация считывается с выходов Q11 -Q0 счетчика. Суммируемые импульсы U + в счетчике с групповой структурой поступают на вход прямого счета "+1" первой младшей группы. Для другой группы сигналы переноса формируются при условии Р = U + Q1Q2Q3Q1

Вычитаемые импульсы U + поступают на вход обратного счета "-1". Для второй группы сигналы заема вырабатываются при условии Z = U - Q3Q2Q1Q0

Аналогично строятся связи и между старшими группами.

Длительность импульсов на счетных входах должна быть не меньше 20 нc, а максимальная частота счета не должна превышать 30 МГц.

ИССЛЕДОВАНИЕ РЕВЕРСИВНОГО СЧЕТЧИКА

1. ЦЕЛЬ РАБОТЫ

Целью работы является:

- теоретическое изучение принципа работы счетчиков и регистров;

- экспериментальное исследование счетчика-регистра на интегральных микросхемах.

2. ОСНОВНЫЕ ТЕОРЕТИЧЕСКИЕ ПОЛОЖЕНИЯ

Регистры и счетчики относятся к разряду цифровых устройств и являются одним из

наиболее распространенных элементов вычислительной техники. Они широко

используются для построения устройств ввода, вывода и хранения информации, а

также для выполнения некоторых арифметических и логических операций.

Для построения счетчиков и регистров используются синхронные триггеры,

переключение которых происходит только при наличии синхронизирующего сигнала

(синхроимпульса ) на входе С. Наиболее часто для построения регистров и

счетчиков используется универсальный Д - триггер, имеющий специальный

информационный вход Д, и динамический вход С (рис.1).

2.1. Устройство, называемое регистром, служит в основном для хранения чисел в

двоичном коде при выполнении над ними различных арифметических и логических

операций. С помощью регистров выполняютоя такие действия над числами, как

передача их из одного устройства в другое, арифметический и логический сдвиг в

сторону младших или старших разрядов, преобразование кода из последовательного в

параллельный и наоборот и т.д. Функциональная схема и условно - графическое

обозначение регистра параллельного типа, собранного на универсальных

Д-триггерах, приведена на рис.2 .

По сигналу на входе С информация, поступившая на входы DОёDЗ, записывается в

регистр и хранится в нем до тех пор, пока не произойдет запись другой

информации, либо не поступит сигнал на вход R, обнуляющий регистр.

Функциональная схема и условно-графическое обозначение регистра сдвига

представлены на рис.З.

Последовательный информационный код поступит на вход D регистра. Импульс команды

сдвига С подается одновременно на синхронизирующие входы всех триггеров регистра

и переводит каждый триггер в состояние, в котором находился триггер предыдущего

разряда. Таким образом, каждый импульс команды сдвига "продвигает" записываемое

число на один разряд вправо.

2.2. Устройство, называемое счетчиком, предназначено для подсчета числа

поступающих на вход сигналов ( импульсов ) в произвольной системе счисления.

Двоичные счетчики строятся на основе триггеров, работающих в счетном режиме ( Т

- триггер или счетный триггер).

Счетный триггер может быть получен из универсального D - триггера путем

соединения его инверсного выхода 0 со входом D.

Счетный триггер и эпюры сигналов, поясняющие его работу, представлены на рис.4.

У счетного триггера состояние выхода изменяется на противоположное при

поступлении на вход С каждого очередного счетного импульса.

Функциональная схема и условнографическое обозначение двоичного счетчика с

коэффициентом пересчета 23 представлена на рис.5.

Каждый поступающий на вход счетчика импульс перебрасывает первый триггер в

противоположное состояние (рис.6). Сигнал с инверсного выхода предыдущего

триггера является входным сигналом для последующего и, таким образом, комбинация

сигналов на выходах Q1, Q2, Q3 будет соответствовать числу поступивших на вход

счетчика импульсов, представленному в двоичном коде. Счетчик данного типа

называется асинхронным счетчиком.

Если на счетный вход каждого последующего триггера счетчика подавать сигнал с

прямого выхода предыдущего триггера, то счетчик будет производить операцию

вычитания. Счетчики, способные выполнять функции сложения и вычитания,

называются реверсивными.

Для построения счетчика с требуемым коэффициентом пересчета М, отличным от

величины 2N (N - число двоичных разрядов счетчика), используется принудительный

сброс счетчика в исходное состояние при достижении счетчиком числа М. Пример

такого счетчика с М=9 (М=10012) представлен на рис.7.

Счетчики представляют собой последовательностые цифровые устройства и предназначены для выполнения операций счета и хранения кода числа подсчитанных импульсов. Существуют различные схемы счетчиков, отличающихся назначением, типом используемых триггеров, организацией связи между ними, порядком смены состояний. По порядку изменения состояний счетчики бывают с естественным и произвольным порядком счета. В первых значение кода каждого последующего состояния счетчика отличается на единицу от кода предыдущего состояния. В счетчиках с произвольным порядком счета значения кодов соседних состояний могут отличаться более чем на единицу. Счетчики также подразделяются на простые и реверсивные. Простые счетчики делятся на суммирующие и вычитающие. В суммирующих счетчиках код последующего состояния имеет большее значение, чем код предыдущего состояния, а в вычитающих – меньшее значение. Реверсивные счетчики могут работать как в режиме суммирования, так и в режиме вычитания.

Основными параметрами счетчика являются:

- модуль счета или коэффициент пересчета Ксч;

- быстродействие счетчика.

Модуль счета Ксч характеризует число устойчивых состояний счетчика, т. е. предельное число импульсов, которое может быть им сосчитано. После поступления Ксч входных импульсов счетчик возвращается в исходное состояние. Такие счетчики называются также делителями на число, равное Ксч.. По модулю счета счетчики подразделяются на двоичные, у которых Ксч=2 m , и недвоичные, у которых Ксч?2 m , где m – положительное целое число.

Быстродействие счетчика в свою очередь определяется двумя величинами:

- разрешающей способностью , т.е. минимальным допустимым интервалом времени между подачей двух входных импульсов, при котором не происходит потеря счета;

- временем установки tуст кода счетчика, т.е. интервалом времени между моментом поступления входного сигнала и моментом завершения перехода счетчика в новое устойчивое состояние.

Поскольку счетчики представляют собой класс ПЦУ, то и синтез их целесообразно выполнять на основе базовых элементов ПЦУ, т.е. триггерах. Количество триггеров для двоичных счетчиков определяется формулой

Для недвоичных счетчиков количество триггеров следует выбирать из условия

где [log2Kсч]- двоичный логарифм заданного коэффициента пересчета, округленный до ближайшего (большего) целого числа.

Двоичные счетчики. Начнем с двоичных счетчиков. Для их построения можно использовать различные типы триггеров. Наиболее удобным является триггер Т-типа (счетный триггер), который осуществляет подсчет импульсов по модулю 2. Такой триггер по сути дела является простейшим счетчиком с Ксч=2. Соединив несколько счетных триггеров определенным образом, можно получить схему многоразрядного счетчика. Если в качестве базовых используются Т-триггеры с прямым динамическим счетным входом, то для построения трехразрядного суммирующего двоичного счетчика, их необходимо объединить так, как это показано на рис. 5.14,а . Срабатывание всех триггеров происходит по переднему фронту счетного импульса. Поэтому, чтобы реализовать операцию суммирования, необходимо на триггеры Т2 и Т3 информацию подавать с инверсных выходовпредыдущих триггеров. Временная диаграмма работы счетчика показана на рис. 5.14,б .

Состояния выходов Q1, Q2 и Q3 сгруппируем в зависимости от номера счетного импульса в таблице 5.1 . Из таблицы очевидно, что двоичный код, задаваемый логическими состояниями выходов счетчика соответствует порядковому номеру входного счетного импульса С. При подаче последнего восьмого импульса счетчик возвращается в исходное состояние, после чего процесс повторяется. Модуль счета, таким образом, Ксч=2 3 =8.

Рис. 5.14.Структурная схема и временная диаграмма работы трехразрядного двоичного суммирующего счетчика на основе Т-триггеров с прямым динамическим счетным входом.

Суммирующий счетчик можно построить и на базе Т-триггеров с инверсным динамическим счетным входом. При этом, поскольку срабатывание триггеров происходит по заднему фронту счетного импульса, нет необходимости задействовать инверсные выходы этих триггеров. Сигнал на вход каждого последующего триггера необходимо подавать с прямого выхода предыдущего триггера ( рис. 5.15,а ). При этом необходимо учитывать, что срабатывание всего счетчика будет происходить по заднему фронту счетного импульса С, как это показано на временной диаграмме рис. 5.15,б .

Рис. 5.15. Структурная схема и временная диаграмма работы трехразрядного двоичного суммирующего счетчика на основе Т-триггеров с инверсным динамическим счетным входом.

Для выполнения операции вычитания достаточно изменить в электрических связях соответствующих схем используемые выходы триггеров на выходы с обратными логическими уровнями, либо использовать триггеры с входами обратного типа динамического управления. Если вычитающий счетчик реализуется на базе Т-триггеров с прямым динамическим входом, то сигналы на входы последующих триггеров, в противоположность схемы рис. 5.14,а , необходимо подавать с прямых выходов предыдущих триггеров ( рис. 5.16,а ). Временная диаграмма работы счетчика с такой структурой приведена на рис. 5.16,б . Из временной диаграммы видно, что с каждым последующим счетным импульсом выходной код уменьшается на единицу (декрементируется). С последним восьмым импульсом счетчик возвращается в исходное состояние.

Рис. 5.16. Структурная схема и временная диаграмма работы трехразрядного двоичного вычитающего счетчика на основе Т-триггеров с прямым динамическим счетным входом.

Рис. 5.17.Структурная схема трехразрядного двоичного реверсивного счетчика.

В рассмотренных счетчиках срабатывание триггеров происходит поочередно друг за другом, т.е. последовательно. Такие счетчики называются асинхронными. Их недостаток состоит в том, что увеличивается общее время установления tуст с увеличением числа триггеров. Кроме того, появление промежуточных комбинаций может привести к ложному срабатыванию дешифратора, если такой есть в структуре ПЦУ. Для устранения этого недостатка используются счетчики, у которых все триггеры срабатывают одновременно. Такие счетчики получили название синхронных счетчиков. Идея синхронного счетчика заключается в построении внешней комбинационной схемы, формирующей сигналы, согласно которым будет происходить одновременное переключение только части триггеров в зависимости от текущего выходного кода. Причем эти сигналы должны быть сформированы до поступления очередного счетного импульса. Счетный импульс должен поступать на все триггеры одновременно. Для этих целей необходимо использовать тактируемые Т-триггеры, входы синхронизации которых объединяются в общую шину. На тактовые Т-входы каждого триггера подаются заранее сформированные сигналы переноса с комбинационной схемы.

Анализ смены состояний суммирующего счетчика показывает, что если значение младшего разряда меняется каждый раз с приходом входного сигнала, то в остальных разрядах значение будет меняться на противоположное только в тех случаях, когда до этого во всех предыдущих разрядах были единицы. Для этого единичный входной сигнал должен поступать на вход триггера только в том случае, если триггеры во всех предыдущих разрядах находятся в единичном состоянии. Задачу формирования входного сигнала для каждого последующего триггера выполняет логический элемент И ЛЭ1 (ЛЭ2), на входы которого подаются сигналы со всех выходов предыдущих триггеров ( рис. 5.18 ). Срабатывание всех триггеров происходит одновременно по общему сигналу синхронизации С, который является счетным импульсом для всего счетчика. Изображенная на рисунке структура называется счетчиком с параллельным переносом, поскольку сигналы на все элементы И, формирующие единичные переносы, подаются с выходов триггеров одновременно в параллельном виде. В исходном состоянии на выходах всех триггеров присутствуют логические нули. С поступлением каждого счетного импульса выходные коды начинают увеличиваться на единицу (инкрементироваться). Задержка в такой схеме равна времени срабатывания одного триггера.

Рис. 5.18. Структурная схема четырехразрядного суммирующего счетчика с параллельным переносом.

Чтобы синтезировать схему вычитающего счетчика, необходимо использовать не прямые, а инверсные выходы триггеров. Таким образом, в исходном состоянии все триггеры будут иметь на инверсных выходах логические единицы. С началом счета выходные коды будут уменьшаться (декрементироваться). Используя принцип коммутации прямых или инверсных выходов триггеров, можно также реализовать реверсивный счетчик с параллельным переносом.

Недостатком счетчиков с параллельным переносом является необходимость использования в случае увеличения разрядности счетчика элементов И с большим числом входов. При этом выходы триггеров должны обладать высокой нагрузочной способностью. Поэтому многоразрядные счетчики строят по групповому принципу. Согласно этому принципу, весь счетчик структурно реализуется путем соединения отдельных групп небольшой разрядности с параллельным переносом внутри этих групп. Сигнал переноса из очередной группы формируется элементом И, объединяющим выходы всех триггеров данной группы. Сформированный сигнал переноса предыдущей группы подается на счетный вход последующей группы. Общая задержка такого счетчика определяется суммой задержек каждой группы.

Другой вариант структуры синхронного счетчика – это структура со сквозным переносом. Согласно этой структуре, перенос формируется только из единичных результатов соседних разрядов. Для этих целей достаточно использовать только двухвходовые элементы И при любой разрядности счетчика ( рис. 5.19 ). Перенос между разрядами осуществляется через каждый элемент И (ЛЭ1 и ЛЭ2) в их последовательной структуре. Отсюда следует, что общее время срабатывания всего счетчика определяется временем срабатывания одного триггера и суммарным временем задержки последовательной цепи логических элементов И. Выигрыш по быстродействию в такой структуре осуществляется за счет меньшего времени срабатывания одного логического элемента по сравнению со временем срабатывания одного триггера. При достаточно большой разрядности счетчика, время задержки во всех элементах И может оказаться значительным и сравняться с временем срабатывания одного триггера.

Рис. 5.19. Структурная схема четырехразрядного суммирующего счетчика со сквозным переносом.

Недвоичные счетчики. Недвоичные счетчики имеют Ксч ? 2 m . Принцип их построения заключается в исключении некоторых устойчивых состояний обычного двоичного счетчика. Избыточные состояния исключаются с помощью обратных связей внутри счетчика. Как было показано ранее, количество триггеров в недвоичном счетчике есть округленное до большего целого числа значение mнедв=[log2Kсч]. Поэтому, если задействовать все возможные состояния m триггеров, то счетчик окажется двоичным. Организуя обратные связи в двоичном счетчике таким образом, чтобы определенными выходными кодовыми комбинациями осуществлять либо его обнуление, либо установку в состояние, отличное от очередного, реализуется недвоичный счетчик с произвольным Ксч. Часть состояний двоичного счетчика, таким образом, пропускаются.

Наибольший интерес среди недвоичных счетчиков представляют двоично-десятичные счетчики с Ксч=10, которые строятся на основе четырех счетных триггеров. Важность этого класса счетчиков заключается в том, что с их помощью легко может быть осуществлен вывод содержимого счетчика в десятичном коде. Действительно каждый двоично-десятичный счетчик имеет десять устойчивых состояний и соответствует одному разряду десятичной системы счисления.

Читайте также: