Работа микропроцессора с памятью кратко

Обновлено: 02.07.2024

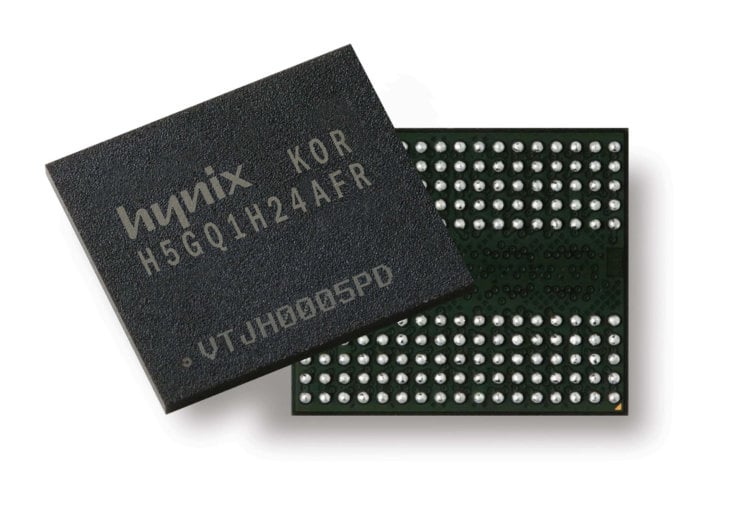

Для хранения информации в микропроцессорных системах используются запоминающие устройства на основе полупроводниковых материалов, а также магнитные и оптические внешние носители. Внутренняя память компьютера представлена в виде отдельных интегральных микросхем (ИМС) собственно памяти и элементов, включенных в состав других ИМС, не выполняющих непосредственно функцию хранения программ и данных - это и внутренняя память центрального процессора, и видеопамять, и контроллеры различных устройств.

Для создания элементов запоминающих устройств, в основном, применяют СБИС со структурой МДП (металл-диэлектрик-полупроводник) на основе кремния (в связи с тем, что в качестве диэлектрика чаще всего используют его оксид Si02, то их обычно называют МОП (металл-оксид-полупроводник) структурами).

Для функционирования компьютерной системы необходимо наличие как оперативного запоминающего устройства (ОЗУ), так и постоянного запоминающего устройства (ПЗУ), обеспечивающего сохранение информации при выключении питания. ОЗУ может быть статическим и динамическим, а ПЗУ однократно или многократно программируемым.

Степень интеграции, быстродействие, электрические параметры ЗУ при записи и хранении информации, помехоустойчивость, долговременная стабильность, стабильность к внешним неблагоприятным факторам при функционировании и т.д. зависят от физических принципов работы приборов, применяемых материалов при производстве ИМС и параметров технологических процессов при их изготовлении.

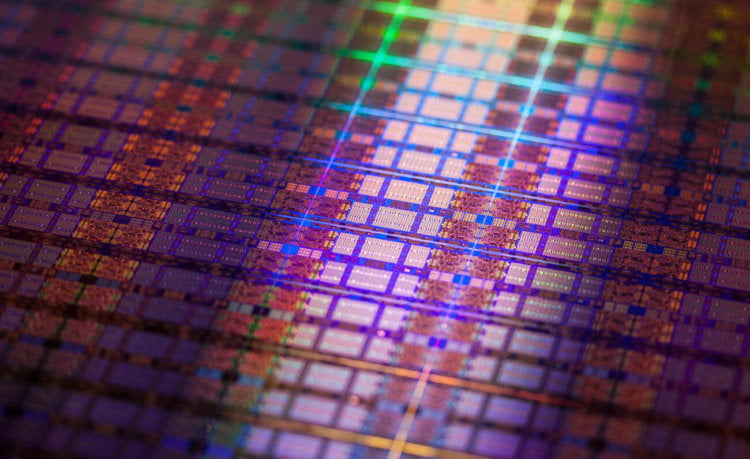

На развитие микропроцессорной техники решающее значение оказывает технология производства интегральных схем.

Полупроводниковые интегральные микросхемы подразделяются на биполярные ИМС и МОП схемы, причем первые - более быстродействующие, а вторые имеют большую степень интеграции, меньшую потребляемую мощность и меньшую стоимость. Цифровые микросхемы могут по идеологии, конструкторскому решению, технологии относится к разным семействам, но выполнять одинаковую функцию, т.е. быть инвертором, триггером или процессором. Наиболее популярными семействами можно назвать у биполярных ИМС: ТТЛ (транзисторно-транзисторная логика), ТТЛШ (с диодами Шоттки), ЭСЛ (эмиттерно-связанная логика); у МДП: n-МОП и КМОП.

Базовым материалом для изготовления ИМС является кремний. Несмотря на то, что он не обладает высокой подвижностью носителей заряда (mn=1500 см2/Вс), а значит, приборы на его основе теоретически будут уступать по быстродействию приборам на основе арсенида галлия GaAs, однако система Si-SiO2 существенно более технологична. С другой стороны, приборы на кремниевой основе кремний-оксид кремния) обладают совершенной границей раздела Si-SiO2, химической стойкостью, электрической прочностью и другими уникальными свойствами.

Технологический цикл производства ИМС включает:

- эпитаксиальное наращивание слоя на подготовленную подложку;

- наращивание слоя SiO2 на эпитаксиальный слой;

- нанесение фоторезиста, маскирование и вытравливание окон в слое;

- легирование примесью путем диффузии или имплантацией;

- аналогично повторение операций для подготовки других легиро-ванных областей;

- повторение операций для создания окон под контактные площадки;

- металлизацию всей поверхности алюминием или поликремнием;

- повторение операций для создания межсоединений;

- удаление излишков алюминия или поликремния;

- контроль функционирования;

- помещение в корпус;

- выходной контроль.

Наиболее критичным для увеличения степени интеграции является процесс литографии, т.е. процесс переноса геометрического рисунка шаблона на поверхность кремниевой пластины. С помощью этого рисунка формируют такие элементы схемы, как электроды затвора, контактные окна, металлические межкомпонентные соединения и т.п. На первой стадии изготовления ИМС после завершения испытаний схемы или моделирования с помощью ЭВМ формируют геометрический рисунок топологии схемы. С помощью электронно-лучевого устройства или засветки другим способом топологический рисунок схемы последовательно, уровень за уровнем можно переносить непосредственно на поверхность кремниевой пластины, но чаще на фоточувствительные стеклянные пластины, называемые фотошаблонами. Между переносом топологического рисунка с двух шаблонов могут быть проведены операции ионной имплантации, загонки, окисления и металлизации. После экспонирования пластины помещают в раствор, который проявляет изображение в фоточувствительном материале - фоторезисте.

Увеличивая частоту колебаний световой волны, можно уменьшить ширину линии рисунка, т. е. сократить размеры интегральных схем. Но возможности этой технологии ограничены, поскольку рентгеновские лучи трудно сфокусировать. Один из вариантов - использовать сам свет в качестве шаблона (так называемое позиционирование атомов фокусированным лазерным лучом). Этим способом, осветив двумя взаимно перпендикулярными лазерными пучками, можно изготовить решетку на кремниевой пластине из хромированных точек размером 80 нм. Сканируя лазером поверхность для создания произвольного рисунка интегральных наносхем, теоретически можно создавать схемы с шириной линии рисунка в 10 раз меньшей, чем сегодняшние. Второе ограничение при литографии накладывает органическая природа фоторезиста. Путь ее решения - применение неорганических материалов, например, оксидов ванадия.

Физические процессы, протекающие в изделиях микроэлектроники (и в микросхемах памяти тоже), технология изготовления и конструктивные особенности ИМС высокой степени интеграции могут влиять на архитектуру и методы проектирования ЭВМ и систем. Естественно, уменьшение геометрических размеров транзисторов приводит к увеличению электрических полей, особенно в районе стока. Это может привести к развитию лавинного пробоя и, как следствие, к изменению выходной ВАХ МОП транзистора:

- включению паразитного биполярного транзистора (исток-подложка-сток);

- неравномерному заряжению диэлектрика у стока;

- деградации приповерхностной области полупроводника;

- пробою диэлектрика.

Поэтому необходимо уменьшение напряжения питания СБИС до 3.6, 3.3, 3 В и т.п., при этом известно, что блок питания компьютера обеспечивает обычно напряжения +5В, +12В, -12В.

Однако инжекция и заряжение диэлектрика не всегда процесс отрицательный или паразитный. Уменьшение напряжения записи информационного заряда в репрограммируемых ЗУ ниже 12 В позволяет их программировать внутри микропроцессорной системы, а не специальным устройством (программатором). Тогда для разработчика открываются большие возможности для программирования не только адреса микросхем контроллера или адаптера в пространстве устройств ввода/вывода или номера прерывания, но и творить необходимое устройство самому (если иметь такую ИМС). Однако отметим, что кроме "хозяина" это может сделать и компьютерный вирус, который будет, естественно, разрушать, а не созидать что-либо.

Основные характеристики полупроводниковой памяти

Полупроводниковая память имеет большое число характеристик и параметров, которые необходимо учитывать при проектировании систем:

1. Емкость памяти определяется числом бит хранимой информации. Емкость кристалла обычно выражается также в битах и составляет 1024 бита, 4 Кбит, 16 Кбит, 64 Кбит и т.п. Важной характеристикой кристалла является информационная организация кристалла памяти MxN, где M - число слов, N - разрядность слова. Например, кристалл емкостью 16 Кбит может иметь различную организацию: 16 Кx1, 4 Кx2 Кx8. При одинаковом времени обращения память с большей шириной выборки обладает большей информационной емкостью.

2. Временные характеристики памяти.

Время доступа - временной интервал, определяемый от момента, когда центральный процессор выставил на шину адреса адрес требуемой ячейки памяти и послал по шине управления приказ на чтение или запись данных, до момента осуществления связи адресуемой ячейки с шиной данных.

Время восстановления - это время, необходимое для приведения памяти в исходное состояние после того, как ЦП снял с ША - адрес, с ШУ - сигнал "чтение" или "запись" и с ШД - данные.

3. Удельная стоимость запоминающего устройства определяется отношением его стоимости к информационной емкости, т.е. определяется стоимостью бита хранимой информации.

4. Потребляемая энергия (или рассеиваемая мощность) приводится для двух режимов работы кристалла: режима пассивного хранения информации и активного режима, когда операции записи и считывания выполняются с номинальным быстродействием. Кристаллы динамической МОП-памяти в резервном режиме потребляют примерно в десять раз меньше энергии, чем в активном режиме. Наибольшее потребление энергии, не зависящее от режима работы, характерно для кристаллов биполярной памяти.

5. Плотность упаковки определяется площадью запоминающего элемента и зависит от числа транзисторов в схеме элемента и используемой технологии. Наибольшая плотность упаковки достигнута в кристаллах динамической МОП-памяти.

6. Допустимая температура окружающей среды обычно указывается отдельно для активной работы, для пассивного хранения информации и для нерабочего состояния с отключенным питанием. Указывается тип корпуса, если он стандартный, или чертеж корпуса с указанием всех размеров, маркировкой и нумерацией контактов, если корпус новый. Приводятся также условия эксплуатации: рабочее положение, механические воздействия, допустимая влажность и другие.

В англоязычной литературе микропроцессор часто называют CPU (central processing unit, [единым] модулем центрального процессора). Причина такого названия кроется в том, что современный процессор представляет собою единый чип. Первый микропроцессор в истории человечества был создан корпорацией Intel в далеком 1971 году.

Роль Intel в истории микропроцессорной индустрии

Речь идет о модели Intel 4004. Мощным он не был и умел выполнять только действия сложения и вычитания. Одновременно он мог обрабатывать всего четыре бита информации (то есть был 4-битным). Но для своего времени его появление стало значительным событием. Ведь весь процессор поместился в одном чипе. До появления Intel 4004, компьютеры базировались на целом наборе чипов или дискретных компонентов (транзисторов). Микропроцессор 4004 лег в основу одного из первых портативных калькуляторов.

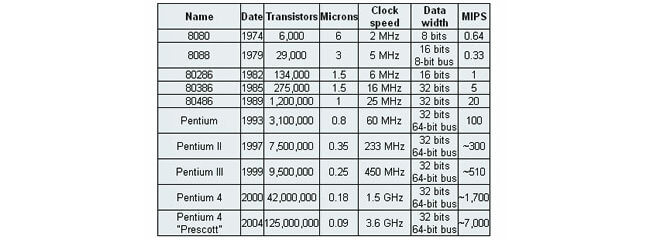

С 2004 года Intel начала предлагать многоядерные процессоры. Число используемых в них транзисторов возросло на миллионы. Но даже сейчас процессор подчиняется тем общим правилам, которые были созданы для ранних чипов. В таблице отражена история микропроцессоров Intel до 2004 года (включительно). Мы сделаем некоторые пояснения к тому, что означают отраженные в ней показатели:

Существует непосредственная связь между тактовой частотой, а также количеством транзисторов и числом операций, выполняемых процессором за одну секунду. Например, тактовая частота процессора 8088 достигала 5 МГЦ, а производительность: всего 0,33 миллиона операций в секунду. То есть на выполнение одной инструкции требовалось порядка 15 тактов процессора. В 2004 году процессоры уже могли выполнять по две инструкции за один такт. Это улучшение было обеспечено увеличением количества процессоров в чипе.

Логика микропроцессора

Чтобы понять, как работает микропроцессор, следует изучить логику, на которой он основан, а также познакомиться с языком ассемблера. Это родной язык микропроцессора.

Микропроцессор способен выполнять определенный набор машинных инструкций (команд). Оперируя этими командами, процессор выполняет три основные задачи:

Поскольку информация достаточно сложна, будем исходить из того, что ширина обеих шин — и адресной и шины данных — составляет всего 8 бит. И кратко рассмотрим компоненты этого сравнительно простого микропроцессора:

Память микропроцессора

Знакомство с подробностями, касающимися компьютерной памяти и ее иерархии помогут лучше понять содержание этого раздела.

Выше мы писали о шинах (адресной и данных), а также о каналах чтения (RD) и записи (WR). Эти шины и каналы соединены с памятью: оперативной (ОЗУ, RAM) и постоянным запоминающим устройством (ПЗУ, ROM). В нашем примере рассматривается микропроцессор, ширина каждой из шин которого составляет 8 бит. Это значит, что он способен выполнять адресацию 256 байт (два в восьмой степени). В один момент времени он может считывать из памяти или записывать в нее 8 бит данных. Предположим, что этот простой микропроцессор располагает 128 байтами ПЗУ (начиная с адреса 0) или 128 байтами оперативной памяти (начиная с адреса 128).

Модуль постоянной памяти содержит определенный предварительно установленный постоянный набор байт. Адресная шина запрашивает у ПЗУ определенный байт, который следует передать шине данных. Когда канал чтения (RD) меняет свое состояние, модуль ПЗУ предоставляет запрошенный байт шине данных. То есть в данном случае возможно только чтение данных.

Из оперативной памяти процессор может не только считывать информацию, он способен также записывать в нее данные. В зависимости от того, чтение или запись осуществляется, сигнал поступает либо через канал чтения (RD), либо через канал записи (WR). К сожалению, оперативная память энергозависима. При отключении питания она теряет все размещенные в ней данные. По этой причине компьютеру необходимо энергонезависимое постоянное запоминающее устройство.

Более того, теоретически компьютер может обойтись и вовсе без оперативной памяти. Многие микроконтроллеры позволяют размещать необходимые байты данных непосредственно в чип процессора. Но без ПЗУ обойтись невозможно. В персональных компьютерах ПЗУ называется базовой системой ввода и вывода (БСВВ, BIOS, Basic Input/Output System). Свою работу при запуске микропроцессор начинает с выполнения команд, найденных им в BIOS.

Команды BIOS выполняют тестирование аппаратного обеспечения компьютера, а затем они обращаются к жесткому диску и выбирают загрузочный сектор. Этот загрузочный сектор является отдельной небольшой программой, которую BIOS сначала считывает с диска, а затем размещает в оперативной памяти. После этого микропроцессор начинает выполнять команды расположенного в ОЗУ загрузочного сектора. Программа загрузочного сектора сообщает микропроцессору о том, какие данные (предназначенные для последующего выполнения процессором) следует дополнительно переместить с жесткого диска в оперативную память. Именно так происходит процесс загрузки процессором операционной системы.

Инструкции микропроцессора

Даже простейший микропроцессор способен обрабатывать достаточно большой набор инструкций. Набор инструкций является своего рода шаблоном. Каждая из этих загружаемых в регистр команд инструкций имеет свое значение. Людям непросто запомнить последовательность битов, поэтому каждая инструкция описывается в виде короткого слова, каждое из которых отражает определенную команду. Эти слова составляют язык ассемблера процессора. Ассемблер переводит эти слова на понятный процессору язык двоичных кодов.

Приведем список слов-команд языка ассемблера для условного простого процессора, который мы рассматриваем в качестве примера к нашему повествованию:

- LOADA mem — Загрузить (load) регистр A из некоторого адреса памяти

- LOADB mem — Загрузить (load) регистр B из некоторого адреса памяти

- CONB con — Загрузить постоянное значение (constant value) в регистр B

- SAVEB mem — Сохранить (save) значение регистра B в памяти по определенному адресу

- SAVEC mem — Сохранить (save) значение регистра C в памяти по определенному адресу

- ADD — Сложить (add) значения регистров A и B. Результат действия сохранить в регистре C

- SUB — Вычесть (subtract) значение регистра B из значения регистра A. Результат действия сохранить в регистре C

- MUL — Перемножить (multiply) значения регистров A и B. Результат действия сохранить в регистре C

- DIV — Разделить (divide) значение регистра A на значение регистра B. Результат действия сохранить в регистре C

- COM — Сравнить (compare) значения регистров A и B. Результат передать в тестовый регистр

- JUMP addr — Перепрыгнуть (jump) к указанному адресу

- JEQ addr — Если выполняется условие равенства значений двух регистров, перепрыгнуть (jump) к указанному адресу

- JNEQ addr — Если условие равенства значений двух регистров не выполняется, перепрыгнуть (jump) к указанному адресу

- JG addr — Если значение больше, перепрыгнуть (jump) к указанному адресу

- JGE addr — Если значение больше или равно, перепрыгнуть (jump) к указанному адресу

- JL addr — Если значение меньше, перепрыгнуть (jump) к указанному адресу

- JLE addr — Если значение меньше или равно, перепрыгнуть (jump) к указанному адресу

- STOP — Остановить (stop) выполнение

Английские слова, обозначающие выполняемые действия, в скобках приведены неспроста. Так мы можем видеть, что язык ассемблера (как и многие другие языки программирования) основан на английском языке, то есть на привычном средстве общения тех людей, которые создавали цифровые технологии.

Работа микропроцессора на примере вычисления факториала

факториал от 5 = 5! = 5 * 4 * 3 * 2 * 1 = 120

На языке программирования C этот фрагмент кода, выполняющего данное вычисление, будет выглядеть следующим образом:

Когда эта программа завершит свою работу, переменная f будет содержать значение факториала от пяти.

Компилятор C транслирует (то есть переводит) этот код в набор инструкций языка ассемблера. В рассматриваемом нами процессоре оперативная память начинается с адреса 128, а постоянная память (которая содержит язык ассемблера) начинается с адреса 0. Следовательно, на языке данного процессора эта программа будет выглядеть так:

// Предположим, что a по адресу 128// Предположим, что F по адресу 1290 CONB 1 // a=1;1 SAVEB 1282 CONB 1 // f=1;3 SAVEB 1294 LOADA 128 // if a > 5 the jump to 175 CONB 56 COM7 JG 178 LOADA 129 // f=f*a;9 LOADB 12810 MUL11 SAVEC 12912 LOADA 128 // a=a+1;13 CONB 114 ADD15 SAVEC 12816 JUMP 4 // loop back to if17 STOP

Теперь возникает следующий вопрос: а как же все эти команды выглядят в постоянной памяти? Каждая из этих инструкций должна быть представлена в виде двоичного числа. Чтобы упростить понимание материала, предположим, что каждая из команд языка ассемблера рассматриваемого нами процессора имеет уникальный номер:

- LOADA — 1

- LOADB — 2

- CONB — 3

- SAVEB — 4

- SAVEC mem — 5

- ADD — 6

- SUB — 7

- MUL — 8

- DIV — 9

- COM — 10

- JUMP addr — 11

- JEQ addr — 12

- JNEQ addr — 13

- JG addr — 14

- JGE addr — 15

- JL addr — 16

- JLE addr — 17

- STOP — 18

Будем считать эти порядковые номера кодами машинных команд (opcodes). Их еще называют кодами операций. При таком допущении, наша небольшая программа в постоянной памяти будет представлена в таком виде:

// Предположим, что a по адресу 128// Предположим, что F по адресу 129Addr машинная команда/значение0 3 // CONB 11 12 4 // SAVEB 1283 1284 3 // CONB 15 16 4 // SAVEB 1297 1298 1 // LOADA 1289 12810 3 // CONB 511 512 10 // COM13 14 // JG 1714 3115 1 // LOADA 12916 12917 2 // LOADB 12818 12819 8 // MUL20 5 // SAVEC 12921 12922 1 // LOADA 12823 12824 3 // CONB 125 126 6 // ADD27 5 // SAVEC 12828 12829 11 // JUMP 430 831 18 // STOP

Как вы заметили, семь строчек кода на языке C были преобразованы в 18 строчек на языке ассемблера. Они заняли в ПЗУ 32 байта.

Декодирование

Рассмотрим работу дешифратора команд на примере инструкции ADD, выполняющей действие сложения:

- В течение первого цикла тактовой частоты процессора происходит загрузка команды. На этом этапе дешифратору команд необходимо: активировать буфер сортировки для счетчика команд; активировать канал чтения (RD); активировать защелку буфера сортировки на пропуск входных данных в регистр команд

- В течение второго цикла тактовой частоты процессора команда ADD декодируется. На этом этапе арифметико-логическое устройство выполняет сложение и передает значение в регистр C

- В течение третьего цикла тактовой частоты процессора счетчик команд увеличивает свое значение на единицу (теоретически, это действие пересекается с происходившим во время второго цикла)

Каждая команда может быть представлена в виде набора последовательно выполняемых операций, которые в определенном порядке манипулируют компонентами микропроцессора. То есть программные инструкции ведут ко вполне физическим изменениям: например, изменению положения защелки. Некоторые инструкции могут потребовать на свое выполнение двух или трех тактовых циклов процессора. Другим может потребоваться даже пять или шесть циклов.

Микропроцессоры: производительность и тенденции

Количество транзисторов в процессоре является важным фактором, влияющим на его производительность. Как было показано ранее, в процессоре 8088 на выполнение одной инструкции требовалось 15 циклов тактовой частоты. А чтобы выполнить одну 16-битную операцию, уходило и вовсе порядка 80 циклов. Так был устроен умножитель АЛУ этого процессора. Чем больше транзисторов и чем мощнее умножитель АЛУ, тем больше всего успевает сделать процессор за один свой такт.

Многие транзисторы поддерживают технологию конвейеризации. В рамках конвейерной архитектуры происходит частичное наложение выполняемых инструкций друг на друга. Инструкция может требовать на свое выполнение все тех же пяти циклов, но если процессором одновременно обрабатываются пять команд (на разных этапах завершенности), то в среднем на выполнение одной инструкции потребуется один цикл тактовой частоты процессора.

Во многих современных процессорах дешифратор команд не один. И каждый из них поддерживает конвейеризацию. Это позволяет выполнять более одной инструкции за один такт процессора. Для реализации этой технологии требуется невероятное множество транзисторов.

64-битные процессоры

Хотя массовое распространение 64-битные процессоры получили лишь несколько лет назад, они существуют уже сравнительно давно: с 1992 года. И Intel, и AMD предлагают в настоящее время такие процессоры. 64-битным можно считать такой процессор, который обладает 64-битным арифметико-логическим устройством (АЛУ), 64-битными регистрами и 64-битными шинами.

Основная причина, по которой процессорам нужна 64-битность, состоит в том, что данная архитектура расширяет адресное пространство. 32-битные процессоры могут получать доступ только к двум или четырем гигабайтам оперативной памяти. Когда-то эти цифры казались гигантскими, но миновали годы и сегодня такой памятью никого уже не удивишь. Несколько лет назад память обычного компьютера составляла 256 или 512 мегабайт. В те времена четырехгигабайтный лимит мешал только серверам и машинам, на которых работают большие базы данных.

Но очень быстро оказалось, что даже обычным пользователям порой не хватает ни двух, ни даже четырех гигабайт оперативной памяти. 64-битных процессоров это досадное ограничение не касается. Доступное им адресное пространство в наши дни кажется бесконечным: два в шестьдесят четвертой степени байт, то есть что-то около миллиарда гигабайт. В обозримом будущем столь гигантской оперативной памяти не предвидится.

64-битная адресная шина, а также широкие и высокоскоростные шины данных соответствующих материнских плат, позволяют 64-битным компьютерам увеличить скорость ввода и вывода данных в процессе взаимодействия с такими устройствами, как жесткий диск и видеокарта. Эти новые возможности значительно увеличивают производительность современных вычислительных машин.

Но далеко не все пользователи ощутят преимущества 64-битной архитектуры. Она необходима, прежде всего, тем, кто занимается редактированием видео и фотографий, а также работает с различными большими картинками. 64-битные компьютеры по достоинству оценены ценителями компьютерных игр. Но те пользователи, которые с помощью компьютера просто общаются в социальных сетях и бродят по веб-просторам да редактируют текстовые файлы никаких преимуществ этих процессоров, скорее всего, просто не почувствуют.

Инструмент проще, чем машина. Зачастую инструментом работают руками, а машину приводит в действие паровая сила или животное.

Компьютер тоже можно назвать машиной, только вместо паровой силы здесь электричество. Но программирование сделало компьютер таким же простым, как любой инструмент.

Процессор — это сердце/мозг любого компьютера. Его основное назначение — арифметические и логические операции, и прежде чем погрузиться в дебри процессора, нужно разобраться в его основных компонентах и принципах их работы.

Два основных компонента процессора

Устройство управления

Устройство управления (УУ) помогает процессору контролировать и выполнять инструкции. УУ сообщает компонентам, что именно нужно делать. В соответствии с инструкциями он координирует работу с другими частями компьютера, включая второй основной компонент — арифметико-логическое устройство (АЛУ). Все инструкции вначале поступают именно на устройство управления.

Существует два типа реализации УУ:

- УУ на жёсткой логике (англ. hardwired control units). Характер работы определяется внутренним электрическим строением — устройством печатной платы или кристалла. Соответственно, модификация такого УУ без физического вмешательства невозможна.

- УУ с микропрограммным управлением (англ. microprogrammable control units). Может быть запрограммирован для тех или иных целей. Программная часть сохраняется в памяти УУ.

УУ на жёсткой логике быстрее, но УУ с микропрограммным управлением обладает более гибкой функциональностью.

Арифметико-логическое устройство

Это устройство, как ни странно, выполняет все арифметические и логические операции, например сложение, вычитание, логическое ИЛИ и т. п. АЛУ состоит из логических элементов, которые и выполняют эти операции.

Большинство логических элементов имеют два входа и один выход.

Ниже приведена схема полусумматора, у которой два входа и два выхода. A и B здесь являются входами, S — выходом, C — переносом (в старший разряд).

Схема арифметического полусумматора

Хранение информации — регистры и память

Как говорилось ранее, процессор выполняет поступающие на него команды. Команды в большинстве случаев работают с данными, которые могут быть промежуточными, входными или выходными. Все эти данные вместе с инструкциями сохраняются в регистрах и памяти.

Регистры

Регистр — минимальная ячейка памяти данных. Регистры состоят из триггеров (англ. latches/flip-flops). Триггеры, в свою очередь, состоят из логических элементов и могут хранить в себе 1 бит информации.

Прим. перев. Триггеры могут быть синхронные и асинхронные. Асинхронные могут менять своё состояние в любой момент, а синхронные только во время положительного/отрицательного перепада на входе синхронизации.

По функциональному назначению триггеры делятся на несколько групп:

- RS-триггер: сохраняет своё состояние при нулевых уровнях на обоих входах и изменяет его при установке единице на одном из входов (Reset/Set — Сброс/Установка).

- JK-триггер: идентичен RS-триггеру за исключением того, что при подаче единиц сразу на два входа триггер меняет своё состояние на противоположное (счётный режим).

- T-триггер: меняет своё состояние на противоположное при каждом такте на его единственном входе.

- D-триггер: запоминает состояние на входе в момент синхронизации. Асинхронные D-триггеры смысла не имеют.

Для хранения промежуточных данных ОЗУ не подходит, т. к. это замедлит работу процессора. Промежуточные данные отсылаются в регистры по шине. В них могут храниться команды, выходные данные и даже адреса ячеек памяти.

Принцип действия RS-триггера

Память (ОЗУ)

ОЗУ (оперативное запоминающее устройство, англ. RAM) — это большая группа этих самых регистров, соединённых вместе. Память у такого хранилища непостоянная и данные оттуда пропадают при отключении питания. ОЗУ принимает адрес ячейки памяти, в которую нужно поместить данные, сами данные и флаг записи/чтения, который приводит в действие триггеры.

Прим. перев. Оперативная память бывает статической и динамической — SRAM и DRAM соответственно. В статической памяти ячейками являются триггеры, а в динамической — конденсаторы. SRAM быстрее, а DRAM дешевле.

Команды (инструкции)

Команды — это фактические действия, которые компьютер должен выполнять. Они бывают нескольких типов:

- Арифметические: сложение, вычитание, умножение и т. д.

- Логические: И (логическое умножение/конъюнкция), ИЛИ (логическое суммирование/дизъюнкция), отрицание и т. д.

- Информационные: move , input , outptut , load и store .

- Команды перехода: goto , if . goto , call и return .

- Команда останова: halt .

Прим. перев. На самом деле все арифметические операции в АЛУ могут быть созданы на основе всего двух: сложение и сдвиг. Однако чем больше базовых операций поддерживает АЛУ, тем оно быстрее.

Инструкции предоставляются компьютеру на языке ассемблера или генерируются компилятором высокоуровневых языков.

В процессоре инструкции реализуются на аппаратном уровне. За один такт одноядерный процессор может выполнить одну элементарную (базовую) инструкцию.

Группу инструкций принято называть набором команд (англ. instruction set).

Тактирование процессора

Быстродействие компьютера определяется тактовой частотой его процессора. Тактовая частота — количество тактов (соответственно и исполняемых команд) за секунду.

Частота нынешних процессоров измеряется в ГГц (Гигагерцы). 1 ГГц = 10⁹ Гц — миллиард операций в секунду.

Чтобы уменьшить время выполнения программы, нужно либо оптимизировать (уменьшить) её, либо увеличить тактовую частоту. У части процессоров есть возможность увеличить частоту (разогнать процессор), однако такие действия физически влияют на процессор и нередко вызывают перегрев и выход из строя.

Выполнение инструкций

Инструкции хранятся в ОЗУ в последовательном порядке. Для гипотетического процессора инструкция состоит из кода операции и адреса памяти/регистра. Внутри управляющего устройства есть два регистра инструкций, в которые загружается код команды и адрес текущей исполняемой команды. Ещё в процессоре есть дополнительные регистры, которые хранят в себе последние 4 бита выполненных инструкций.

Ниже рассмотрен пример набора команд, который суммирует два числа:

- LOAD_A 8 . Это команда сохраняет в ОЗУ данные, скажем, . Первые 4 бита — код операции. Именно он определяет инструкцию. Эти данные помещаются в регистры инструкций УУ. Команда декодируется в инструкцию load_A — поместить данные 1000 (последние 4 бита команды) в регистр A .

- LOAD_B 2 . Ситуация, аналогичная прошлой. Здесь помещается число 2 ( 0010 ) в регистр B .

- ADD B A . Команда суммирует два числа (точнее прибавляет значение регистра B в регистр A ). УУ сообщает АЛУ, что нужно выполнить операцию суммирования и поместить результат обратно в регистр A .

- STORE_A 23 . Сохраняем значение регистра A в ячейку памяти с адресом 23 .

Вот такие операции нужны, чтобы сложить два числа.

Все данные между процессором, регистрами, памятью и I/O-устройствами (устройствами ввода-вывода) передаются по шинам. Чтобы загрузить в память только что обработанные данные, процессор помещает адрес в шину адреса и данные в шину данных. Потом нужно дать разрешение на запись на шине управления.

У процессора есть механизм сохранения инструкций в кэш. Как мы выяснили ранее, за секунду процессор может выполнить миллиарды инструкций. Поэтому если бы каждая инструкция хранилась в ОЗУ, то её изъятие оттуда занимало бы больше времени, чем её обработка. Поэтому для ускорения работы процессор хранит часть инструкций и данных в кэше.

Если данные в кэше и памяти не совпадают, то они помечаются грязными битами (англ. dirty bit).

Поток инструкций

Современные процессоры могут параллельно обрабатывать несколько команд. Пока одна инструкция находится в стадии декодирования, процессор может успеть получить другую инструкцию.

Однако такое решение подходит только для тех инструкций, которые не зависят друг от друга.

Если процессор многоядерный, это означает, что фактически в нём находятся несколько отдельных процессоров с некоторыми общими ресурсами, например кэшем.

Адресное пространство МП состоит из множества ячеек памяти ОЗУ, из которых он может брать информацию или засылать ее. Как говорилось выше, начиная с 4-го поколения доминирует байтовая организация памяти, и минимально адресуемой единицей является байт. Например, для ОЗУ емкостью 1024 кбайта адреса байтов таковы:

00000 00001 . FFFFF

При обмене информацией с памятью процессор обращается к ячейкам ОЗУ по их номерам (адресам). Способы задания требуемых адресов в командах ЭВМ принято называть методами адресации.От видов и разнообразия методов адресации существенно зависит эффективность работы программы с данными, особенно если последние организованы в определенную структуру.

Для того, чтобы процессор мог извлечь данные из ячейки ОЗУ или поместить их туда, необходимо где-то задать требуемый адрес. Если адрес находится в самой команде, то мы имеем дело с прямой адресацией.Поскольку при подобном способе слишком сильно возрастает длина команды, то, чтобы избежать этого неприятного эффекта, при обращении к ОЗУ процессор использует методкосвенной адресации. Идея состоит в том, что адрес памяти предварительно заносится в один из регистров МП, а в команде содержится лишь ссылка на этот регистр. Если учесть, что при хранении адреса в регистре его еще очень удобно модифицировать (скажем, циклически увеличивая на заданную величину), становится понятным, почему косвенная адресация нашла такое широкое применение.

Приведем описание наиболее распространенных вариантов ссылок на исходную информацию (учитывая, что терминология для разных МП может различаться, названия методов адресации не приводятся):

1) данные находятся в одном из регистров МП;

2) данные входят непосредственно в состав команды, т.е. размещаются после кода операции (операции с константой);

3) данные находятся в ячейке ОЗУ, адрес которой содержится в одном из регистров МП;

4) данные находятся в ячейке ОЗУ, адрес которой вычисляется по формуле

адрес = базовый адрес + смещение.

Базовый адрес хранится в одном из регистров МП и является начальной точкой массива данных. Смещение может быть как некоторой константой, так и содержимым другого регистра. Часто такой способ доступа к ОЗУ называют индексным,так как это похоже на нахождение элемента в одномерном массиве по его индексу.

Следует подчеркнуть, что здесь описаны лишь наиболее общие методы адресации. У конкретных моделей МП существуют некоторые особенности адресации ОЗУ. Кроме того, имеющиеся методы адресации могут быть комбинированными. Так, например, в процессорах семейства PDPвозможна двойная косвенная адресация: данные хранятся в ячейке ОЗУ, адрес которой хранится в ячейке, адрес которой находится в указанном регистре (как тут не вспомнить детский стишок о синице, которая ворует пшеницу, которая в темном чулане хранится, в доме, который построил Джек?).

Добавим, что, помимо всего прочего, при сегментной адресации один и тот же адрес ОЗУ может быть представлен несколькими комбинациями чисел (в самом деле, одну и ту же сумму можно получить разными способами)

Поскольку современные интелловские процессоры, начиная с 80386, стали 32-разрядными, их регистров хватает, чтобы адресовать до 4 Гбайт памяти Сегментный способ при этом становится излишним, хотя и сохраняется как вариант ради обеспечения программной совместимости с предыдущими моделями.

Стек -это неявный способ адресации, при котором информация записывается и считывается только последовательным образом с использованием, так называемого, указателя стека.

1) уменьшит указатель стека на 2 (целое число занимает в памяти 2 байта);

2) запишет N1 по полученному адресу 2004 (рис. 4.13, б).

Рис. 4.13.Пример для изучения принципа работы стека

1) считает в N3 значение из стека;

2) увеличит указатель на 2 (рис. 4.13, г).

Аналогично прочитаем N2 и N1, после чего стек опустеет и вернется к начальному состоянию, изображенному на рис. 4.13, а.

Еще раз подчеркнем, что в командах работы со стеком адрес ОЗУ не фигурирует в явном виде. Но при этом молчаливо предполагается, что указатель стека уже задан. Как правило, инициализацию указателя стека компьютер делает сам, но не мешает поинтересоваться, так ли это в вашем конкретном случае и достаточно ли памяти под стек имеется при этом. Если указатель стека определен неправильно, то запись в стек может разрушить полезную информацию в ОЗУ и вызвать непредсказуемые последствия.

Читайте также:

- Завоевательная программа фашизма и холокост кратко

- Российское общество сегодня социальный срез кратко

- Консультация для родителей в детском саду на тему закаливание детей летом

- Кратко изложить порядок проведения и сроки осмотра устройств и сооружений железной дороги

- Ознакомление родителей с нормативными документами в школе