Системы команд машин различных поколений адресация памяти реферат

Обновлено: 29.06.2024

В целом систему команд MCS-51 можно охарактеризовать как весьма мощную и симметричную в том смысле, что программист имеет возможность использовать большинство операций с полным набором методов адресации и программно доступных ресурсов аппаратуры.

Разработчик изделия работает с системой команд при создании программы на языке ассемблера. При этом он имеет дело с какой-либо кросс-системой, имеющей свою версию языка.

Каждая команда сообщает процессору выполняемую операцию и методы доступа к операндам. Командная строка языка ассемблер содержит метку (символический адрес), мнемонику (символическое имя) команды, операнды, комментарий. Имя команды однозначно связано с выполняемой ею операцией (действием). Число операндов в разных командах микроконтроллеров MCS-51 находится в диапазоне от нуля до трех, операнды разделяются запятыми. При двух операндах первым указывается приемник, вторым источник. Многие команды по умолчанию используют аккумулятор как один из источников операнда и/или как приемник результата.

Методы адресации представляют собой набор механизмов доступа к операндам. Одни из них просты и поэтому приводят к компактному формату команды и быстрому доступу к операнду, но объем доступных с их помощью ресурсов ограничен. Другие методы адресации позволяют оперировать со всеми имеющимися в системе ресурсами, но команда получается длинной, на ее ввод и выполнение тратится много времени. Набор методов адресации в каждой системе команд является компромиссным сочетанием известных механизмов адресации, выбранным проектировщиками архитектуры исходя из набора решаемых задач. При этом для процессоров с архитектурой CISC (complete instruction set computer) большую роль имеет и удобство работы программиста.

С точки зрения формата, команды микроконтроллеров семейства MCS-51 делятся на одно-, двух- и трехбайтные. Используется четыре основных метода адресации.

Регистровая адресация. Операнд находится в одном из регистров общего назначения R0..R7 банка, номер которого определяется разрядами RS0, RS1 регистра PSW. Номер регистра определяется тремя младшими битами байта кода операции (КОП - первый байт команды). Регистровая адресация позволяет в одном байте указать код операции и адрес операнда. Поскольку операнд находится во внутренней ячейке, не требуется циклов обращения к внешней памяти данных.

Формат команды сложения ADD A,Rn следующий:

Прямая адресация. Операнд находится во внутренней памяти данных, адрес ячейки определяет отдельный байт команды. Таким образом, команды с использованием прямой адресации имеют минимум два байта, доступны только 256 ячеек, обращения за операндом к внешней памяти не требуется.

Формат команды сложения ADD A,direct следующий:

Косвенно-регистровая адресация. Этот метод адресации использует регистры R0 и R1 в качестве указателей. Регистры берутся из банка, определяемого разрядами RS0, RS1 регистра PSW. Содержимое этих регистров используется как адрес для обращения к ячейке внутренней памяти данных, хранящей операнд. Команда получается однобайтной, номер регистра указывает младший бит. Длина команды при этом соответствует длине команды с использованием регистровой адресации, но косвенная адресация дает доступ ко всему пространству внутренней памяти данных.

Формат команды сложения ADD A, @Ri следующий:

Непосредственная адресация. Операнд находится в отдельном байте команды, это константа. Таким образом, команды с использованием непосредственной адресации имеют минимум два байта, обращения за операндом к внешней памяти не требуется.

Рассмотрен микропроцессор фирмы Texas Instruments семейства TMS320 S40. Особенности сигнальных процессоров. Типы адресации микропроцессора. Рассмотрение команды LDI||STI проверка ее при разных значениях, применение программы C4x Simulator Composer.

| Рубрика | Программирование, компьютеры и кибернетика |

| Вид | курсовая работа |

| Язык | русский |

| Дата добавления | 09.04.2019 |

| Размер файла | 2,4 M |

Студенты, аспиранты, молодые ученые, использующие базу знаний в своей учебе и работе, будут вам очень благодарны.

МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РФ

Федеральное государственное бюджетное образовательное учреждение

высшего профессионального образования

«Воронежский государственный лесотехнический университет

имени Г.Ф. Морозова

ПОЯСНИТЕЛЬНЬНАЯ ЗАПИСКА

КУРСОВОЙ РАБОТЫ

Дисциплина: Программирование микропроцессоров

Основные способы адресации в памяти

Студент группы ИС2-151-ОБ

Белов Семён Вадимович

Руководитель, к.т.н., профессор

Зольников Константин Владимирович

- Введение

- 1. Теоретичкая часть

- 2. Практическая часть

- Заключение

- Список используемой литературы

Работа микропроцессора невозможна без использования любого вида обращения к памяти, а именно адресации. При вычислении любых операций над данными необходимо знать размещение исходных данных, а также иметь свободный адрес для хранения результатов. Если команда использует два и более операнда, то необходимо задать адрес для каждого из них. Знание принципов построения микропроцессора, логики взаимодействия операндов способствует эффективному написанию кода для решения различных прикладных задач. Наличие знаний об способах использования адресации в микропроцессорах позволит создавать различной сложности алгоритмы.

Задачей данной курсовой работы заключается в рассмотрении коммуникационных портов, а также их использовании в микропроцессоре TMS320 S40.

- 1. Теоретичкая часть

- микропроцессор сигнальный программа

- Микропроцессор фирмы Texas Instruments семейства TMS320 S40 является сигнальным процессором. Так как вся его система команд ориентирована на быстрое выполнение алгоритмов цифровой обработки сигналов. К ключевым особенностям сигнальных процессора можно отнести

1. Конвейерное выполнение команд

2. Разделение памяти программы и памяти данных

3. Основной операционных блок выполняется за один цикл

4. Все вспомогательные арифметические блоки для вычисления адресов операндов выполняются за один машинный цикл

Применение сигнальных процессоров разнообразно - от встроенных микроконтроллеров в приборы бытового назначения до больших (до нескольких тысяч микропроцессоров) мультипроцессорных систем общего назначения. Одним из подходов к программированию таких систем является программирование на ассемблере. Программа имеет максимальную эффективность по быстродействию и используемой памяти, но большую трудоемкость в разработке. Другой подход предполагает использование языка высокого уровня. Вначале создается прототип программы на языке высокого уровня, получается ассемблерный текст каждого модуля программы и проводится вручную оптимизация ассемблерного кода для получения заданных временных характеристик программы или ее отдельных участков. Программирование (или оптимизация) на уровне ассемблерного кода позволяет максимально эффективно использовать особенности архитектуры и системы команд применяемого процессора.

Для изучения типов адресации микропроцессора рассмотрим основные его характеристики

цикл команды 50нс для тактовой

максимальный адресуемый объем

памяти 16 Gb (4GЧ32);

разрядность операндов 32 бита;

порты до 20 Мб/с;

производительность до 275 MOPS;

встроенный сопроцессор прямого

доступа к памяти (ПДП) до 75 MOPS;

одноцикловые операции с плавающей точкой 40/32 бита;

внутренний кэш команд на 512 байт;

скорость обмена данными через

встроенные порты ввода/вывода до 100 Мб/с;

внутреннее ОЗУ 8 Кбайт.

В процессорах семейства TMS320 S40 возможны четыре основных режима адресации памяти данных:

2) Косвенная адресация. Восемь вспомогательных регистров (AR0 - AR7) обеспечивают гибкую и удобную косвенную адресацию в процессорах TMS320C5х. В случае косвенной адресации адрес операнда находится в текущем вспомогательном регистре. Для выбора текущего вспомогательного регистра необходимо загрузить в регистр указателя вспомогательного регистра (ARP) значение в диапазоне от 0 до 7.

Над содержимым вспомогательных регистров можно производить ряд арифметических операций с помощью арифметического устройства вспомогательных регистров - ARAU (Auxiliary Register Arithmetic Unit), которое выполняет арифметические операции над содержимом вспомогательных регистров в фазе декодирования команды. Это позволяет сформировать адрес перед фазой декодирования следующей команды. Использование ARAU позволяет модифицировать содержимое ARn после использования его содержимого в текущей команде, например, регистр может быть инкрементирован или декрементирован.

С помощью косвенной адресации, может быть адресована любая ячейка памяти в пределах 64К при помощи полного 16-ти разрядного значения, содержащегося во вспомогательном регистре.

Существует два основных вида модификации адреса при косвенной адресации:

- косвенная адресация с инкрементом и декрементом на 1;

- косвенная адресация с индексацией (изменением) на величину, содержащуюся в регистре INDX.

Во втором случае возможно в свою очередь два варианта:

- добавление или вычитание содержимого регистра INDX;

- добавление или вычитание содержимого регистра INDX по правилам бит реверсивной арифметики (обычно используется для реализации быстрых алгоритмов преобразования Фурье).

Во всех случаях содержимое вспомогательного регистра, указанного регистром ARP, используется как адрес операнда в памяти данных. ARAU осуществляет математические операции над содержимым указанного вспомогательного регистра.

После выполнения любой команды с косвенной адресацией в ARP может быть загружено новое значение. Если в ARP загружается новая величина, то старая величина загружается в буфер вспомогательного регистра состояния ST1.

Косвенная адресация может быть использована во всех командах, кроме команд с непосредственными операндами или без операндов.

4) Циклическая адресация представляет метод адресации, при котором происходит циклическое обращение к ячейкам некоторой области памяти (к ячейкам буфера), т.е. при достижении конца буфера автоматически происходит переход к его началу и наоборот. В пределах буфера для указания адреса используется вспомогательный регистр (т.е. косвенный принцип адресации). При инкременте содержимого регистра (увеличении адреса) при достижении последней ячейки буфера в этот регистр автоматически заносится начальный адрес буфера.

Рис.1 Циклический буфер

На рисунке 1 приведен алгоритм циклической адресации. Рисунок показывает, как будет распределяться последовательность отсчетов входного сигнала в буфере длиной 6 ячеек. В таком буфере, например, можно организовать линию задержки на 5T, где T - интервал дискретизации. Для этого надо последовательно считывать отсчеты x (0) и x(5), x(1) и x(6) и т.д.

В процессорах семейства TMS320 S40 имеется аппаратный механизм реализации циклических буферов, которые позволяют организовать два одновременно действующих циклических буфера, управляемых с помощью вспомогательных регистров. Существует 5 регистров, с помощью которых осуществляется управление циклическими буферами:

- CBSR1 - регистр начального адреса первого циклического буфера;

- CBSR2 - регистр начального адреса второго циклического буфера;

- CBER1 - регистр конечного адреса первого циклического буфера;

- CBER2 - регистр конечного адреса второго циклического буфера;

- CBCR - регистр управления циклическими буферами.

Чтобы задать циклический буфер, необходимо вначале загрузить адреса начала и конца в соответствующие регистры циклического буфера, затем определить вспомогательный регистр, который будет работать указателем на ячейку памяти внутри циклического буфера. И в завершение установить бит разрешения работы соответствующего циклического буфера в регистре CBCR.

Общая схема архитектуры на примере процессора TMS3 2OC4x представлена на рис. 2

Процессор TMS320C4x имеет адресное пространство в 4G слов (4GЧ32), которое является общим для памяти программ, памяти данных и портов ввода/вывода. Карта памяти управляется уровнем на входном контакте ROMEN и для различных значений этого сигнала показана на рис.3

Рис. 2 Общая схема архитектуры

Рис. 3 Карта памяти управления уровнем на входном контакте ROMEN для различных значений

Как видно из рисунка, сигналом ROMEN управляется только начальная зона адресного пространства величиной в 1М слов. В случае ROMEN=0 - это внешняя память, доступная процессору через локальную шину, а в случае ROMEN=1 - это внутреннее ПЗУ, содержащее начальный загрузчик (адреса00000000h - 00000FFFh), который используется при загрузке программ из внешнего ПЗУ или с одного из коммуникационных портов. Работа начального загрузчика описана в п.1.12. Следующие 1М слов используются для адресации внутренних периферийных устройств: таймеров, коммуникационных портов, регистров сопроцессора ПДП и регистров управления внешними шинами

Адресное пространство 00300000h - 7FFFFFFFh принадлежит внешней локальной шине, а 80000000h-FFFFFFFFh - внешней глобальной шине. К ши нам могут подключаться память или устройства ввода/вывода с различным быстродействием. При обращении в зону адресов 00000000h - 00300000h операций на локальной шине не производится (не вырабатывается строб шины), если ROMEN = 1. Если входной сигнал ROMEN = 0, на локальной шине производится передача данных при обращении по адресам 00000000h - 000FFFFFh. Каждая шина содержит два набора сигналов, управляющих передачей данных по шине (называемых STRB0 и STRB1), и набор сигналов, управляющих доступом(в случае разделяемой памяти в МП системах).Логика работы каждой шины определяется собственным регистром управления, в котором программируется адресное пространство, размер страницы памяти, режим формирования сигнала готовности и количество тактов ожидания (0-7) для каждого из стробов STRB0 и STRB1. Адреса регистров управления внешними шинами:0010 0000h - регистр управления глобальной шиной (GMICR);0010 0004h - регистр управления локальной шиной (LMICR).

Обладая этим набором регистров можно реализовать пять типов адресации операндов

При задании операндам регистровой адресации их значения содержатся в регистрах процессора. Список регистров представлен на рисунке

Рис. 4 Список регистров

Во время формирования прямой адресации создаётся две компоненты, первая содержит указатель страницы памяти данных, а вторая это 16 разрядное поле прямого адреса из слова команды. Схема формирования адреса приведена на рисунке

Рис. 5 Схема формирования адреса

Для формирования адреса операнда используются содержимое вспомогательных регистров AR0-AR7, смещение, указанное в слове команды и содержимое индексных регистров IR0, IR1 в различных сочетаниях. Процессор TMS320C4x имеет 26 режимов косвенной адресации. Среди них можно выделить следующие группы:

1. не модифицирующие вспомогательный регистр

2. осуществляющие модификацию вспомогательного регистра до его использования в качестве адреса

3. модифицирующие вспомогательный регистр после его использования для адресации операнда

4. использующие специальную модификацию вспомогательного регистра

Во время формирования непосредственной адресации операнд располагается в восьми или шестнадцати младших битах слова команды. В зависимости от типа данных, принятых для конкретной команды, поле операнда может интерпретироваться как без знаковое целое, целое со знаком или число в коротком формате с ПТ. Синтаксис адресации: expr.

Относительная адресация используется в командах переходов. Выполнение команды перехода заключается в изменении программного счетчика PC на величину константы (смещения перехода), содержащейся в 16 или 24 младших битах слова команды.

Смещение перехода является целым числом со знаком. Оно вычисляется:

для стандартных переходов

СМЕЩЕНИЕ = АДРЕС ПЕРЕХОДА - (АДРЕС КОМАНДЫ ПЕРЕХОДА + 1);

для задержанных переходов (см. п.1.12)

СМЕЩЕНИЕ = АДРЕС ПЕРЕХОДА - (АДРЕС КОМАНДЫ ПЕРЕХОДА + 3

Процессор TMS320C4x не может выполнять операции типа память-память, поэтому один из операндов всегда имеет регистровую адресацию. В большинстве команд процессора регистровая адресация одного из операндов может сочетаться с любым типом адресации второго операнда, за исключением относительной адресации. Как правило, приемником результата операции всегда является регистр, кроме команд сохранения (типа STI, STF), где приемником служит память с косвенной или прямой адресацией. Команды безусловных переходов используют относительную адресацию с 24-разрядным смещением, а команды условных переходов - относительную с 16-разрядным смещением или регистровую адресацию

Рис. 6 Основной набор шин процессора коммуникационных портов

По сигналу сброса RESET порты 0, 1 и 2 процессора устанавливаются в режим передачи данных, а порты 3, 4 и 5 - в режим приема. Логику работы коммуникационного порта рассмотрим на примере связи двух процессоров TMS320C4x (рис. 1.7). Порт 0 процессора A, установленный сигналом сброса в режим передачи, связан с одноименными линиями порта 3 процессора В, находящегося после сброса в режиме приема (порт 0 процессора A владеет маркером шины).

Рис. 7 Архитектура коммуникационного порта

Если в выходном буфере коммуникационного пор-та 0 процессора A имеется хотя бы одно слово данных, начинается передача слова. Байты слова выставляются на шину данных, начиная с младшего. Байт сопровождается сигналом CSTRB0 низкого уровня. Порт 3 процессора B принимает байт с шины данных и отвечает сигналом CRDY3 низкого уровня. Если в выходном буфере порта 3 процессора B появится слово данных, арбитр порта3 выработает сигнал CREQ3 запроса маркера шины. После передачи очередного слова арбитр порта 0 процессора A проанализирует сигнал CREQ0=CREQ3, выдаст сигнал передачи маркера шины CACK0 на порт 3 процессора B и переведет порт 0 процессора A в режим приема. Арбитр порта 3 процессора B примет сигнал CACK3=CACK0 и переведет свой порт в режим передачи. Передача данных пойдет аналогично, но из процессора B в процессор A. Если у процессора A еще есть данные в выходном буфере, его арбитр выработает запрос маркера шины на процессор B и все повторится.

Рис. 8 Направление сигналов внешней шины

Проверка запроса маркера CREQx производится арбитром порта, осуществляющего передачу (владеющего маркером), после передачи каждого слова данных для избежания монополизации шины данных одним из портов.

Рис. 9 Пример связи процессоров через коммуникационные порты

Логика работы коммуникационного порта незаметна для программиста, и, с его точки зрения, коммуникационный порт представляет из себя двунаправленный 32-разрядный интерфейс, имеющий три регистра в адресном пространстве периферийных устройств: регистр управления, входной порт и выходной порт. Распределение адресов коммуникационных портов в адресном пространстве показано на рис. 1.8, а назначение битов регистра управления. Следует отметить, что программно могут изменяться только биты ICH иOCH регистра управления. Поля OUTPUT LEVEL иINPUT LEVEL изменяются косвенно. Поле OUTPUTLEVEL увеличивается на единицу при записи слова в регистр выходного порта, поле INPUT LEVEL уменьшается на единицу при считывании регистра входного порта. Синхронизация коммуникационных портов с CPUи DMA поддерживается двумя способами. Простейшей формой синхронизации является использование внутренних сигналов готовности. Если CPU или DMA сопроцессор пытаются прочитать пустой входной буфер или записать в заполненный выходной буфер, вырабатывается сигнал неготовности, переводящий CPU или DMA в состояние ожидания. В этом случае цикл доступа к буферу растягивается до появления сигнала готовности. Сигналами готовности являются внутренние сигналы OCRDY для выходного буфера и ICRDY для входного буфера. Для синхронизации по прерываниям коммуникационный порт генерирует четыре внутренних сигнала, перечисленных на рис. 10

Рис. 10 Регистры управления коммуникационных портов

Прерываниями CPU от коммуникационных портов управляют биты 1-24регистра разрешения внутренних прерываний IIE (см. п.1.3), вектора прерываний коммуникационных портов приводятся в табл.1.3. Примечательно, что внутренние сигналы ICFULL, ICRDY, OCRDY и OCEMPTY не отражаются в регистре IIF. Информация о состоянии этих сигналов может быть получена из полей OUTPUT LEVEL и INPUT LEVEL регистра управления соответствующего коммуникационного порта. Для синхронизации коммуникационных портов и каналов сопроцессора ПДП используются только сигналы ICRDY и OCRDY.

Рис. 11 Внутренние сигналы прерывания от коммуникационных портов

2. Практическая часть

В практической части используется программа C4x Simulator Composer

Целью данной курсовой работы в практической части заключается рассмотрение команды LDI||STI проверка её при разных значениях.

Системная память.Обычно под системной понимают лишь оперативную память. На самом деле работоспособность всей компьютерной системы зависит от характеристик подсистемы памяти в целом. Подсистема памяти охватывает:

оперативную память как таковую;

кэш-память первого уровня, расположенную в ядре МП;

кэш-память второго уровня (в некоторых конфигурациях она выступает как кэш третьего уровня), размещаемую на СП, на картридже МП или в его ядре;

шины данных и команд, объединяющие все элементы подсистемы в единое целое.

Системная память подразделяется на два типа — с динамической и статической выборкой. В первом случае значение бита информации в ячейке определяется наличием или отсутствием заряда на миниатюрном конденсаторе, управляемом одним—двумя транзисторами. В статической памяти применены специальные элементы — триггеры, реализованные на 4-6 транзисторах. Естественно, что из-за необходимости ожидания накопления (стекания) заряда на конденсаторе быстродействие DRAMниже. Однако благодаря большему числу транзисторов на ячейку, память SRAMсущественно дороже. Обычно модули DRAМ применяют в оперативной и видеопамяти, а модули SRAМ — в качестве быстрых буферных элементов в процессорах, на СП, в контроллерах дисков, CD-RОМ и пр.

Статическая память. Ячейкой в статической памяти является триггер — логический элемент с двумя устойчивыми достояниями, в любом из которых он сохраняется до тех пор, пока подается питание. Время срабатывания триггера составляет в современных микросхемах единицы наносекунд. Однако плотность компоновки ячеек SRAMсущественно ниже, чем в микросхемах DRAM, а стоимость производства выше, поэтому статическая память применяется лишь в наиболее ответственных компонентах.

В современных системах обычно используется конвейерный режим с пакетным способом передачи данных (PipelinedBurstCache), организованный на микросхемах статической памяти с синхронным доступом.

Асинхронная динамическая память (DRAM).Асинхронный интерфейс работы динамической памяти предусматривает наличие отдельного устройства в контроллере памяти для генерации управляющих сигналов. Для операций чтения/записи определяется продолжительность, зависящая от технологии изготовления микросхемы, ширины шины данных, наличия буфера и других параметров. Каждый цикл операции чтения и записи ячеек памяти может иметь продолжительность, отличную от других циклов. Никакая последующая операция не может начаться до сигнала об окончании предыдущей. Для генерации необходимых импульсов контроллер асинхронной памяти имеет делитель, вырабатывающий сигналы необходимой частоты для каждой операции внутри цикла.

Синхронная динамическая память (SDRAM).Вэтом случае все команды и обмен данными по шине памяти проходят синхронно с тактовыми импульсами системной шины, поэтому все циклы одной операции имеют одинаковую продолжительность.

Ячейки в динамической памяти образуют матрицу, состоящую из строк и столбцов. При считывании данных содержимое одной строки целиком переносится в буфер, реализованный на элементах статической памяти. После этого из строки считывается значение (0 или 1) нужной ячейки, и содержимое буфера вновь записывается в прежнюю строку динамической памяти. Такие переносы данных осуществляются путем изменения состояния конденсаторов ячеек, то есть происходит процесс заряда (разряда, если конденсатор был заряжен). Так как конденсаторы чрезвычайно малы, высока вероятность непроизвольного изменения их состояния из-за паразитных утечек и наводок.

Для исключения утраты данных проводятся циклы регенерации с определенной частотой, которые обычно инициализируются специализированными микросхемами. За один такт микропроцессора память может регенерироваться несколько раз.

Без участия МП информация из памяти может считываться блоками устройством прямого доступа к памяти DMA— DirectMemoryAccess. При необходимости оно посылает запрос, содержащий адрес и размер блока данных, а также управляющие сигналы. Так как доступ к памяти по каналам DMAодновременно могут иметь несколько устройств (например, процессор, видеокарта с интерфейсом AGP, контроллер шины PCI, HDD), образуется очередь запросов, хотя каждому потребителю ресурсов памяти требуются собственные данные, часто расположенные не только в разных микросхемах, но и в разных банках памяти.

ОЗУ реализуется на микросхемах DRAM (DynamicRAМ — динамическая память с произвольной выборкой), характеризующихся по сравнению с другими разновидностями памяти низкой стоимостью и высокой удельной ёмкостью, но большим энергопотреблением и меньшим быстродействием. Каждый информационный бит (0 или 1) в DRAMхранится в виде заряда конденсатора. Из-за токов утечки этот заряд необходимо с определённой периодичностью обновлять. Регенерация содержимого памяти требует дополнительного времени, а запись информации во время регенерации в память не допускается.

Видеоадаптер ПК позволяет монитору взаимодействовать с процессором. Поэтому видеоадаптер должен иметь специальную память (видеопамять), в которую процессор записывает изображение в периоды относительно небольшой загруженности. А уже затем видеоадаптер, независимо от процессора, может выводить содержимое видеопамяти на экран. В современных условиях минимальным объёмом видеопамяти следует считать 32 Мбайт, приемлемым — 128 Мбайт, комфортным — 256 Мбайт. Ввиду больших объёмов видеоинформации видеоадаптеры, как правило, подключаются к материнской плате через специализированные шины с наибольшей пропускной способностью.

В микросхеме CMOS хранятся данные о гибких и жестких дисках, о процессоре, о некоторых других устройствах материнской платы. Тот факт, что компьютер четко отслеживает время и календарь (даже и в выключенном состоянии), тоже связан с тем, что показания системных часов постоянно хранятся (и изменяются) в CMOS. Таким образом, программы, записанные в BIOS, считывают данные о составе оборудования компьютера из микросхемы CMOS, после чего они могут выполнить обращение к жесткому диску, а в случае необходимости и к гибкому, и передать управление тем программам, которые там записаны.

Нередко кэш-память распределяют по нескольким уровням. Кэш первого уровня выполняется в том же кристалле, что и сам процессор, и имеет объем порядка десятков Кбайт. Кэш второго уровня находится либо в кристалле процессора, либо в том же узле, что и процессор, хотя и исполняется на отдельном кристалле. Кэш-память первого и второго уровня работает на частоте, согласованной с частотой ядра процессора. Кэш-память третьего уровня выполняют на быстродействующих микросхемах типа SRAMи размещают на материнской плате вблизи процессора. Ее объемы могут достигать нескольких Мбайт, но работает она на частоте материнской платы.

2. Организация систем адресации и команд

Процессор — основная микросхема компьютера, в которой и производятся все вычисления. Конструктивно процессор состоит из ячеек, похожих на ячейки оперативной памяти, но в этих ячейках данные могут не только храниться, но и изменяться. Внутренние ячейки процессора называют регистрами. Важно также отметить, что данные, попавшие в некоторые регистры, рассматриваются не как данные, а как команды, управляющие обработкой данных в других регистрах. Среди регистров процессора есть и такие, которые в зависимости от своего содержания способны модифицировать исполнение команд. Таким образом, управляя засылкой данных в разные регистры процессора, можно управлять обработкой данных. На этом и основано исполнение программ.

С остальными устройствами компьютера, и в первую очередь с оперативной памятью, процессор связан несколькими группами проводников, называемых шинами. Основных шин три: шина данных, адресная шина и командная шина.

Адресная шина.У процессоров IntelPentium (а именно они наиболее распространены в персональных компьютерах) адресная шина 32-разрядная, то есть состоит из 32 параллельных линий. В зависимости от того, есть напряжение на какой-то из линий или нет, говорят, что на этой линии выставлена единица или ноль. Комбинация из 32 нулей и единиц образует 32-разрядный адрес, указывающий на одну из ячеек оперативной памяти. К ней и подключается процессор для копирования данных из ячейки в один из своих регистров.

Шина данных. По этой шине происходит копирование данных из оперативной памяти в регистры процессора и обратно. В компьютерах, собранных на базе процессоров IntelPentium, шина данных 64-разрядная, то есть состоит из 64 линий, по которым за один раз на обработку поступают сразу 8 байтов.

Система команд процессора. В процессе работы процессор обслуживает данные, находящиеся в его регистрах, в поле оперативной памяти, а также данные, находящиеся во внешних портах процессора. Часть данных он интерпретирует непосредственно как данные, часть данных — как адресные данные, а часть — как команды. Совокупность всех возможных команд, которые может выполнить процессор над данными, образует так называемую систему команд процессора. Процессоры, относящиеся к одному семейству, имеют одинаковые или близкие системы команд. Процессоры, относящиеся к разным семействам, различаются по системе команд и не взаимозаменяемы.

Процессоры с расширенной и сокращенной системой команд.Чем шире набор системных команд процессора, тем сложнее его архитектура, тем длиннее формальная запись команды (в байтах), тем выше средняя продолжительность исполнения одной команды, измеренная в тактах работы процессора. Так, например, система команд процессоров IntelPentium в настоящее время насчитывает более тысячи различных команд. Такие процессоры называют процессорами с расширенной системой команд — CISС-процессорами (CISC— ComplexInstructionSetComputing).

В противоположность CISC-процессорам в середине 80-х годов появились процессоры архитектуры RISCс сокращенной системой команд (RISC— ReducedInstructionSetComputing). При такой архитектуре количество команд в системе намного меньше, и каждая из них выполняется намного быстрее. Таким образом, программы, состоящие из простейших команд, выполняются этими процессорами много быстрее. Оборотная сторона сокращенного набора команд состоит в том, что сложные операции приходится эмулировать далеко не эффективной последовательностью простейших команд сокращенного набора.

В результате конкуренции между двумя подходами к архитектуре процессоров сложилось следующее распределение их сфер применения:

• CISC-процессоры используют в универсальных вычислительных системах;

• RISC-процессоры используют в специализированных вычислительных системах или устройствах, ориентированных на выполнение единообразных операций.

Для персональных компьютеров платформы IBMPCдолгое время выпускались только CISC-процессоры, к которым относятся и все процессоры семейства IntelPentium. Однако в последнее время компания AMD приступила к выпуску процессоров семейства AMD-K6, в основе которых лежит внутреннее ядро, выполненное по RISC-архитектуре, и внешняя структура, выполненная по архитектуре CISC. Таким образом, сегодня появились процессоры, совместимые по системе команд с процессор

ЗаключениеСистемная память подразделяется на два типа — с динамической и статической выборкой, динамическая в свою очередь на синхронную и асинхронную.

ОЗУ (оперативное запоминающее устройство) — память с произвольной выборкой, она хранит выполняемые программы и данные, непосредственно участвующие в операциях. От объёма ОЗУ зависит не только возможность работы с ресурсоёмкими программами, но и производительность ПК.

Видеоадаптер имеет специальную память (видеопамять), в которую процессор записывает изображение в периоды относительно небольшой загруженности. А уже затем видеоадаптер, независимо от процессора, выводит содержимое видеопамяти на экран.

Процессор — основная микросхема компьютера, в которой и производятся все вычисления. Конструктивно процессор состоит из ячеек, данные в них могут не только храниться, но и изменяться. Внутренние ячейки процессора называют регистрами. Данные, попавшие в некоторые регистры, рассматриваются не как данные, а как команды, управляющие обработкой данных в других регистрах. С остальными устройствами компьютера, и в первую очередь с оперативной памятью, процессор связан несколькими группами проводников, называемых шинами. Основных шин три: шина данных, адресная шина и командная шина.

Адресная шина состоит из параллельных линий. В зависимости от того, есть напряжение на какой-то из линий или нет, говорят, что на этой линии выставлена единица или ноль. Комбинация из нулей и единиц образует разрядный адрес, указывающий на одну из ячеек оперативной памяти. К ней и подключается процессор для копирования данных из ячейки в один из своих регистров.

Для того чтобы процессор мог обрабатывать данные, ему нужны команды. Он должен знать, что следует сделать с теми байтами, которые хранятся в его регистрах. Эти команды поступают в процессор тоже из оперативной памяти, из областей, где хранятся программы. Команды тоже представлены в виде байтов. В процессе работы процессор часть данных интерпретирует непосредственно как данные, часть данных — как адресные данные, а часть — как команды. Совокупность всех возможных команд, которые может выполнить процессор над данными, образует систему команд процессора.

Список использованной литературы

2. Информатика: Базовый курс: / О.А. Акулов, Н.В.Медведев. 2-е изд., испр. и доп. – М.: Омега – Л, 2005.- 552с.

3. Информатика: Учебник. – 3-е перераб. изд. / Под ред. Н.В. Макаровой. – М.: Финансы и статистика, 2002. – 768с.: ил.

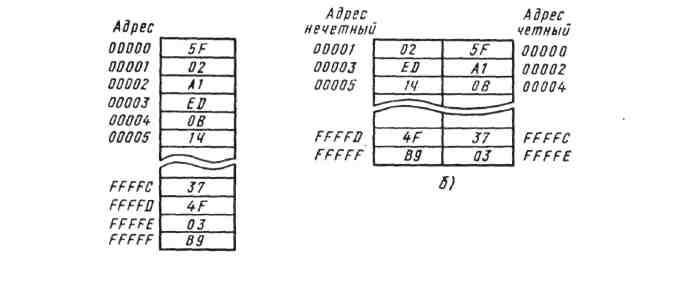

В ВМ на базе Intel 8086 первые байты слов могут иметь как четные, так и нечетные адреса в памяти. Если слово начинается с четного адреса, обращение к нему произойдет в одном цикле, в то время как обращение к слову с нечетным адресом младшего байта займет два цикла. Поэтому для сокращения времени выполнения программ целесообразно располагать слова в памяти так, чтобы их младшие байты имели четные адреса.

![]()

Рис. 1.5. Логическая (а) и физическая (б) организация памяти

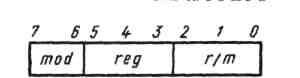

В зависимости от типа команды операнд может представлять собой байт или слово и храниться в РОН или памяти. В большинстве команд для адресации операндов используется специальный байт, который называется

постбайтом и размещается вслед за первым байтом, содержащим код операции.

![]()

Рис. 1.6. Структура постбайта

Постбайт, структура которого представлена на рис. 1.6, указывает способ адресации одного или двух операндов и состоит из трех полей. Поля mod и r/т задают местоположение одного операнда следующим образом: если mod=11, то операндом является содержимое регистра, двоичный код (номер) которого задается в 3-разрядном поле r/т в соответствии с табл. 1.1а.

Если тod=11, то в полях mod и r/т содержится информация, согласно которой устанавливается один из способов адресации - прямая, косвенная регистровая, по базе, индексная и по базе с индексированием. Если для реализации выбранного способа адресации требуется дополнительная адресная информация, то она указывается в одном или двух байтах в виде смещения disp, которое следует непосредственно за постбайтом. Наличие или отсутствие смещения и его размерность определяются полем mod следующим образом:

если mod = 00, то disp отсутствует;

если mod=01, то disp размерностью 1 байт указывается за постбайтом, причем перед использованием этого смещения при формировании исполнительного адреса ЕА оно расширяется со знаком до 16 разрядов (расширение со знаком подразумевает заполнение старшего байта значением знакового разряда, указанного в disp);

если mod=10, то за постбайтом следует 16-разрядное смещение disp, рассматриваемое как число со знаком.

Таблица 1.1а

Для каждой комбинации значений поля mod 00, 01 или 10 формирование исполнительного адреса ЕА определяется полем r/т в соответствии с табл. 1.1б. Исключение из описанных способов кодирования полей mod и r/т составляет случай mod=00, r/т=110, соответствующий EA = disp, причем disp- есть 16-разрядное смещение. Таким образом, при обращении к памяти имеется 24 варианта вычисления адреса ЕА, используемого в качестве смещения в сегменте при вычислении физического адреса.

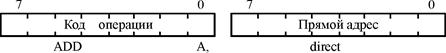

![]()

Рис. 1.7. Форматы команд центрального процессора

![]()

Поле reg постбайта используется для адресации тогда, когда в команде задаются два операнда. В этом случае второй операнд всегда находится в регистре, код которого указывается в поле постбайта в соответствии с табл. 1.1. В командах, где требуется только один операнд, поле reg постбайта используется совместно с байтом кода операции (КОП) для увеличения вариантов кодирования операций. Всего в ЦП используются восемь способов адресации, из которых пять реализуются с помощью постбайта. На рис. 1.7 представлены форматы команд, иллюстрирующие задание различных способов адресации.

Регистровая адресация. Операнд находится в одном из РОН, код которого указывается в байте КОП (рис. 1.7, а) или в постбайте при mod= 11 (рис. 1.7, б, в, д).

Непосредственная адресация. Операнд содержится в формате команды в виде одно- или двухбайтовой константы (рис 1.7, а, б). Этот способ задается особой комбинацией значений разрядов в поле КОП и может быть использован в большинстве команд с двумя операндами. Такие команды имеют постбайт, что делает возможным выполнение операций над константой и операндом, расположенным в памяти или регистре. Способ непосредственной адресации неприменим в командах загрузки сегментных регистров и в команде занесения данных в стек. В этих случаях используется промежуточная загрузка константы в один из регистров, указанных в табл. 1.1.

В командах с однобайтовыми операндами (w = 0) операнд имеет длину 1 байт и располагается в конце команды (рис. 1.7, а, б) в поле данных. В командах с операндами-словами (w = 1) операнд обычно занимает поле данных длиной 2 байт (рис. 1.7, а). Однако некоторые команды с операндами-словами могут иметь однобайтовый операнд, что указывается с помощью присвоения 1-разрядному полю s значения 1 (рис. 1.7, б). Если 5 = 1, то однобайтовое поле данных, содержащееся непосредственно в команде, перед использованием в операции расширяется со знаком до 16-разрядного слова. Расширение со знаком позволяет использовать 16-разрядные операнды в диапазоне значений от -128 до +127, которые в команде записываются однобайтовым операндом вместо двухбайтового. Двухбайтовый операнд используется в случаях, когда значение требуемого операнда (константы) выходит за пределы указанного диапазона.

Прямая адресация. Исполнительный адрес операнда задается с помощью двух байтов, которые следуют за первым байтом (рис. 1.7, г) или за постбайтом (рис. 1.7,д). Младший байт адреса идет по порядку первым. Прямая адресация позволяет обращаться к операндам в пределах одного сегмента памяти емкостью 64К байт.

Возможна также длинная прямая адресация, при которой команда содержит 16-разрядный базовый адрес сегмента, а также 16-разрядное смещение в сегменте (исполнительный адрес), что позволяет при программировании осуществить обращение к операнду, находящемуся в произвольном (не текущем) сегменте, т. е. в пределах всей памяти емкостью в 1М байт. Однако такой способ прямой адресации применим только в командах переходов и командах вызова подпрограмм, в которых он позволяет осуществлять межсегментные переходы. Невозможность применения этого способа адресации в командах, задающих операции над данными, представляет определенное неудобство.

Косвенная регистровая адресация. Исполнительный адрес операнда содержится в одном из регистров ВХ, SI или DI, код которого задается в постбайте (рис. 1.7, б, в, д).

Адресация с индексированием. В формате команды непосредственно за постбайтом задается 16-разрядный базовый адрес, а в постбайте указывается один из регистров ВХ, ВР, SI или DI, в котором хранится индекс (рис. 1.7, д). Адресация с индексированием логически эквивалентна адресации по базе с 16-разрядным смещением. Различие заключается в том, что 16-разрядное смещение интерпретируется как базовый адрес, а регистр хранит индекс. Однако поскольку любой из указанных четырех регистров может применяться как при адресации по базе, так и • при адресации с индексированием, указанное различие является несущественным.

Адресация по базе с индексированием. Если в предыдущих способах адресации либо базы, либо смещения были фиксированы при выполнении команды и задавались в формате команды непосредственно, то адресация по базе с индексированием позволяет задавать оба этих параметра в регистрах (рис. 1.7,б,в). Это дает возможность вычислить во время выполнения программы как базовый адрес структуры данных, так и смещение одного из ее элементов.

В завершение рассмотрения различных способов адресации отметим, что исполнительные адреса ЕА, получаемые описанными выше способами, являются в действительности 16-разрядными смещениями в сегменте. Как было показано на рис. 1.3, 20-разрядный физический адрес получается путем сложения смещения в сегменте с предварительно сдвинутым на четыре разряда влево базовым адресом сегмента. Поскольку имеется четыре сегментных регистра CS, DS, SS и ES, для выполнения каждого преобразования логического адреса в физический должен быть выбран определенный регистр, содержащий базовый адрес соответствующего сегмента. Это осуществляют аппаратные средства микропроцессора, которые автоматически выбирают сегментный регистр согласно цели каждого обращения к памяти, как показано в табл. 1.2. В таблице указан также источник логического адреса, определяющий смещение в сегменте.

В ряде случаев для эффективной передачи данных между сегментами удобно извлекать операнды, находящиеся в стековом сегменте, не прибегая к операциям со стеком. Это относится, например, к извлечению параметров подпрограмм, которые находятся глубоко в стеке. Для подобных целей существует специальный вид обращения к памяти с использованием базового регистра ВР. Данные, для доступа к которым используется регистр ВР, выбираются из стекового сегмента, причем содержимое регистра SS служит в этом случае базовым адресом, а смещение задается исполнительным адресом ЕА, в формировании которого участвует содержимое регистра ВР.

Читайте также: