Шифраторы и дешифраторы реферат

Обновлено: 02.07.2024

Дешифратор – это устройство, предназначенное для преобразования двоичного кода в напряжение логической единицы (логического нуля) на том выходе, номер которого совпадает со значением двоичного кода на входе. При n входах в полном дешифраторе имеется 2n выходов, т.е. для каждой комбинации входных сигналов имеется соответствующий выход. Дешифратор, у которого при n входах число выходов меньше 2n, называется неполным.

Вложенные файлы: 1 файл

срс 6.doc

Дешифраторы и шифраторы.

Дешифратор – это устройство, предназначенное для преобразования двоичного кода в напряжение логической единицы (логического нуля) на том выходе, номер которого совпадает со значением двоичного кода на входе. При n входах в полном дешифраторе имеется 2 n выходов, т.е. для каждой комбинации входных сигналов имеется соответствующий выход. Дешифратор, у которого при n входах число выходов меньше 2 n , называется неполным. Другое название дешифратора -декодер. Принцип работы полного трехразрядного дешифратора рассмотрим на примере его таблицы истинности.

Соответствующие таблице истинности ФАЛ имеют вид

Структурная схема трехразрядного дешифратора, синтезированная на основании полученных ФАЛ приведена на рис. 4.10,а, а его УГО - на рис. 4.10,б.

Рис. 4.10.Структурная схема и УГО трехразрядного дешифратора.

В общем случае логические уравнения для выходных переменных дешифратора n-разрядного числа имеют вид

Построенные по полученным формулам дешифраторы называются линейными. К преимуществу линейных дешифраторов можно отнести высокое быстродействие, поскольку входные переменные одновременно поступают на все элементы И. Одновременно, без дополнительных задержек, формируется и результат на выходах этих элементов. Очевидно, что для реализации линейного дешифратора n-разрядного числа необходимо иметь 2 n логических элементов И с n-входами. В существующих микросхемах логических элементов количество входов ограничено. Следовательно, ограничена и разрядность реализуемых на их основе линейных дешифраторов, что является недостатком. Кроме того, недостатком является и то, что предыдущие элементы, работающие на входы дешифратора, должны иметь высокую нагрузочную способность, т.е. должны быть рассчитаны на подключение большого числа логических элементов И. Каждый из входов дешифратора подключен к 0,5·2 n логическим элементам И. Поскольку нагрузочная способность базовых логических элементов ИС не превышает величины N=10¸20, то максимальная разрядность дешифрируемых чисел для линейных дешифраторов n=4¸5.

Указанного недостатка лишены пирамидальные дешифраторы. Принцип построения этих дешифраторов состоит в том, что сначала строят линейный дешифратор для двухразрядного числа X1, X2, для чего необходимы 2 2 =4 двухвходовые схемы И. Далее, каждая полученная конъюнкция логически умножается на входную переменную X3 в прямой и инверсной форме. Полученная конъюнкция снова умножается на входную переменную X4 в прямой и инверсной форме и т.д. Наращивая таким образом структуру, можно построить пирамидальный дешифратор на произвольное число входов. На рис. 4.11 приведена структура пирамидального дешифратора для трех разрядов.

>Рис. 4.11. Пирамидальный дешифратор для трехразрядного числа.

Характерным отличием пирамидальных дешифраторов от линейных является использование только двухвходовых логических элементов вне зависимости от разрядности дешифрируемого числа. В то же время количество логических элементов в пирамидальном дешифраторе больше. Однако следует иметь ввиду, что количество логических элементов, располагаемых в одном корпусе ИС, определяется главным образом требуемым количеством выводов. Следовательно, в одном корпусе ИС можно расположить большее число двухвходовых элементов, чем трехвходовых, четырехвходовых и т.д. И значит, пирамидальная структура дешифратора по числу корпусов ИС может оказаться более предпочтительной, чем линейная.

Шифраторы выполняют задачу обратную той, которую выполняют дешифраторы: появление логической единицы (логического нуля) на определенном входе приводит к появлению соответствующей кодовой комбинации на выходе. Также как и дешифраторы, шифраторы бывают полными и неполными. Работа восьмивходового полного шифратора задается следующей таблицей истинности:

Одними из очень важных элементов цифровой техники, а особенно в компьютерах и системах управления являются шифраторы и дешифраторы.

Когда мы слышим слово шифратор или дешифратор, то в голову приходят фразы из шпионских фильмов. Что-то вроде: расшифруйте депешу и зашифруйте ответ.

В этом нет ничего неправильного, так как в шифровальных машинах наших и зарубежных резидентур используются шифраторы и дешифраторы.

Шифраторы.

Таким образом, шифратор (кодер), это электронное устройство, в данном случае микросхема, которая преобразует код одной системы счисления в код другой системы. Наибольшее распространение в электронике получили шифраторы, преобразующие позиционный десятичный код, в параллельный двоичный. Вот так шифратор может обозначаться на принципиальной схеме.

К примеру, представим, что мы держим в руках обыкновенный калькулятор, которым сейчас пользуется любой школьник.

Поскольку все действия в калькуляторе выполняются с двоичными числами (вспомним основы цифровой электроники), то после клавиатуры стоит шифратор, который преобразует вводимые числа в двоичную форму.

Все кнопки калькулятора соединяются с общим проводом и, нажав, к примеру, кнопку 5 на входе шифратора, мы тут же получим двоичную форму данного числа на его выходе.

Конечно же, шифратор калькулятора имеет большее число входов, так как помимо цифр в него нужно ввести ещё какие-то символы арифметических действий, поэтому с выходов шифратора снимаются не только числа в двоичной форме, но и команды.

Если рассмотреть внутреннюю структуру шифратора, то несложно убедиться, что он выполнен на простейших базовых логических элементах.

Во всех устройствах управления, которые работают на двоичной логике, но для удобства оператора имеют десятичную клавиатуру, используются шифраторы.

Дешифраторы.

Дешифраторы относятся к той же группе, только работают с точностью до наоборот. Они преобразуют параллельный двоичный код в позиционный десятичный. Условное графическое обозначение на схеме может быть таким.

Если говорить о дешифраторах более полно, то стоит сказать, что они могут преобразовывать двоичный код в разные системы счисления (десятичную, шестнадцатиричную и пр.). Всё зависит от конкретной цели и назначения микросхемы.

Простейший пример. Вы не раз видели цифровой семисегментный индикатор, например, светодиодный. На нём отображаются десятичные цифры и числа к которым мы привыкли с детства (1, 2, 3, 4. ). Но, как известно, цифровая электроника работает с двоичными числами, которые представляют комбинацию 0 и 1. Что же преобразовало двоичный код в десятичный и подало результат на цифровой семисегментный индикатор? Наверное, вы уже догадались, что это сделал дешифратор.

Для справки. Микросхема К176ИД2 разрабатывалась для управления 7-ми сегментным светодиодным индикатором. Эта микросхема способна преобразовать двоичный код от 0000 до 1001, что соответствует десятичным цифрам от 0 до 9 (одна декада). Остальные, более старшие комбинации просто не отображаются. Выводы C, S, K являются вспомогательными.

У микросхемы К176ИД2 есть четыре входа (1, 2, 4, 8). Их ещё иногда обозначают D0 – D3. На эти входы подаётся параллельный двоичный код (например, 0001). В данном случае, двоичный код имеет 4 разряда. Микросхема преобразует код так, что на выходах (a – g) появляются сигналы, которые и формируют на семисегментном индикаторе десятичные цифры и числа, к которым мы привыкли. Так как дешифратор К176ИД2 способен отобразить десятичные цифры в интервале от 0 до 9, то на индикаторе мы увидим только их.

Ко входам дешифратора К176ИД2 подключены 4 тумблера (S1 - S4), с помощью которых на дешифратор можно подать параллельный двоичный код. Например, при замыкании тумблера S1 на 5 вывод микросхемы подаётся логическая единица. Если же разомкнуть контакты тумблера S1 – это будет соответствовать логическому нулю. С помощью тумблеров мы сможем вручную устанавливать на входах микросхемы логическую 1 или 0. Думаю, с этим всё понятно.

На схеме показано, как на входы дешифратора DD1 подан код 0101. На светодиодном индикаторе отобразится цифра 5. Если замкнуть только тумблер S4, то на индикаторе отобразится цифра 8. Чтобы записать число от 0 до 9 в двоичном коде достаточно четырёх разрядов: a3* 8 + a2* 4 + a1* 2 + a0* 1, где a0 – a3, - это цифры из системы счисления (0 или 1).

Представим число 0101 в десятичном виде 0101 = 0*8 + 1*4 + 0*2 + 1*1 = 4 + 1 = 5. Теперь взглянем на схему и увидим, что вес разряда соответствует цифре, на которую умножается 0 или 1 в формуле.

Дешифратор на базе технологии ТТЛ – К155ИД1 использовался в своё время для управления газоразрядным цифровым индикатором типа ИН8, ИН12, которые были очень востребованы в 70-е годы, так как светодиодные низковольтные индикаторы ещё были очень большой редкостью.

Всё изменилось в 80-е годы. Можно было свободно приобрести семисегментные светодиодные матрицы (индикаторы) и среди радиолюбителей прокатился бум сборки электронных часов. Самодельные электронные часы не собрал для дома только ленивый.

Такой код называют унитарным, поэтому дешифратор является преобразователем позиционного двоичного кода в унитарный. Так как возможное количество чисел, закодированных n-разрядным двоичным кодом, равно количеству наборов из и аргументов (N = 2″), то дешифратор, имеющий n входов, должен иметь 2n выходов. Такой дешифратор называют полным. Если часть входных наборов не используется, то дешифратор… Читать ещё >

Дешифраторы и шифраторы ( реферат , курсовая , диплом , контрольная )

Как отмечалось в параграфе 3.2, цифровые устройства делятся на комбинационные и последовательностные. К комбинационным относятся такие цифровые устройства, выходные сигналы которых зависят только от текущего значения входных сигналов. Эти устройства, в отличие от последовательностных, не обладают памятью. После завершения переходных процессов в этих устройствах на их выходах устанавливаются выходные величины, на которые характер переходных процессов влияния не оказывает.

Любое сложное цифровое устройство может быть разделено на комбинационную часть, выполняющую логические операции, и элементы памяти. В принципе комбинационная часть может быть выполнена на логических элементах, однако это слишком сложно и дорого. Гораздо проще для этого использовать готовые комбинационные устройства. К основным комбинационным устройствам относят дешифраторы, шифраторы, мультиплексоры (распределители), демультиплексоры и сумматоры.

Дешифраторы

Такой код называют унитарным, поэтому дешифратор является преобразователем позиционного двоичного кода в унитарный. Так как возможное количество чисел, закодированных n-разрядным двоичным кодом, равно количеству наборов из и аргументов (N = 2″), то дешифратор, имеющий n входов, должен иметь 2n выходов. Такой дешифратор называют полным. Если часть входных наборов не используется, то дешифратор называют неполным, и у него число выходов меньше 2n. Таким образом, в зависимости от входного двоичного кода на выходе дешифратора возбуждается только одна из выходных цепей, по номеру которой можно распознать входное число.

Дешифраторы применяют для расшифровки адресов ячеек запоминающих устройств, высвечивания букв и цифр на мониторах, индикаторах и других устройствах. Чаще всего они являются встроенными в БИС, как, например, в полупроводниковых запоминающих устройствах, однако они выпускаются и в виде ИС среднего уровня интеграции.

Проиллюстрируем реализацию дешифраторов на примере полного дешифратора трехразрядных чисел. Таблица истинности дешифратора представлена в табл. 3.5.

Таблица 3.5

Как видно, каждый выход xi равен единице только на одном наборе, поэтому работа дешифратора описывается восемью функциями — по числу выходов дешифратора, каждая из которых является конъюнкцией (логическим И) трех аргументов:

Схема трехразрядного полного дешифратора показана на рис. 3.12. Для реализации одной функции yi, нужен один трехвходовый конъюнктор. Так как на входах конъюнкторов присутствуют как прямые значения аргументов, так и инверсные, в схеме дешифратора необходимы три инвертора (см. рис. 3.12, а).

Рис. 3.12. Линейный дешифратор на три входа:

а — логическая схема; б — условное обозначение дешифратора с входами синхронизации и разрешения Часто дешифраторы выполняют с управляемой синхронизацией, при которой дешифрация кода будет произведена во время подачи синхронизирующего импульса, поступившего на вход С, лишь при условии, что на вход EN подан разрешающий единичный сигнал (см. рис. 3.12, б). Для реализации такого условия необходимы конъюнкторы с четырьмя входами, на четвертый вход которых поступает сигнал разрешения. Этот сигнал формируется двухвходовым конъюнктором при совпадении сигналов С и EN.

Число контактов у стандартного корпуса несложной ИС ограничено (14, 16 или 24), поэтому дешифраторы, выпускаемые в виде ИС, имеют небольшую разрядность входного кода (три, реже четыре). Так, например, в 16-контактном корпусе может быть помещен лишь трехразрядный полный дешифратор. Если требуется создать дешифратор большей разрядности, используют каскадное соединение дешифраторов небольшой разрядности.

Пример 3.1. Пусть на основе трехразрядных дешифраторов необходимо создать пятиразрядный (рис. 3.13).

Рис. 3.13. Схема наращивания размерности дешифратора.

Решение. Пятиразрядный дешифратор должен иметь 25 = 32 выходов. Разделим пять разрядов на младшие x2, x1, x0 и старшие x4, х3. Тогда младшие можно подать на входы четырех 3-разрядных дешифраторов второго каскада и сформировать 8 • 4 = 32 выхода. Используя входы разрешения . можно выбирать один из четырех дешифраторов второго каскада, на котором должен сформироваться единичный сигнал. Для этого старшие два разряда подадим на входы управляющего дешифратора первого каскада, а его выходы подключим к входам разрешения ?? дешифраторов первого каскада.

Рис. 3.14. Схема управления исполнительными устройствами технологической системы на основе дешифратора.

Шифраторы

Шифратор (coder) — это комбинационное устройство, выполняющее функции, обратные дешифратору. При подаче сигнала на один из его входов (унитарный код) на выходе должен образоваться соответствующий двоичный код.

Если число входов шифратора равно 2n, то число выходов, очевидно, должно быть равным п, т. е. числу разрядов двоичного кода, которым можно закодировать 2″ ситуаций.

Проиллюстрируем синтез схемы шифратора при п = 3. Таблица истинности имеет вид, приведенный в табл. 3.6.

Если количество входов настолько велико, что в шифраторе используются все возможные комбинации сигналов на выходе, то такой шифратор называется полным, если не все, то неполным. Число входов ивыходов в полном шифраторе связано соотношением п = 2 т , где п — число входов, т — число выходов.

Рассмотрим пример построения шифратора для преобразования десятиразрядного единичного кода (десятичных чисел от 0 до 9) в двоичный код. При этом предполагается, что сигнал, соответствующий логической единице, в каждый момент времени подаётся только на один вход.Условное обозначение шифратора и таблица соответствия кода.

Схема такого шифратора, на элементах ИЛИ.

Если на всех входах — логическая единица, то на всех выходах также логическая единица, что соответствует числу 0 в так называемом инверсном коде (1111).Если хотябы на одном входе имеется логический ноль, то состояние выходных сигналов определяется наибольшим номе ром входа, на котором имеется логический ноль, и не зависит от сигналов на входах, имеющих меньший номер.

Например, если на входе PRI — логический ноль, а на всех остальных входах — логическая единица, то на выходах имеются следующие сигналы: В1 - 0, В2 -1, В4-1, В8 -1, что соответствует числу 1 в инверсном коде (1110).

Основное назначение шифратора — преобразование номера источника сигнала в код (например, номера нажатой кнопки некоторой клавиатуры).

Для получения шифраторов с большим числом входов, т. е. наращивания размерности шифратора, объединяют микросхемы шифраторов с дополнительными выводами.

Дешифратором называется комбинационное устройство, преобразующее n-разрядный двоичный код в логический сигнал, появляющийся на том выходе, десятичный номер которого соответствует двоичному коду. Число входов и выходов в так называемом полном дешифраторе связано соотношением т= 2 n , где п — число входов, а т— число выходов. Если в работе дешифратора используется неполное число выходов, то такой дешифратор называется неполным. Так, например, дешифратор, имеющий 4 входа и 16 выходов, будет полным, а если бы выходов было только 10, то он являлся бы неполным.

Дешифратор имеет 10 инверсных выходов Y0, . ,Y9. Цифры определяют десятичное число, соответствующее заданному двоичному числу на входах. Очевидно, что этот дешифратор неполный.

Значение активного уровня (нуля) имеет тот выход, номер которого равен десятичному числу, определяемому двоичным числом на входе. Например, если на всех входах — логические нули, то на выходе Yo— логический ноль, а на остальных выходах — логическая единица. Если на входе А2 — логическая единица, а на остальных входах — логический ноль, то на выходе У2 — логический ноль, а на остальных выходах — логическая единица. Если на входе — двоичное число, превышающее 9 (например, на всех входах единицы, что соответствует двоичному числу 1111 и десятичному числу 15), то на всех выходах — логическая единица.

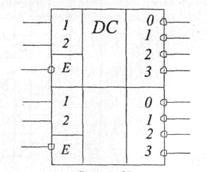

Помимо информационных имеется один или более входов, называемых входами разрешения, или адресными входами. Так, микросхема КР531ИД14 представляет собой два дешифратора 2 х 4, т. е. каждый дешифратор имеет два информационных входа и четыре инверсных выхода, атакже инверсный вход разрешения.

Цифры на входе (1,2) обозначают вес разряда двоичного числа, а цифры на выходе (0—3) определяют десятичное число, соответствующее заданному числу на входе.

При логической 1 на входе разрешения на всех выходах будут также логические 1. При активизации входа разрешения, т. е. при Е = 0, логический 0 появляется на том выходе дешифратора, номер которого соответствует десятичному эквиваленту двоичного числа, поданного на информационные входы. Благодаря наличию входа разрешения можно наращивать размерность дешифраторов. Так, используя 5 дешифраторов 2x4, можно построить дешифратор 4x16.

Очевидно, что если использовать две микросхемы КР531ИД14, т. е. четыре дешифратора 2x4, можно построить неполный дешифратор.

Дешифратор — одно из широко используемых логических устройств. Его применяют для построения различных комбинационных устройств.

Это основано на том обстоятельстве, что на выходе дешифратора вырабатываются все возможные логические произведения всех входных переменных (конъюнктивные минтермы).

Читайте также: