Реферат регистры и их виды и

Обновлено: 08.07.2024

Регистры сдвига предназначены для выполнения операций приема, хранения и выдачи двоичных чисел в последовательном или параллельном кодах, сдвига кода вправо или влево на заданное число разрядов, задержки передаваемой информации на т тактов. В этих регистрах каждый тактовый импульс инициирует введение разряда двоичного числа в первый триггер и сдвиг содержимого последующих триггеров на один разряд… Читать ещё >

Регистры. Электротехника и электроника ( реферат , курсовая , диплом , контрольная )

Регистром называют устройство, предназначенное для хранения цифровых кодов, сдвига чисел, преобразования параллельного кода в последовательный и выполнения других операций с двоичными числами. Структура регистра представляет собой упорядочснную последовательность триггерных ячеек и комбинационную схему, обеспечивающую ввод, вывод и выполнение логических преобразований. Обычно в регистрах используют универсальные //(-триггеры или //-триггеры задержки. По способу ввода чисел регистры делят на последовательные, параллельные и комбинированные, а, но функциональному назначению выделяют регистры памяти (накопительные) и сдвига.

Регистры памяти предназначены для хранения двоичной информации небольшого объема: байта (8 бит) или двухбайтового слова (16 бит). Структурно они представляют собой п синхронных D-триггеров для хранения одного разряда двоичного числа и комбинационных схем совпадения для разделения операций записи и чтения (рис. 14.8).

Рис. 14.8. Структура регистра памяти.

Ввод кода двоичного числа X = (хп…Х2Хi) осуществляется одновременно во все разряды при подаче единичного сигнала на вход синхронизации С. Вывод хранимого кода на шину Y производят через выходные схемы совпадения при подаче единичного сигнала на вход разрешения чтения с2.

Наращивание разрядности регистров памяти получают добавлением аналогичных регистров и объединением соответствующих входов синхроимпульсов и сброса.

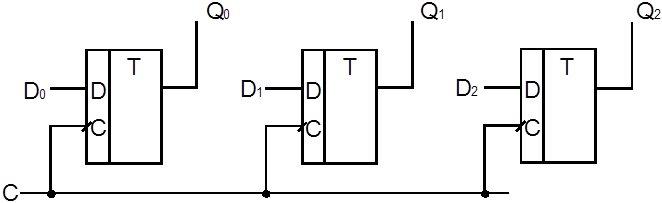

Регистры сдвига предназначены для выполнения операций приема, хранения и выдачи двоичных чисел в последовательном или параллельном кодах, сдвига кода вправо или влево на заданное число разрядов, задержки передаваемой информации на т тактов. В этих регистрах каждый тактовый импульс инициирует введение разряда двоичного числа в первый триггер и сдвиг содержимого последующих триггеров на один разряд вправо. Структура регистра сдвига содержит п двухступенчатых триггеров (рис. 14.9, а).

В трехразрядном регистре сдвига вправо младший разряд вводимого числаХ = (х2ХХ0), например X = 101, подается на вход и записывается в первую ячейку в момент окончания первого синхроимпульса. С приходом следующего сигнала синхронизации (рис. 14.9, б) единица из ячейки первого разряда переносится в следующую, а в нее заносится следующий разряд числах! = 0. За три такта в ре;

Рис. 14.9. Структура однонаправленного регистра сдвига (а) и временная диаграмма (б).

гистр будет записано трехразрядное число, т. е. на выходах ячеек образуются сигналы Q2 = 1, Q = О, Q0 = 1. За следующие три такта хранимое число будет выведено в последовательном коде на выход Y. Для параллельного вывода данных к выходам Q2, QuQo следует подключить схемы совпадения, открываемые разрешающим чтение сигналом. Для построения регистра, смещающего код числа влево, выходы последующего триггера соединяют с входами предыдущего.

Использование в цепях межкаскадных связей комбинационных схем совпадения обеспечивает возможность электрического управления порядком соединения ячеек для получения реверсивного регистра, осуществляющего сдвиг числа влево и вправо. Одной из областей применения реверсивных регистров служит программная организация операций умножения и деления, основанных на том, что сдвиг двоичного числа на один разряд вправо или влево соответствует его умножению или делению на два. Получили распространение комбинированные (универсальные) регистры, в которых управляющие комбинационные схемы обеспечивают параллельный или последовательный ввод и вывод данных с возможностью сдвига вправо и влево.

Регистром называется последовательностное функциональное устройство, предназначенное для хранения двоичной комбинации заданное время. Регистры можно построить на базе RS, JK и Dтриггеров. Наиболее удобно строить регистры на базе D-триггер, потому что они имеют один информационный вход. Число разрядов регистра равно числу используемых триггеров т.к. один триггер хранит один разряд двоичной комбинации. Одиночный триггер можно рассматривать как одноразрядный регистр памяти.

Регистры по способу записи и считывания информации делятся на параллельные (памяти) и последовательные (сдвиговые).

Регистры прежде всего используются для хранения информации. Но на базе регистров также можно построить различные устройства.

На регистрах сдвига наиболее просто реализовать преобразователь последовательного кода в параллельный и наоборот. Их применяют в устройствах аппаратного умножения и деления двоичных чисел, в кодирующих устройствах для синтеза помехоустойчивых кодов, которые могут обнаруживать и исправлять ошибки и т.д.

Регистры сдвига можно использовать также для построения счётчиков, которые носят обще название кольцевые. Часто их еще называют по имени используемого кода.

2 Параллельные регистры

Параллельным (памяти) регистром называется последовательностное функциональное устройство, состоящее из набора синхронных триггеров с независимыми информационными выходами и общим синхронизирующим входом и предназначенное для хранения двоичной комбинации. Число информационных входов и выходов (разрядов) равно числу используемых триггеров.

Для создания регистров памяти в интегральном исполнении используются D - триггеры статических и динамических и называют их соответственно статическими и динамическими регистрами. Схема трехразрядного динамического регистра памяти, построенного из динамических D - триггеров показана на рисунке 1.

Данный регистр работает следующим образом. При появлении на синхронизирующем входе C перепада с 0 на 1 информация, находящаяся на выходах D2. D0 записывается в триггеры и хранится там до появления следующего перепада с 0 на 1 на входе C. Запись информации в регистр памяти, построенный из статистических D - триггеров осуществляется так же, как и в одиночный статический.

Рисунок 1 Параллельный регистр

Запись и считывание информации происходит за один такт.

В некоторых регистрах памяти предусмотрена возможность высокоомного состояния выходов и установка выходов в нуль (сброс).

Регистры памяти применяют для промежуточного кратковременного хранения данных и для организации параллельного ввода-вывода в информационно-измерительных и вычислительных устройствах.

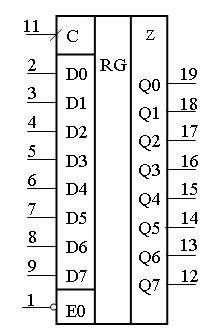

Примером параллельного регистра в интегральном исполнении может служить регистр 1533ИР37, УГО которого показано на рисунке 2.

Рисунок 2 Параллельный регистр 1533ИР37

Он представляет собой восьмиразрядный буферный регистр. Регистр построен на динамических D-триггерах, переключение производится положительным фронтом тактового импульса. Регистр имеет восемь входов данных D0 – D7 и восемь выходов Q0 – Q7. Когда на специальный вход подается низкий уровень, то после поступления положительного перепада на тактовый вход С входная информация появляется на выходах Q. Если на установлен высокий уровень, то выходные буферные каскады переводятся в высокоимпедансное состояние (состояние Z). При низком уровне тактового сигнала С триггеры регистра находятся в режиме хранения информации, зафиксированной при прохождении предыдущего положительного фронта импульса С.

3 Сдвиговые регистр

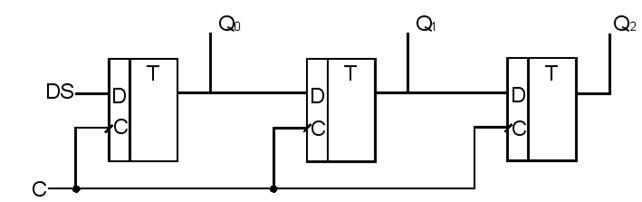

Регистром сдвига называется последовательностное функциональное устройство, состоящее из соединенных последовательно синхронных триггеров с общим синхронизирующим входом, и в этом устройстве происходит сдвиг записанной в него двоичной комбинации на один разряд при появлении активного перепада сигнала на синхронизирующем входе. Разрядность регистра равна числу используемых триггеров.

Регистры сдвига в интегральном исполнении создаются, в основном, из динамических D - триггеров и могут сдвигать записанную в них информацию в сторону старших разрядов (вправо), или в обе стороны. В последнем случае они называются реверсивными.У любого регистра сдвига обязательно есть вход последовательного ввода информации. У реверсивных регистров таких входов два: один для ввода информации при сдвиге вправо, другой - для ввода при сдвиге влево. Возможность последовательного вывода информации так же существует у любого регистра сдвига. Для этого у него имеется специальный выход последовательного вывода, а если предусмотрен параллельный вывод информации, то в качестве выхода для последовательного вывода используется выход последнего (старшего) разряда регистра.

Схема трехразрядного регистра сдвига с последовательным вводом, параллельным выводом и сдвигом информации в сторону старших разрядов (вправо), построенная из D - триггеров показана на рисунке 3.

Рисунок 3 Регистр сдвига

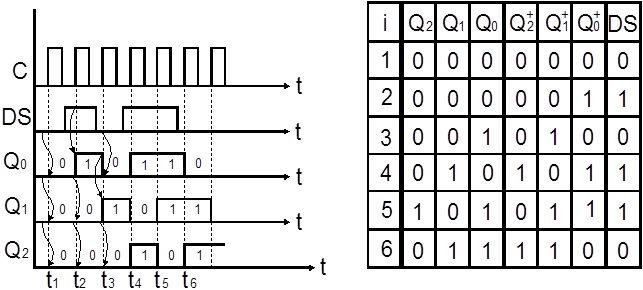

Работу схемы удобнее пояснять с помощью временной диаграммы, показанной на рисунке 4. При появлении активного перепада импульса на синхронизирующем входе C (в данном случае это перепад с 0 на 1) информация, находящаяся в этот момент на входе каждого триггера переписывается на его выход. Стрелки на рисунке 4 показывают, какая именно информация (0 или 1) переписывается.

Рисунок 4 Временная диаграмма Рисунок 5 Таблица переходов

Выход первого триггера считается младшим разрядом, а выход последнего триггера - старшим разрядом регистра.

Пускай перед началом работы на выходах всех триггеров и на входе DS находятся нули, т.е. в регистре записана комбинация 000. В момент на входах каждого триггера находился нуль, поэтому он и перепишется на выходы всех триггеров. Комбинация в регистре после - 000. В момент (когда но входе С появился перепад с 0 на 1) на входе DS находилась единица, а на выходах остальных триггеров нули, поэтому в первый триггер запишется единица, а во второй и третий нули. Комбинация в регистре после - 001. В момент на входе DS и на входе третьего триггера находились нули, а на входе второго -единица, поэтому в первый и третий триггер запишутся нули, а во второй - единица. Комбинация в регистре после - 010 и т.д. Информацию на входе DS необходимо установить до появления активного перепада на входе C.

Работу регистра сдвига можно пояснить и с помощью таблицы состояний (функций перехода), приведенной на рисунке 5. Каждая строка таблицы соответствует состоянию выходов регистра до появления активного перепада (столбцы . ) и после его появления (столбцы . ). В столбце DS обозначен уровень сигнала на входе DS перед самым появлением активного перепада, а в столбце - номер импульса, который вызвал состояние . .

Временная диаграмма и таблица состояния наглядно демонстрирует движение информации в регистре сдвига.

Для расширения функциональных возможностей у регистра сдвига может предусматриваться параллельный ввод информации, переключение в высокоомное состояние выходов, установка в нулевое состояние и др.

Регистр сдвига можно использовать и как регистр памяти. Только в этом случае для ввода информации через последовательный вход требуется число тактов равное разрядности регистра, а не один, как у регистров памяти.

Примером универсального регистра может служить микросхема К155ИР13 (рисунок 6). Режим ее работы задается уровнями сигналов на входах SR и SL (см. таблицу состояний регистра). При сдвиге вправо сигнал со входа DR переписывается в младший разряд DO0 по фронту каждого тактового импульса, а старая информация выхода DO7 теряется. При сдвиге влево информация с входа DL записывается на выход DO7, а информация с выхода DO0 теряется. При SL = SR = 1 микросхема работает как параллельный регистр, запись информации в который с входов DIпроисходит по фронту тактового импульса. При подаче 0 на вход все триггеры регистра сбрасываются в нулевое состояние.

![рис. 3.72]()

Что такое регистр?

Регистр — это последовательностное логическое устройство, используемое для хранения n-разрядных двоичных чисел и выполнения преобразований над ними. Регистр представляет собой упорядоченную последовательность триггеров, число которых соответствует числу разрядов в слове. С каждым регистром обычно связано комбинационное цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами.

Типичными являются следующие операции:

- прием слова в регистр;

- передача слова из регистра;

- поразрядные логические операции;

- сдвиг слова влево или вправо на заданное число разрядов;

- преобразование последовательного кода слова в параллельный и обратно;

- установка регистра в начальное состояние (сброс).

Фактически любое цифровое устройство можно представить в виде совокупности регистров, соединенных друг с другом при помощи комбинационных цифровых устройств.

Классификация регистров

- накопительные (регистры памяти, хранения);

- сдвигающие.

В свою очередь сдвигающие регистры делятся: - по способу ввода-вывода информации на:

• параллельные,

• последовательные,

• комбинированные; - по направлению передачи информации на:

• однонаправленные,

• реверсивные.

Накопительный регистр с параллельными вводом и выводом информации

Рассмотрим накопительный регистр с параллельными вводом и выводом информации (рис. 3.72).

Основой регистра являются D-триггеры, которые на своих выходах повторяют значения сигналов на входах X1 — Х4 (информационные входы) при логическом сигнале 1 на входе синхронизации (т. е. осуществляется параллельный ввод входной информации в регистр).

Таким образом, осуществляется параллельный вывод информации. В качестве примера рассмотрим микросхему регистра К155ИР15. Приведем условное обозначение и таблицы внутренних и выходных состояний (рис. 3.73).

Схема сдвигающего регистра

Таким образом, за четыре такта осуществляется последовательный ввод в регистр 4-разрядного двоичного числа. В качестве примера приведем микросхему сдвигающего регистра К155ИР13 и его таблицу состояний (рис. 3.75).

Регистр процессора - сверхбыстрая оперативная память внутри процессора, предназначенная прежде всего для хранения промежуточных результатов вычисления.

По типу приёма и выдачи информации различают 2 типа регистров:

- С последовательным приёмом и выдачей информации — сдвиговые регистры.

- С параллельным приёмом и выдачей информации — параллельные регистры.

По назначению регистры различаются на:

- аккумулятор — используется для хранения промежуточных результатов арифметических и логических операций и инструкций ввода-вывода;

- флаговые — хранят признаки результатов арифметических и логических операций;

- общего назначения — хранят операнды арифметических и логических выражений, индексы и адреса;

- индексные — хранят индексы исходных и целевых элементов массива;

- указательные — хранят указатели на специальные области памяти (указатель текущей операции, указатель базы, указатель стека);

- сегментные — хранят адреса и селекторы сегментов памяти;

· управляющие — хранят информацию, управляющую состоянием процессора, а также адреса системных таблиц.

Начиная с 80386 процессоры Intel предоставляют 16 основных регистров для пользовательских программ плюс еще 11 регистров для работы с мультимедийными приложениями (MMX(Multimedia Extension)) и числами с плавающей запятой (FPU/NPX (Float Point Unit / Numerical Processor Extension)). Все команды так или иначе изменяют значения регистров, и всегда быстрее и удобнее обращаться к регистру, чем к памяти.

Из реального (но не из виртуального) режима помимо основных регистров доступны так же регистры управления памятью (GDTR, IDTR, TR, LDTR), регистры управления (CR0, CR1 – CR4), отладочные регистры (DR0 – DR7) и машинно-специфичные регистры, но они не применяются для решения повседневных задач.

Регистры общего назначения.

Остальные четыре регистра – ESI (индекс источника), EDI (индекс приемника), EBP (указатель базы), ESP (указатель стека) - имеют более конкретное назначение и применяются для хранения всевозможных временных переменных. Регистры ESI и EDI необходимы в строковых операциях, EBP и ESP – при работе со стеком. Так же как в случае с регистрами EAX – EDX, младшие половины этих четырех регистров называются SI, DI, BP и SP соответственно, и в процессорах до 80386 только они и присутствовали.

(Регистры общего назначения)

Сегментные регистры.

При использовании сегментированных моделей памяти для формирования любого адреса нужны два числа – адрес начала сегмента и смещение искомого байта относительно этого начала (в бессегментной модели памяти flat адреса начала всех сегментов равны). Операционные системы (кроме DOS) могут размещать сегменты, с которыми работает программа пользователя, в разных местах памяти и даже временно записывать их на диск, если памяти не хватает. Так как сегменты способны оказаться где угодно, программа обращается к ним, применяя вместо настоящего адреса начала сегмента 16-битное число, называемое селектором. В процессорах Intel предусмотрены шесть 16-битных регистров – CS, DS, ES, FS, GS, SS, где хранятся селекторы. Это означает, что в любой момент можно изменить параметры, записанные в этих регистрах.

В отличие от DS, ES, GS, FS, которые называются регистрами сегментов данных, CS и SS отвечают за сегменты двух особенных типов – сегмента кода и сегмент стека. Первый содержит программу, исполняющуюся в данный момент, следовательно, запись нового селектора в этот регистр приводит к тому, что далее будет исполнена не следующая по тексту программы команда, а команда из кода, находящегося в другом сегменте, с тем же смещением. Смещение очередной выполняемой команды всегда хранится в специальном регистре EIP (указатель инструкции, 16-битная форма IP), запись в который также приведет к тому, что далее будет исполнена какая-нибудь другая команда. На самом деле все команды передачи управления – перехода, условного перехода, цикла, вызова подпрограммы и т. п. – и осуществляют эту самую запись в CS и EIP.

Стек.

Регистр флагов.

Еще один важный регистр, использующийся при выполнении большинства команд, - регистр флагов. Его младшие 16 бит, представлявшие собой весь этот регистр до процессора 80386, называются FLAGS. В E FLAGS каждый бит является флагом, то есть устанавливается в 1 при определенных условиях или установка его в 1 изменяет поведение процессора. Все флаги, расположенные в старшем слове регистра, имеют отношение к управлению защищенным режимом, поэтому будем рассматривать только регистр FLAGS.

- CF – флаг переноса. Устанавливается в 1, если результат предыдущей операции не уместился в приемнике и произошел перенос старшего бита или если требуется заем (при вычитании), в противном случае – в 0. Например, после сложения слова 0FFFFh и 1, если регистр, в который надо поместить результат, - слово, в него будет записано 0000h и флаг CF=1.

- PF – флаг четности. Устанавливается в 1, если младший байт результата предыдущей команды содержит четное число битов, равных 1, и в 0, если нечетное. Это не тоже самое, что делимость на два. Число делится на 2 без остатка, если его самый младший бит равен нулю, и не делится, когда он равен 1.

- AF – флаг полупереноса или вспомогательного переноса. Устанавливается в 1, если в результате предыдущей операции произошел перенос (или заем) из третьего бита в четвертый. Этот флаг используется автоматически командами двоично-десятичной коррекции.

- ZF – флаг нуля. Устанавливается в 1, если результат предыдущей команды – ноль.

- SF – флаг знака. Он всегда равен старшему биту результата.

- TF – флаг ловушки. Он был предусмотрен для работы отладчиков, не использующих защищенный режим. Установка его в 1 приводит к тому, что после выполнения каждой программной команды управление временно передается отладчику (вызывается прерывание 1 – описание команды INT).

- IF – флаг прерываний. Сброс этого флага приводит к тому, что процессор перестает обрабатывать прерывания от внешних устройств (описание команды INT). Обычно его сбрасывают на короткое время для выполнения критических участков кода.

- DF – флаг направления. Он контролирует поведения команд обработки строк: когда он установлен в 1, строки обрабатываются в сторону уменьшения адресов, когда DF=0 – наоборот.

- OF – флаг переполнения. Он устанавливается в 1, если результат предыдущей арифметической операции над числами со знаком выходит за допустимые для них пределы. Например, если при сложении двух положительных чисел получается число со старшим битом, равным единице, то есть отрицательное, и наоборот.

Флаги IOPL (уровень привилегий ввода-вывода) и NT (вложенная задача) применяются в защищенном режиме.

Читайте также: