Использование сумматоров в вычислительной технике реферат

Обновлено: 04.07.2024

Комбинационные сумматоры находят широкое применение в арифметических устройствах вычислительных систем.

Двоичным сумматором называется логическое устройство (узел), выполняющее операцию сложения двух двоичных чисел.

В сумматорах параллельного действия слагаемые числа поступают на входы сумматора в параллельном коде, результат выдается параллельным же кодом на его выходах.

Таким образом, комбинационный сумматор n-разрядных двоичных чисел представляет собой дискретной устройство, имеющее 2n входов и n выходов. Такое устройство называется многоразрядным сумматором. Многоразрядный сумматор представляет собой совокупность так называемых одноразрядных сумматоров, каждый из которых формирует значение только одного из разрядов суммы.

Одноразрядные сумматоры можно классифицировать по количеству входов на следующие виды:

- двухвходовые, именуемые полусумматорами;

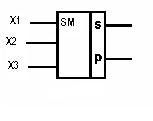

- трехвходовые, именуемые полными сумматорами.

Одноразрядные сумматоры применяются для обработки последовательных кодов, а соответствующим образом соединенная совокупность таких сумматоров образует многоразрядный сумматор, предназначенный для обработки параллельных кодов.

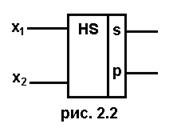

Одноразрядный полусумматор (HS) имеет два входа и два выхода (Рисунок 2.2). С выхода S снимается сигнал суммы (S), а с выхода Р - сигнал переноса (Р).

Функционирование полусумматора описывается таблицей соответствия (истинности), изображенной в виде таблицы 2.1

Из таблицы 2.1 получаем:

Видим, что логическая функция суммы S соответствует функции “неравнозначность” (сложение по модулю 2), а логическая функция переноса Р - функции “конъюнкция”.

Построив эти функции в заданном базисе, получим функциональную схему полусумматора. Схема HS в базисе И, ИЛИ, НЕ представлена на рисунке 2.3 а.

Для сокращения числа логических элементов проведем некоторые преобразования логических функций S и Р. Выразим функцию S в КНФ (методом двойной инверсии или используя распределительный закон) и проведем преобразования:

Функциональная схема такого полусумматора представлена на рисунке 2.3 б (в базисе И, ИЛИ, НЕ).

Полусумматоры могут применяться как сумматоры по модулю 2. В этом случае используется один выход S. Во многих сериях ИМС полусумматор имеется как отдельный логический элемент.

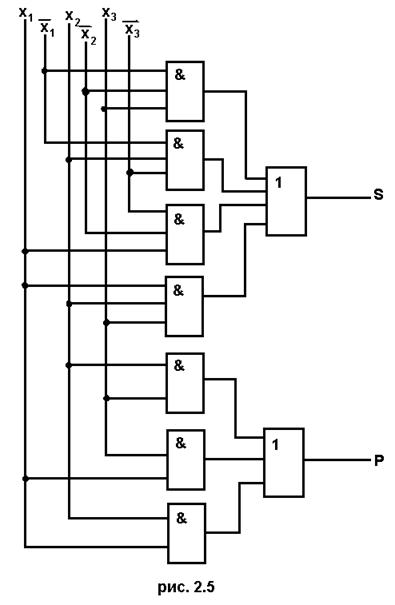

Схема сумматора, построенная по этим выражениям в базисе И, ИЛИ, НЕ, представлена на рисунке 2.5.

Так как быстродействие комбинационных схем определяется временем задержки входных сигналов логическими элементами, т.е. количеством элементов в цепях распространения сигналов, то приведенная схема полного сумматора по быстродействию наилучшая, хотя и обладает аппаратурной избыточностью.

для построения полного сумматора, хотя схема последнего

Для реализации схемы полного сумматора на полусумматорах преобразуем логические функции S и Р следующим образом.

Первый полусумматор (HS1) имеет входы х2 и х3, второй (HS2) - входы х1 и SHS1.

Соответствующая этим функциям структурная схема полного сумматора изображена на рисунке 2.6.

С помощью одноразрядных сумматоров можно построить суммирующие устройства для сложения многоразрядных двоичных чисел, которые могут быть последовательного или параллельного действия.

Наиболее употребительны сумматоры параллельного действия, так называемые многоразрядные сумматоры, которые строятся из полных сумматоров, соединенных определенным образом так, что сигнал (выход Р) переноса предыдущего разряда поступает на третий вход последующего разряда (Рисунок 2.7). На первый и второй входы каждого полного сумматора поступают цифры одноименных разрядов слагаемых чисел (кодов).

Время суммирования определяется временем передачи сигнала переноса от младшего разряда к старшему:

где - время образования суммы в полном сумматоре;

n - разрядность сумматора;

tn - время распространения переноса в одном разряде.

Поскольку , то быстродействие суммирующего устройства в основном зависит от времени распространения сигнала переноса .

Быстродействие суммирующего устройства параллельного действия значительно выше, чем последовательного.

Кроме комбинационных суммирующих устройств применяются накапливающие суммирующие устройства (сумматоры с памятью), которые не только суммируют слагаемые, но и запоминают полученную сумму. В качестве элементов памяти, как правило, применяются триггеры со счетным входом. Одноразрядный накапливающий сумматор содержит схему ИЛИ на 3 входа и триггер со счетным входом, у которого нулевой выход является инверсным динамическим (рисунок 2.8).

Читайте также: