Архитектура набора команд кратко

Обновлено: 05.07.2024

Архитектура набора команд служит границей между аппаратурой и программным обеспечением и представляет ту часть системы, которая видна программисту.

Двумя основными архитектурами набора команд, используемыми компьютерной промышленностью на современном этапе развития вычислительной техники являются архитектуры CISC и RISC. Известны также архитектуры MISC и VLIW

Лидером в разработке микропроцессоров с полным набором команд (CISC - Complete Instruction Set Computer) считается компания Intel со своей серией x86 и Pentium. Эта архитектура является практическим стандартом для рынка микрокомпьютеров.

Архитектура процессоров компании Intel основана на системе команд CISC (Complex Instruction Set Computer) – полной системе команд переменной длины. Команды процессора могут иметь длину от 8 до 108 бит, и процессор должен последовательно декодировать инструкцию после определения её границ. Первые процессоры для персональных компьютеров были скалярными устройствами ( то есть могли в каждый момент времени выполнять только одну команду), конвейерная обработка ( то есть одновременное выполнение нескольких команд на разных стадиях конвейера применялась лишь в больших ЭВМ).

Для CISC-процессоров характерно:

Ø сравнительно небольшое число регистров общего назначения;

Ø большое количество машинных команд, некоторые, из которых нагружены семантически аналогично операторам высокоуровневых языков программирования и выполняются за много тактов;

Ø большое количество методов адресации;

Ø большое количество форматов команд различной разрядности;

Ø преобладание двухадресного формата команд;

Ø наличие команд обработки типа регистр-память.

Позже появились процессоры, основанные на архитектуре RISC (Reduced Instruction Set Computer) – сокращённом наборе команд компьютера фиксированной длины, которая была оптимизирована для суперскалярных (с возможностью выполнения нескольких команд одновременно) конвейерных вычислений.

Зачатки этой архитектуры уходят своими корнями к компьютерам CDC6600, разработчики которых (Торнтон, Крэй и др.) осознали важность упрощения набора команд для построения быстрых вычислительных машин. Эту традицию упрощения архитектуры С. Крэй с успехом применил при создании широко известной серии суперкомпьютеров компании Cray Research.

Однако окончательно понятие RISC в современном его понимании сформировалось на базе трех исследовательских проектов компьютеров: процессора 801 компании IBM, процессора RISC университета Беркли и процессора MIPS Стенфордского университета.

Для RISC-процессоров характерно:

Ø архитектура, отделяющая команды обработки от команд работы с памятью;

Ø эффективная конвейерная обработка;

Ø система команд разрабатывалась таким образом, чтобы выполнение любой команды занимало небольшое количество машинных тактов (предпочтительно один машинный такт);

Ø логика выполнения команд, с целью повышения производительности, ориентировалась на аппаратную, а не на микропрограммную реализацию (чтобы упростить логику декодирования команд использовались команды фиксированной длины и фиксированного формата);

Ø наличие достаточно большого регистрового файла (в типовых RISC-процессорах реализуются 32 или большее число регистров по сравнению с 8 - 16 регистрами в CISC-архитектурах), что позволяет большему объему данных храниться в регистрах на процессорном кристалле большее время и упрощает работу компилятора по распределению регистров под переменные;

Ø для обработки, как правило, используются трехадресные команды, что помимо упрощения дешифрации дает возможность сохранять большее число переменных в регистрах без их последующей перезагрузки.

Ко времени завершения университетских проектов (1983-1984 гг.) обозначился также прорыв в технологии изготовления сверхбольших интегральных схем. Простота архитектуры и ее эффективность, подтвержденная этими проектами, вызвали большой интерес в компьютерной индустрии и с 1986 года началась, активная промышленная реализация архитектуры RISC. К настоящему времени эта архитектура прочно занимает лидирующие позиции на мировом компьютерном рынке рабочих станций и серверов.

Развитие архитектуры RISC в значительной степени определялось прогрессом в области создания оптимизирующих программаторов (компиляторов). Именно современная техника программирования позволяет эффективно использовать преимущества большего регистрового файла, конвейерной организации и большей скорости выполнения команд. Современные компиляторы используют также преимущества другой оптимизационной техники для повышения производительности, обычно применяемой в процессорах RISC: реализацию задержанных переходов и суперскалярной обработки, позволяющей в один и тот же момент времени выдавать на выполнение несколько команд. Архитектуры процессоров CISC и RISC развивались практически независимо, однако в отдельных модификациях процессоров AMD удалось совместить обе архитектуры. То есть микроядро процессора работает на основе инструкций RISC, а специальный блок интерпретирует команды CISC для обеспечения совместимости с программами для процессоров х86.

Minimum instruction set computer — вычисления с минимальным набором команд. Дальнейшее развитие идей команды Чака Мура, который полагает, что принцип простоты, изначальный для RISC-процессоров, слишком быстро отошёл на задний план. В пылу борьбы за максимальное быстродействие, RISC догнал и перегнал многие CISC процессоры по сложности. Архитектура MISC строится на стековой вычислительной модели с ограниченным числом команд (примерно 20-30 команд).

Very long instruction word — сверхдлинное командное слово. Архитектура процессоров с явно выраженным параллелизмом вычислений, заложенным в систему команд процессора. Являются основой для архитектуры EPIC. Ключевым отличием от суперскалярных CISC-процессоров является то, что для них загрузкой исполнительных устройств занимается часть процессора (планировщик), на что отводится достаточно малое время, в то время как загрузкой вычислительных устройств для VLIW-процессора занимается компилятор, на что отводится существенно больше времени (качество загрузки и, соответственно, производительность теоретически должны быть выше). Примером VLIW-процессора является Intel Itanium.

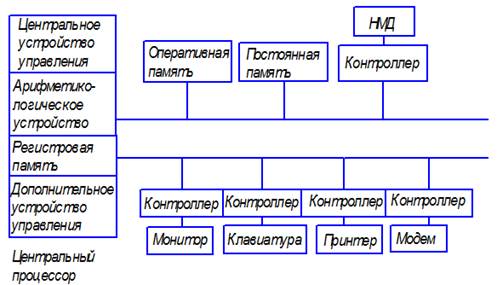

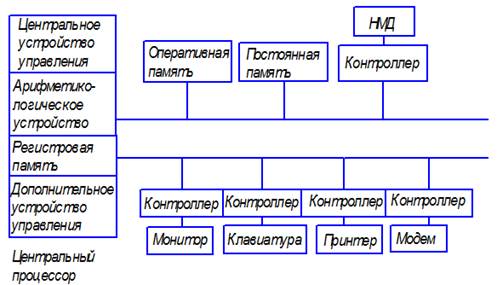

Центральный процессор в персональных компьютерах представляет собой микропроцессор, то есть, построен на одной микросхеме. В его состав входят:

•Центральное устройство управления - комплекс средств автоматического управления процессами передачи и обработки информации;

•Арифметико-логическое устройство - устройство, осуществляющее обработку информации и выработку признаков управляющих сигналов.

•Внутренняя память процессора:

-Постоянная память устройства управления.

Рис. 1 Обобщенная структурная схема ПК

Модули оперативной и постоянной памяти, связаны с микропроцессором напрямую. Остальные устройства (монитор, клавиатура, накопители на магнитных носителях и т.д.) связаны с микропроцессором через контроллеры ввода-вывода, которые, в свою очередь, связаны с микропроцессором через системную шину.

Микропроцессор является ядром ЭВМ. Он осуществляет обработку данных и функции управления системой. К функциям управления системой относятся:

•инициирование операций ввода-вывода;

•управление доступом к основной памяти;

•обработка системных событий – прерываний;

•организация многозадачных режимов работы.

Организация центрального процессора определяется архитектурой и принципами работы ЭВМ ( состав и форматы команд, организация памяти). Логическая структура включает ряд функциональных средств:

•средства обработки информации;

•средства управления системой и программами;

•управление интерфейсом и каналами.

Структурно эти средства разбиваются на центральное устройство управления, АЛУ, внутреннюю память и управляющие устройства, связанные с конкретными устройствами вычислительной машины.

Центральное устройство управления принимает и расшифровывает команды, формирует адреса команд и операндов, формирует последовательности управляющих сигналов и обеспечивает координацию работы всех функциональных узлов, посредством выработки синхронизирующих сигналов.

Внутренняя память входит в состав первого уровня и связана с АЛУ и другими блоками центрального процессора непосредственно и имеет скорость работы соизмеримую со скоростью работы блоков процессора.

•Управляющая память входит в состав центрального устройства управления и относится к классу постоянной памяти. Этот вид памяти используется для хранения микропрограмм. Ее отличает очень высокое быстродействие и небольшая емкость, определяющаяся количеством команд в системе команд центрального процессора.

•Регистровая память выполнена на триггерных элементах и входит в состав центрального процессора. Емкость ее невысока, скорость высокая, но меньше, чем у управляющей памяти. Основной характеристикой данного типа памяти является разрядность.

Архитектура набора команд служит границей между аппаратурой и программным обеспечением и представляет ту часть системы, которая видна программисту.

Двумя основными архитектурами набора команд, используемыми компьютерной промышленностью на современном этапе развития вычислительной техники являются архитектуры CISC и RISC. Известны также архитектуры MISC и VLIW

Лидером в разработке микропроцессоров с полным набором команд (CISC - Complete Instruction Set Computer) считается компания Intel со своей серией x86 и Pentium. Эта архитектура является практическим стандартом для рынка микрокомпьютеров.

Архитектура процессоров компании Intel основана на системе команд CISC (Complex Instruction Set Computer) – полной системе команд переменной длины. Команды процессора могут иметь длину от 8 до 108 бит, и процессор должен последовательно декодировать инструкцию после определения её границ. Первые процессоры для персональных компьютеров были скалярными устройствами ( то есть могли в каждый момент времени выполнять только одну команду), конвейерная обработка ( то есть одновременное выполнение нескольких команд на разных стадиях конвейера применялась лишь в больших ЭВМ).

Для CISC-процессоров характерно:

Ø сравнительно небольшое число регистров общего назначения;

Ø большое количество машинных команд, некоторые, из которых нагружены семантически аналогично операторам высокоуровневых языков программирования и выполняются за много тактов;

Ø большое количество методов адресации;

Ø большое количество форматов команд различной разрядности;

Ø преобладание двухадресного формата команд;

Ø наличие команд обработки типа регистр-память.

Позже появились процессоры, основанные на архитектуре RISC (Reduced Instruction Set Computer) – сокращённом наборе команд компьютера фиксированной длины, которая была оптимизирована для суперскалярных (с возможностью выполнения нескольких команд одновременно) конвейерных вычислений.

Зачатки этой архитектуры уходят своими корнями к компьютерам CDC6600, разработчики которых (Торнтон, Крэй и др.) осознали важность упрощения набора команд для построения быстрых вычислительных машин. Эту традицию упрощения архитектуры С. Крэй с успехом применил при создании широко известной серии суперкомпьютеров компании Cray Research.

Однако окончательно понятие RISC в современном его понимании сформировалось на базе трех исследовательских проектов компьютеров: процессора 801 компании IBM, процессора RISC университета Беркли и процессора MIPS Стенфордского университета.

Для RISC-процессоров характерно:

Ø архитектура, отделяющая команды обработки от команд работы с памятью;

Ø эффективная конвейерная обработка;

Ø система команд разрабатывалась таким образом, чтобы выполнение любой команды занимало небольшое количество машинных тактов (предпочтительно один машинный такт);

Ø логика выполнения команд, с целью повышения производительности, ориентировалась на аппаратную, а не на микропрограммную реализацию (чтобы упростить логику декодирования команд использовались команды фиксированной длины и фиксированного формата);

Ø наличие достаточно большого регистрового файла (в типовых RISC-процессорах реализуются 32 или большее число регистров по сравнению с 8 - 16 регистрами в CISC-архитектурах), что позволяет большему объему данных храниться в регистрах на процессорном кристалле большее время и упрощает работу компилятора по распределению регистров под переменные;

Ø для обработки, как правило, используются трехадресные команды, что помимо упрощения дешифрации дает возможность сохранять большее число переменных в регистрах без их последующей перезагрузки.

Ко времени завершения университетских проектов (1983-1984 гг.) обозначился также прорыв в технологии изготовления сверхбольших интегральных схем. Простота архитектуры и ее эффективность, подтвержденная этими проектами, вызвали большой интерес в компьютерной индустрии и с 1986 года началась, активная промышленная реализация архитектуры RISC. К настоящему времени эта архитектура прочно занимает лидирующие позиции на мировом компьютерном рынке рабочих станций и серверов.

Развитие архитектуры RISC в значительной степени определялось прогрессом в области создания оптимизирующих программаторов (компиляторов). Именно современная техника программирования позволяет эффективно использовать преимущества большего регистрового файла, конвейерной организации и большей скорости выполнения команд. Современные компиляторы используют также преимущества другой оптимизационной техники для повышения производительности, обычно применяемой в процессорах RISC: реализацию задержанных переходов и суперскалярной обработки, позволяющей в один и тот же момент времени выдавать на выполнение несколько команд. Архитектуры процессоров CISC и RISC развивались практически независимо, однако в отдельных модификациях процессоров AMD удалось совместить обе архитектуры. То есть микроядро процессора работает на основе инструкций RISC, а специальный блок интерпретирует команды CISC для обеспечения совместимости с программами для процессоров х86.

Minimum instruction set computer — вычисления с минимальным набором команд. Дальнейшее развитие идей команды Чака Мура, который полагает, что принцип простоты, изначальный для RISC-процессоров, слишком быстро отошёл на задний план. В пылу борьбы за максимальное быстродействие, RISC догнал и перегнал многие CISC процессоры по сложности. Архитектура MISC строится на стековой вычислительной модели с ограниченным числом команд (примерно 20-30 команд).

Very long instruction word — сверхдлинное командное слово. Архитектура процессоров с явно выраженным параллелизмом вычислений, заложенным в систему команд процессора. Являются основой для архитектуры EPIC. Ключевым отличием от суперскалярных CISC-процессоров является то, что для них загрузкой исполнительных устройств занимается часть процессора (планировщик), на что отводится достаточно малое время, в то время как загрузкой вычислительных устройств для VLIW-процессора занимается компилятор, на что отводится существенно больше времени (качество загрузки и, соответственно, производительность теоретически должны быть выше). Примером VLIW-процессора является Intel Itanium.

Центральный процессор в персональных компьютерах представляет собой микропроцессор, то есть, построен на одной микросхеме. В его состав входят:

•Центральное устройство управления - комплекс средств автоматического управления процессами передачи и обработки информации;

•Арифметико-логическое устройство - устройство, осуществляющее обработку информации и выработку признаков управляющих сигналов.

•Внутренняя память процессора:

-Постоянная память устройства управления.

Рис. 1 Обобщенная структурная схема ПК

Модули оперативной и постоянной памяти, связаны с микропроцессором напрямую. Остальные устройства (монитор, клавиатура, накопители на магнитных носителях и т.д.) связаны с микропроцессором через контроллеры ввода-вывода, которые, в свою очередь, связаны с микропроцессором через системную шину.

Микропроцессор является ядром ЭВМ. Он осуществляет обработку данных и функции управления системой. К функциям управления системой относятся:

•инициирование операций ввода-вывода;

•управление доступом к основной памяти;

•обработка системных событий – прерываний;

•организация многозадачных режимов работы.

Организация центрального процессора определяется архитектурой и принципами работы ЭВМ ( состав и форматы команд, организация памяти). Логическая структура включает ряд функциональных средств:

•средства обработки информации;

•средства управления системой и программами;

•управление интерфейсом и каналами.

Структурно эти средства разбиваются на центральное устройство управления, АЛУ, внутреннюю память и управляющие устройства, связанные с конкретными устройствами вычислительной машины.

Центральное устройство управления принимает и расшифровывает команды, формирует адреса команд и операндов, формирует последовательности управляющих сигналов и обеспечивает координацию работы всех функциональных узлов, посредством выработки синхронизирующих сигналов.

Внутренняя память входит в состав первого уровня и связана с АЛУ и другими блоками центрального процессора непосредственно и имеет скорость работы соизмеримую со скоростью работы блоков процессора.

•Управляющая память входит в состав центрального устройства управления и относится к классу постоянной памяти. Этот вид памяти используется для хранения микропрограмм. Ее отличает очень высокое быстродействие и небольшая емкость, определяющаяся количеством команд в системе команд центрального процессора.

•Регистровая память выполнена на триггерных элементах и входит в состав центрального процессора. Емкость ее невысока, скорость высокая, но меньше, чем у управляющей памяти. Основной характеристикой данного типа памяти является разрядность.

Архитектура набора команд (англ. instruction set architecture, ISA ) — часть архитектуры компьютера, определяющая программируемую часть ядра микропроцессора. На этом уровне определяются реализованные в микропроцессоре конкретного типа:

- архитектура памяти,

- взаимодействие с внешними устройствами ввода/ вывода, , , ,

- различные типы внутренних данных (например, с плавающей запятой, целочисленные типы и т. д.), и исключительных состояний.

Микроархитектура

Описывает модель, топологию и реализацию ISA на микросхеме микропроцессора. На этом уровне определяется:

- конструкция и взаимосвязь основных блоков ЦП,

- структура ядер, исполнительных устройств, АЛУ, а также их взаимодействия, ,

- организация конвейеров,

- организация кэш-памяти,

- взаимодействие с внешними устройствами.

В рамках одного семейства микропроцессоров микроархитектура со временем расширяется путём добавления новых усовершенствований и оптимизации существующих команд с целью повышения производительности, энергосбережения и функциональных возможностей микропроцессора. При этом сохраняется совместимость с предыдущей версией ISA.

Уровни, реализуемые в архитектуре, микроархитектуре и в семействе процессоров соответственно, а также их взаимосвязь описаны на рис. 1 в документе White Paper Inside Intel®Core™ Microarchitecture (англ.)

Архитектура системы команд — это совокупность формальных правил отображения программных приложений в машинных кодах модулем процессора или его эмулятором.

Введение

Система команд электронной вычислительной машины — это весь список команд, которые может исполнить данное вычислительное устройство. При этом, архитектурой системы команд является набор тех средств компьютерного оборудования, которые видимы и могут быть доступными программисту. Архитектуру системы команд следует воспринимать в качестве линии, согласующей нужды проектировщиков программ с возможностями разработчиков модулей вычислительной техники.

Архитектура системы команд

Архитектура системы команд является интерфейсом, связывающим программное и аппаратное обеспечение, как показано на рисунке ниже:

Рисунок 1. Архитектура системы команд. Автор24 — интернет-биржа студенческих работ

В результирующем итоге, целью программного и аппаратного обеспечения является обеспечение наиболее эффективной реализации вычислительного процесса. То есть минимизация времени вычислений, и, с этой точки зрения, очень важным является правильный выбор архитектуры системы команд.

Проще говоря, время исполнения программы, то есть время вычислений Tвыч, может быть определено через количество команд в программном приложении Nком, усреднённое число тактов процессора, отводимых на выполнение одной команды CPI, и размер тактового периода τпр:

Tвыч = Nком • CPI • τпр.

Все составляющие этой формулы имеют зависимость от определённых аспектов архитектуры системы команд, и, при этом, могут влиять на другие, как показано на рисунке ниже:

Готовые работы на аналогичную тему

Рисунок 2. Система команд. Автор24 — интернет-биржа студенческих работ

Следовательно, нужно очень внимательно подходить к подбору архитектуры системы команд.

- Какой тип данных будет использован в компьютере, и в каком формате?

- В каких ещё местах, кроме главной памяти, могут быть сохранены информационные данные?

- Как может быть осуществлён доступ к информации?

- Какой перечень операций может осуществляться над информационными данными?

- Какое количество операндов допускается в команде?

- Каким образом может быть определён адрес следующей команды?

- Как будет выполняться кодирование команд?

История прогресса в сфере вычислительного оборудования, будто зеркало, отображает все изменения, которые происходят в отношениях проектировщиков к перспективам различных архитектур системы команд.

Мотивация, которая предопределяет обращение к новому типу архитектуры системы команд, заключается в следующих аспектах:

- Набор операций, которые может выполнить вычислительная техника, и их уровень сложности.

- Место расположения операндов, влияющее на число и размер адресов, которые указываются в адресном участке команд работы с данными.

Сегодняшние технологии программирования базируются на языках высокого уровня, основной целью которых является облегчение процесса программирования. Однако ориентация на высокоуровневые языки порождает существенную проблему, а именно, сложные операторы, типичные для языков высокого уровня, имеют существенные отличия от обычных машинных процедур, выполняемых практически во всех компьютерах. Как следствие, выполнение программ на компьютере может оказаться низкоэффективным. Данная проблема именуется семантическим разрывом, и для её решения проектировщики вычислительного оборудования сегодня могут выбрать следующие подходы и соответствующие им типы архитектуры системы команд:

- Архитектура, имеющая полный командный набор, то есть CISC(Complex Instruction Set Computer).

- Архитектура, имеющая сокращённый командный набор, то есть RISC (Reduced Instruction Set Computer).

- Архитектура, имеющая командные слова сверхбольшого размера, то есть VLIW (Very Long Instruction Word).

Архитектура CISC способна преодолеть семантический разрыв путём расширения системы команд, а также дополнением её усложнёнными командами, которые по семантике аналогичны операторам высокоуровневых языков. Основы архитектуры CISC были заложены корпорацией IBM, начавшей использовать этот подход в семействе ЭВМ IBM 360, и продолжает его использовать в нынешних самых производительных универсальных компьютерах, класса мэйнфрейм. Такой же подход использовала и фирма Intel при разработке микропроцессоров серии x86. Архитектура системы команд CISC характеризуется следующими моментами:

- Присутствие в процессоре относительно малого количества регистров общего назначения.

- Значительное число машинных команд, некоторые из которых способны аппаратно реализовать сложные операторы высокоуровневых языков.

- Наличие разнообразных методов адресации операндов.

- Большое количество форматов команд, имеющих разную разрядность.

- Имеются команды, в которых обработка совмещена с обращением к памяти.

К типу архитектуры CISC относятся фактически все ЭВМ, которые выпускались до середины восьмидесятых годов прошлого века, и очень много ЭВМ, выпускающихся сегодня.

Однако, подробный анализ, проведённый специалистами, привёл к существенному пересмотру стандартных решений, что и привело к разработке архитектуры RISC. Её основной идеей было ограничение перечня команд вычислительного устройства наиболее часто применяемыми самыми простыми командами, работающими с данными, находящимися лишь в регистрах процессоров. Обращение к памяти возможно только при помощи специализированных команд чтения и записи. Сильно сократилось число форматов и методов задания адресов операндов. Данные меры дали возможность сильно упростить аппаратное обеспечение ЭВМ и повысить уровень быстродействия.

Основой архитектуры VLIW является также архитектура RISC. В VLIW набор несложных команд RISC соединён в единую сверхбольшую команду, и они исполняются параллельно. В остальном архитектура системы команд VLIW аналогична RISC, а отличие состоит только в добавочном уровне параллельных вычислений.

Архитектура набора команд (англ. instruction set architecture, ISA) — часть архитектуры компьютера, определяющая программируемую часть ядра микропроцессора. На этом уровне определяются реализованные в микропроцессоре конкретного типа:

- архитектура памяти,

- взаимодействие с внешними устройствами ввода/ вывода,

- режимы адресации,

- регистры,

- машинные команды,

- различные типы внутренних данных (например, с плавающей запятой, целочисленные типы и т. д.),

- обработчики прерываний и исключительных состояний.

Микроархитектура

Описывает модель, топологию и реализацию ISA на микросхеме микропроцессора. На этом уровне определяется:

- конструкция и взаимосвязь основных блоков ЦП,

- структура ядер, исполнительных устройств, АЛУ, а также их взаимодействия,

- блоков предсказания переходов,

- организация конвейеров,

- организация кэш-памяти,

- взаимодействие с внешними устройствами.

В рамках одного семейства микропроцессоров микроархитектура со временем расширяется путём добавления новых усовершенствований и оптимизации существующих команд с целью повышения производительности, энергосбережения и функциональных возможностей микропроцессора. При этом сохраняется совместимость с предыдущей версией ISA.

Уровни, реализуемые в архитектуре, микроархитектуре и в семействе процессоров соответственно, а также их взаимосвязь описаны на рис. 1 в документе White Paper Inside Intel®Core™ Microarchitecture (англ.)

Наборы команд на базе архитектуры Intel (IA)

Корпорация Intel разработала три типа ISA, которые ориентируются на различные секторы рынка. Для их именования часто используется акроним из выражения Intel Architecture, IA (например, IA-32, IA-64).

Читайте также: