Принцип работы d триггера кратко

Обновлено: 05.07.2024

Особенностью триггера является то, что при подаче на вход D низкого уровня (логического 0) и по спаду импульса на входе С, триггер сбрасывается в нулевое состояние. Если на входе D высокий уровень (логическая 1), то по спаду импульса на входе С триггер устанавливается в единицу.

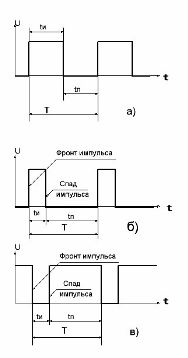

Что такое спад импульса? Объяснить это лучше наглядно, например, с помощью рисунка. Вот взгляните.

Напомним, что вход C является входом синхронизации или, по-другому, входом тактирования. Он нужен для того, чтобы упорядочить работу множества отдельных микросхем в одной общей схеме.

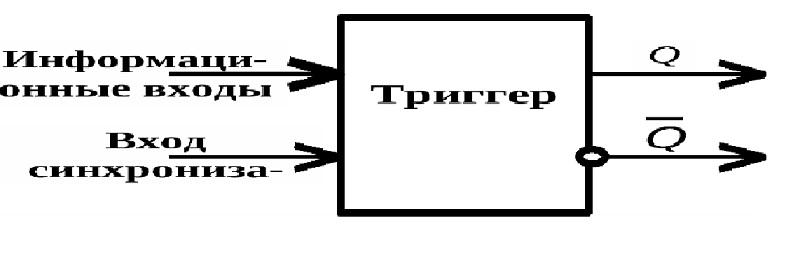

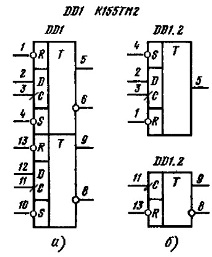

На принципиальных схемах D-триггер обозначается следующим образом.

Бывает, что изображение на схеме несколько отличается. Но, несмотря на это, на условном обозначении D-триггера всегда присутствует указание входа "D".

В cерии логических микросхем К561, выполненных по технологии КМОП, есть наборы D-триггеров. Например, микросхема К561ТМ2 содержит два D-триггера в одном корпусе. А в составе микросхемы К561ТМ3 уже четыре D-триггера. Для построения несложных счётчиков и делителей частоты эти микросхемы гораздо удобнее.

Вот так обозначается на схемах микросхема К561ТМ2 (К176ТМ2, К564ТМ2). Импортный аналог микросхемы К561ТМ2 - CD4013, HEF4013.

Как видим, в составе этой микросхемы два D-триггера. Для подключения питания к этой микросхеме используются вывод 14 (это плюс "+", VDD) и вывод 7 (это минус "-", GND).

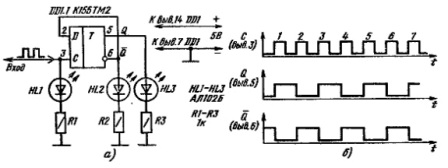

Для того чтобы получить из D-триггера делитель частоты на два достаточно соединить инверсный выход со входом D. То есть соединяются выводы 2 и 5 (12 и 9), а импульсы подаются на вход С.

В цифровых схемах d триггер выполняет функции единичного запоминающего устройства. Такие решения применяют для оперативного и длительного хранения информации. Их используют в блоках фильтрации сигналов. Представленные ниже сведения помогут ознакомиться не только с теорией, но и с методикой решения отдельных практических задач.

Что такое Д триггер

Триггерами называют устройства, способные длительное время поддерживать определенное состояние на выходе. Как правило, они контролируют соответствующие уровни напряжения. Изменения происходят при определенной комбинации входных сигналов.

Простейшие устройства этой категории создают по схеме RS. Они запоминают состояние сигнала, поданного на один из входов. Чтобы устранить процесс сбоев, который вызывают паразитные колебания при переходе сигнала из ноля в единицу и обратно, применяют синхронизацию. Этим дополнительным сигналом устанавливают точное время (интервал) для возможных изменений.

Устройство Д триггера

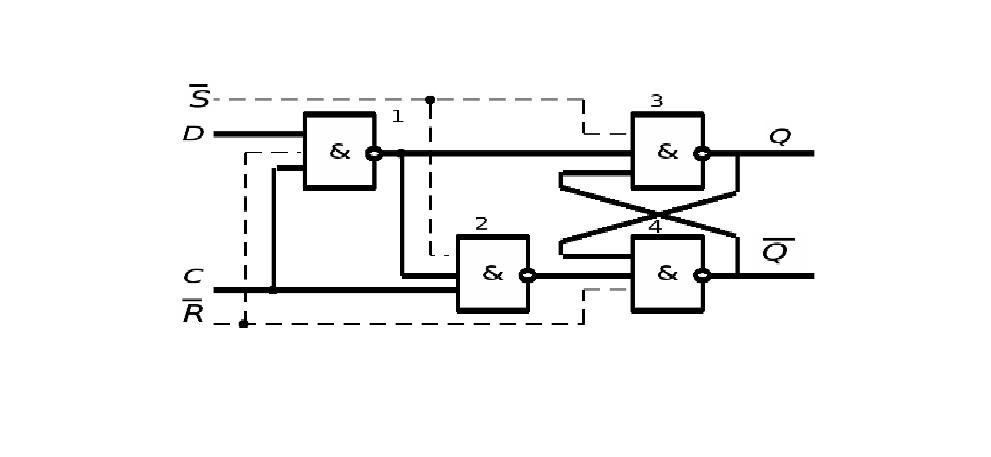

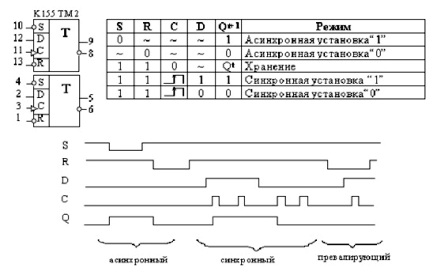

На рисунке, кроме основных, отмечены входы. Вне зависимости от сигналов синхронизации, с их помощью переводят изделие в нулевое или единичное состояние. Таким образом реализован принцип приоритетности, так как активация S и R блокирует входные вентили C.

Виды D триггера

Типовые решения с применением представленных логических элементов рассмотрены ниже. Допустимы другие комбинации для удвоения частоты и решения других задач.

D-триггер синхронный

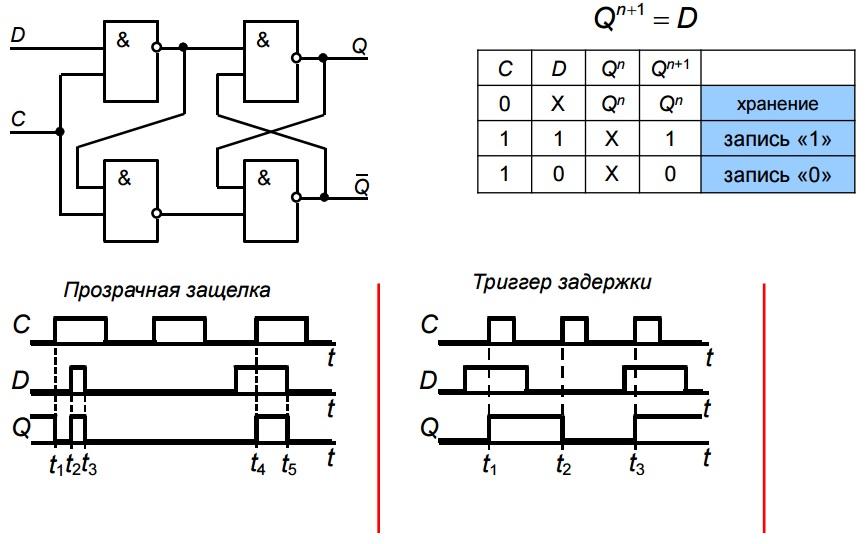

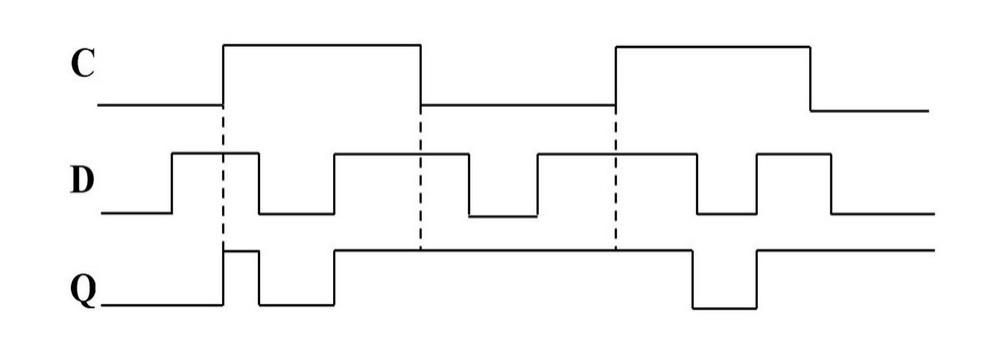

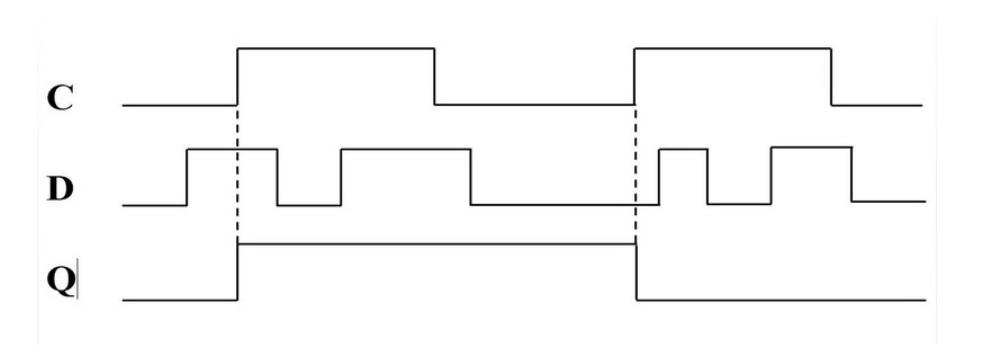

Рассмотрим на упрощенном примере основы функционирования. Для этого уберем сервисные входы. Диаграммы демонстрируют изменение сигналов при разных комбинациях управления. В таблице показаны состояния для записи единиц и нулей, а также в режиме хранения.

Если подать на С единицу (ноль), изменение на D сопровождается появлением аналогичного сигнала на выходе Q. Следует обратить внимание на временные задержки. Пока синхронизация отсутствует, изделие не срабатывает, вне зависимости от состояния информационного входа.

В соответствующих режимах:

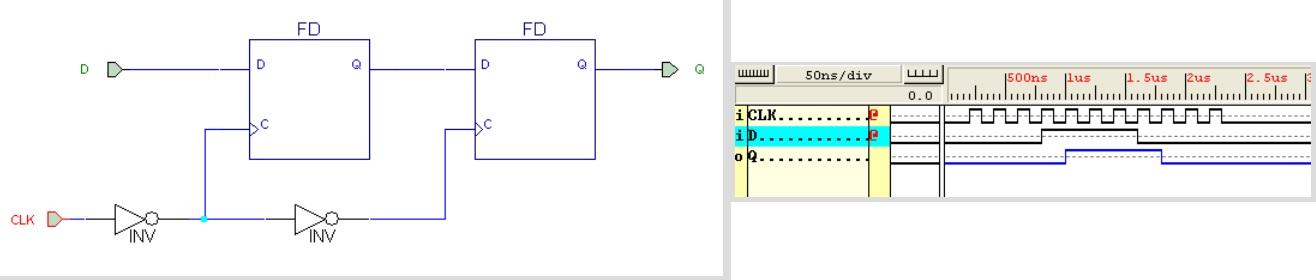

D-триггер двухступенчатый

В таких схемах объединяют последовательно два триггера. Первый – настраивают по увеличению входного сигнала. Второй – по спаду. Как видно на рисунке, состояние изменяется не одновременно с появлением новой информации, а с определенной временной задержкой, длительность которой равна одному полному рабочему циклу сигнала синхронизации.

Принцип работы

Во всех схемах имеет значение длительность рабочих реакций, которая определяет время записи (стирания). Определенное значение имеет помехоустойчивость. В следующих разделах рабочие процессы рассмотрены подробно.

Элементы с управлением по уровню

В этом варианте изменение состояния происходит только при высоком уровне синхронизирующего сигнала. При соответствующем положении устройство копирует изменения на входе с небольшой технологической задержкой. Если на С – ноль, реакция на выходе отсутствует.

Элементы с управлением по фронту

В соответствии с названием, здесь реализована схема управления по фронту (переднему и заднему). С помощью временной диаграммы можно рассмотреть рабочие циклы внимательно.

Допустим, что для управления выбран передний фронт. При С=0 состояние триггера не изменяется, вне зависимости от информационных сигналов, – одновременно с прохождением переднего фронта записывается аналогичное уровню D. В данном примере – единица. Следующие изменения происходят по такому же алгоритму.

Чтобы расширить базовую функциональность, устройство дополняют представленными выше сервисными входами (R и S). С их помощью состояние устанавливают произвольным образом (1 или 0) в любой нужный момент. Разумеется, для выполнения таких действий понадобятся дополнительные элементы управления.

К сведению. В этом варианте не имеет значения длительность управляющего сигнала. Для функционирования схемы его можно подать с применением инвертора в противофазе на два триггера Д типа, соединенные последовательно. Такое решение будет сопровождаться изменением состояния по заднему фронту (спаду).

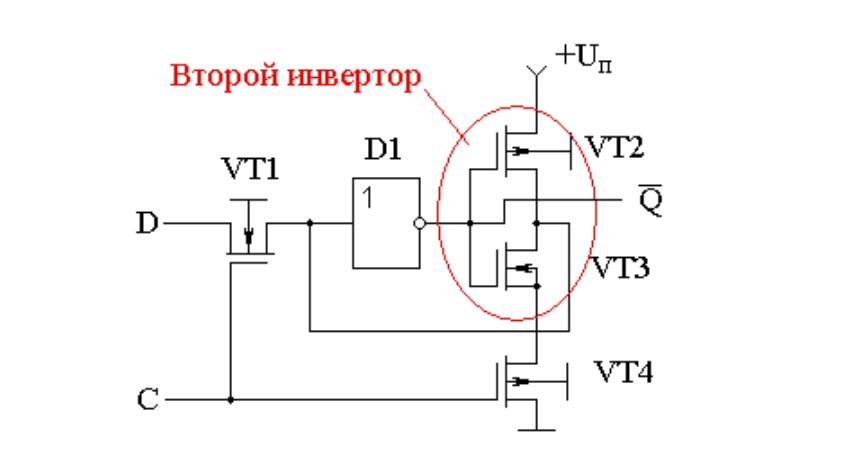

Схема реализации d-триггера

В отличие от схем RS, данные устройства управляются с применением одного информационного входа. Это удобно, так как в двоичной системе один бит принимает только два значения (ноль или единицу). Кроме экономии проводников, такое решение помогает изменять задержку с применением регулировок частоты синхронизирующего сигнала.

Вместо рассмотренных выше ТТЛ элементов для создания аналогичного устройства можно применить типовые транзисторы, созданные с применением КМОП технологии. На картинке изображен d триггер, принцип работы которого представлен ниже:

- при отсутствии сигнала на входе C транзистор VT1 находится в закрытом состоянии, не пропускает ток через полупроводниковый затвор;

- в этом состоянии не имеет значения уровень сигнала на D;

- если подать на С единицу, переход откроется;

- инвертор D1 обеспечит передачу на выход Q сигнала;

- два транзистора VT2 и VT3 образуют второй инвертор, который обеспечивает функционирование схемы в режиме типичного D триггера.

Таким образом, как и при работе с элементарными логическими компонентами, здесь данные состояния сохраняются только при нулевом уровне синхронизирующего сигнала. При увеличении его до уровня открытия полупроводникового перехода информация на входе и выходе будет повторяться с минимальной задержкой.

Для объективного анализа схемотехники надо изучить переходные процессы. Дело в том, что базовые для логических уравнений значения (ноль и единица) не всегда способны физически соответствовать идеальным значениям. Допустим, что управляющий сигнал поступает одновременно со сменой информационного. В этом случае триггер переходит в нестабильное состояние.

Ошибки проявляются в сбоях, когда последующие логические элементы ошибочно воспринимают амплитуду входных сигналов. Подобные ошибки могут блокировать полностью работу вычислительных устройств и другой техники.

Паразитные импульсные помехи образуют шумы в радиочастотном диапазоне. Состояние неопределенности увеличивает временные задержки при прохождении сигналов. Чтобы минимизировать вредное влияние и правильно делать конструкторские расчеты, производители триггеров указывают в сопроводительной документации минимальные допустимые параметры:

- setup time – промежуток перед синхронизирующим импульсом;

- hold time – длительность информационного сигнала.

Оценочный параметр MTBF показывает величину, обратно пропорциональную скорости отказов. Им определяют способность триггеров поддерживать стабильность рабочих процессов.

Условные обозначения Д триггеров на схеме

Стандарты:

- Т – триггер;

- D – информационный вход;

- C (треугольник) – синхронизация;

- S и R – входы для принудительного перевода состояния в ноль или единицу.

При работе с цифровыми схемами, кроме основных логических функций, надо учитывать базовые принципы радиотехники. Для поддержания хорошей работоспособности необходимо качественное электропитание. Особое внимание уделяют минимизации паразитных переходных процессов, защите от внешних неблагоприятных воздействий. Уменьшает количество сбоев эффективная защита от электромагнитных помех.

Триггеры различных видов зачастую входят в состав различной простой схемотехники, где не требуется применение микроконтроллеров. Они могут сохранять ранее установленные значения, изменять их, производить запись логического нуля или единицы. D-триггер является одним из наиболее распространённых видов таких устройств. Он позволяет осуществлять задержку сигналов, а также хранить информацию на протяжении нужного времени.

Какие бывают триггеры

Действие триггеров основывается на определенных принципах, зависящих от их типа. Эти логические устройства принимают входные сигналы, которые ими и управляют. Выходная информация зависит от сигнала, поступившего на вход и от полученного на предыдущем этапе. Следовательно, D-триггер реагирует и на существующие в данный момент значения, и на поступившие ранее.

Триггер может быть синхронный (тактируемый) и асинхронный (нетактируемый). В первом случае устройство учитывает тактовые сигналы. В любой вычислительной системе все действия выполняются с привязкой к сигналам такого типа с целью обеспечения согласованной работы.

Использование тактовых сигналов в синхронных триггерах означает, что срабатывание по заложенному принципу происходит не в любой момент времени, а лишь тогда, когда на управляющем входе наблюдается определенное событие. Например, если осуществляется переход тактового импульса от максимального значения до нулевого или наоборот. У асинхронных устройств такой привязки нет. В них переход из одного режима в другой выполняется перепадом напряжения.

Как работает D-триггер

D-триггер называют еще триггером задержки, поскольку он способен задерживать входной информационный сигнал на один такт. Время задержки определяется частотой импульсов синхронизации. Если информационный сигнал изменится, то выходной повторит его изменение, но лишь после того как тактовый сигнал примет значение, равное единице. Пока его значение будет оставаться нулевым, сигнал на выходе меняться не будет.

Работа любого D-триггера отражается в таблице истинности. Как видим, таблица истинности статического D-триггера достаточно простая. Она показывает, что нулевое значение управляющего сигнала обеспечивает хранение предыдущего значения сигнала на выходе на протяжении любого нужного периода времени. На практике речь идёт о том времени, когда к устройству подключено электропитание.

В представленной таблице истинности приведена информация о срабатывании D-триггера при значении C = 1. На практике применяется ещё один вариант, когда срабатывание происходит по переднему фронту импульса. То есть, выходное значение становится равным входному в тот момент, когда значение управляющего импульса меняется с нуля на 1. Логический элемент, в котором используется управление по уровню напряжения, называется статический D-триггер, а по фронту — динамический.

Когда применяется управление по фронту, срабатывание происходит при изменении управляющего значения. Может применяться два варианта — по переднему фронту или по заднему. При использовании первого варианта значение меняется с 0 на 1, второго — с 1 на 0.

Помимо таблицы, для описания работы логических элементов используются еще временные диаграммы.

Усложнённый вариант триггера

Иногда используется усложнённый вариант, когда добавляется ещё один вход. Обычно его обозначают буквой R. Если на него подается сигнал с нулевым значением, он не оказывает никакого влияния на работу элемента. В том случае, когда на вход R поступает сигнал с единичным значением, происходит сброс Q в 0. Этого же можно добиться на классическом D-триггере, если использовать C = 0 и D = 0.

Схемы реализации D-триггера

Роль каждого элемента будет проще понять, изучив принцип работы Д-триггера. Из схемы видно, если C = 0, то логическая операция И создаст нулевое значение независимо от вторых входных значений на DD1.1 и DD1.2. Операция отрицания сформирует единицу на выходе обоих этих элементов.

На входе третьего элемента будет два значения: единица и отрицание Q. Операция И на выходе сформирует отрицание Q. Отрицание приведёт к тому, что на выходе будет значение Q, совпадающее с тем, которое здесь было раньше.

На четвертый элемент поступят единица и Q. Результатом применения И будет Q. После применения отрицания на выходе этого элемента будет отрицание Q. Следовательно, и в этом случае значение не изменится.

Теперь нужно рассмотреть ситуацию, когда на управляющем входе единичное значение. Если D = 0, то после применения И будет получен ноль, а в результате отрицания выходным значением DD.1 станет единица, которая будет передана на вход DD1.2.

В DD1.2 на входе имеется две единицы, значит операция И сформирует 1, а отрицание даст 0. Следовательно, на DD1.4 на выходе будет единица, что соответствует нулевому значению Q. По такому же принципу рассчитываются остальные варианты.

Схему D-триггера можно получить из синхронного RS-триггера за счет введения дополнительного элемента И-НЕ1, соединяющего оба инверсных входа в один информационный. Это позволяет исключить состояние неопределенности для S и R.

Существуют еще комбинированные D-триггеры. Они имеют входы S и R, предназначенные для асинхронной установки логического 0 и 1. С помощью этих входов устройству можно придать первоначальное определенное состояние.

На схеме видно, что из 6 элементов И-НЕ построен D-триггер, его принцип работы следующий: при наличии 1 на входе R и нуля на C, D, S будут оставаться закрытыми элементы с первого по пятый. Шестой элемент при этом будет открытым, то есть, Q = 1, а /Q = 0. Первый элемент откроется, если с входа S будет снят нулевой сигнал. Состояние остальных элементов не изменится.

Когда на вход С поступит единичный сигнал, на всех входах третьего элемента появится такой же сигнал, в результате чего он откроется. Шестой элемент при этом закроется и /Q = 1. Затем на входы пятого элемента также поступят единичные сигналы, и он примет открытое состояние, а Q = 0. В результате после переключения триггера на выходе Q появится сигнал идентичный тому сигналу, который был на входе D до переключения, то есть, Qn+1 = Dn = 0. Если же с входа С снимается единичный сигнал, состояние триггера не меняется.

Достаточно просто схема D-триггера реализовывается на КМОП микросхемах. В подобных устройствах функции логических элементов И выполняют обычные транзисторные ключи.

После поступления синхросигнала высокого уровня на вход С транзистор №1 открывается, обеспечивая поступление сигнала с D на Q. При этом задействуется первый инвертор. В данной ситуации второй транзистор остается закрытым. Он отключает инвертор, построенный на транзисторах VT1 и VT3. Включается этот инвертор после поступления низкого потенциала на вход С.

D-триггеры входят в состав многих микросхем. Например, в микросхеме ТМ2 содержится два таких элемента, ТМ5, ТМ7, ТМ8 — четыре, ТМ9 — шесть.

Применение D-триггеров

Способность сохранять информацию позволяет применять D-триггеры для реализации устройств памяти. Эти работающие элементы способны сохранять нужный режим на выходе до тех пор, пока не будет подан управляющий сигнал для изменения. Триггер даёт возможность, как вносить двоичную информацию, так и хранить и считывать её.

Понимая, что такое Д-триггер, его можно применить для создания регистра-защёлки. Эти устройства важны в определённых ситуациях. Иногда сигнал длится на протяжении очень небольшого промежутка времени и микросхема может не успеть среагировать на него. В подобных случаях выгодно использовать ещё одну микросхему, на которой сохранятся необходимые значения на протяжении времени, достаточного для выполнения нужных действий.

Одно из основных назначений D-триггера — использование в счетном режиме. Чтобы заставить его работать в качестве счетчика импульсов, достаточно на вход D подать сигнал с его собственного инверторного выхода. В таком режиме по приходу каждого импульса на вход С триггер будет менять свое состояние на противоположное, как показано на временной диаграмме.

Делитель частоты — устройство, способное изменять частоту выходного сигнала относительно входного значения. Используя каскадное соединение нескольких элементов, можно построить делители частоты, обладающие различными коэффициентами деления. Два D-триггера, соединенных последовательно, обеспечивают получение выходного сигнала, частота которого в четыре раза меньше по сравнению с той, что была на входе. Три последовательно соединенных элемента будут делить ее на восемь, а четыре — на шестнадцать.

При создании цифровых схем, действие которых синхронизируется единым тактовым генератором, очень часть бывает необходимо добиться синхронизации действующей схемы и внешнего входного сигнала. То есть, асинхронный сигнал должен преобразоваться в синхронный для всей системы, в которую он поступает. Эту задачу можно решить путем установки D-триггера.

Триггер способен выполнять логическую функцию и при этом поддерживать обратную связь. Именно поэтому его используют при создании многих устройств, предназначенных для запоминания, хранения, передачи и преобразования информации. Найти эти элементы можно в самых разных приборах, включая и устройства цифровой микроэлектроники.

Триггер – элемент цифровой техники, бистабильное устройство, которое переключается в одно из состояний и может находиться в нем бесконечно долго даже при снятии внешних сигналов. Он строится из логических элементов первого уровня (И-НЕ, ИЛИ-НЕ и т.д.) и относится к логическим устройствам второго уровня.

На практике триггеры выпускаются в виде микросхем в отдельном корпусе или входят в качестве элементов в состав больших интегральных схем (БИС) или программируемых логических матриц (ПЛМ).

Классификация и типы синхронизации триггеров

Триггеры делятся на два больших класса:

Принципиальное различие между ними в том, что у первой категории устройств уровень выходного сигнала меняется одновременно с изменением сигнала на входе (входах). У синхронных триггеров изменение состояния происходит только при наличии сихронизирующего (тактового, стробирующего) сигнала на предусмотренном для этого входе. Для этого предусмотрен специальный вывод, обозначаемый буквой С (clock). По виду стробирования синхронные элементы делятся на два класса:

У первого типа уровень выхода меняется в зависимости от конфигурации входных сигналов в момент появления фронта (переднего края) или спада тактового импульса (зависит от конкретного вида триггера). Между появлением синхронизирующих фронтов (спадов) на входы можно подавать любые сигналы, состояние триггера не изменится. У второго варианта признаком тактирования является не изменение уровня, а наличие единицы или нуля на входе Clock. Также существуют сложные триггерные устройства, классифицируемые по:

- числу устойчивых состояний (3 и более, в отличие от 2 у основных элементов);

- числу уровней (также более 3);

- другим характеристикам.

Сложные элементы имеет ограниченное применение в специфических устройствах.

Типы триггеров и принцип их работы

Существует несколько основных типов триггеров. Перед тем, как разобраться в различиях, следует отметить общее свойство: при подаче питания выход любого устройства устанавливается в произвольное состояние. Если это критично для общей работы схемы, надо предусматривать цепи предустановки. В простейшем случае это RC-цепочка, которая формирует сигнал установки начального состояния.

RS-триггеры

Самый распространенный тип асинхронного бистабильного устройства – RS-триггер. Он относится к триггерам с раздельной установкой состояния 0 и 1. Для этого имеется два входа:

Имеется прямой выход Q, также может быть инверсный выход Q1. Логический уровень на нём всегда противоположен уровню на Q – это бывает удобно при разработке схем.

При подаче положительного уровня на вход S на выходе Q установится логическая единица (если есть инверсный выход, он перейдет на уровень 0). После этого на входе установки сигнал может меняться как угодно – на выходной уровень это не повлияет. До тех пор, пока единица не появится на входе R. Это установит триггер в состояние 0 (1 на инверсном выводе). Теперь изменение сигнала на входе сброса никак не повлияет на дальнейшее состояние элемента.

Важно! Вариант, когда на обоих входах присутствует логическая единица, является запретным. Триггер установится в произвольное состояние. При разработке схем такой ситуации надо избегать.

RS-триггер можно построить на основе широко распространенных двухвходовых элементов И-НЕ. Такой способ реализуем как на обычных микросхемах, так и внутри программируемых матриц.

Один или оба входа могут быть инверсными. Это означает, что по этим выводам триггер управляется появлением не высокого, а низкого уровня.

Если построить RS-триггер на двухвходовых элементах И-НЕ, то оба входа будут инверсными – управляться подачей логического нуля.

Существует стробируемый вариант RS-триггера. У него имеется дополнительный вход С. Переключение происходит при выполнении двух условий:

- присутствие высокого уровня на входе Set или Reset;

- наличие тактового сигнала.

Такой элемент применяют в случаях, когда переключение надо задержать, например, на время окончания переходных процессов.

D-триггеры

Пока на входе для синхронизации присутствует логическая единица, сигнал на выходе Q повторяет сигнал на входе данных (режим прозрачности). Как только уровень строба перейдет в состояние 0, на выходе Q уровень останется тем же, что был в момент перепада (защелкнется). Так можно зафиксировать входной уровень на входе в любой момент времени. Также существуют D-триггеры с тактированием по фронту. Они защёлкивают сигнал по положительному перепаду строба.

На практике в одной микросхеме могут объединять два типа бистабильных устройств. Например, D и RS-триггер. В этом случае входы Set/Reset являются приоритетными. Если на них присутствует логический ноль, то элемент ведёт себя как обычный D-триггер. При появлении хотя бы на одном входе высокого уровня, выход устанавливается в 0 или 1 независимо от сигналов на входах С и D.

T-триггеры

T-триггер относится к классу счётных бистабильных элементов. Логика его работы проста – он изменяет своё состояние каждый раз, когда на его вход приходит очередная логическая единица. Если на вход подать импульсный сигнал, выходная частота будет в два раза выше входной. На инверсном выходе сигнал будет противофазен прямому.

Так работает асинхронный Т-триггер. Также существует синхронный вариант. При подаче импульсного сигнала на тактирующий вход и при наличии логической единицы на выводе T, элемент ведёт себя так же, как и асинхронный – делит входную частоту пополам. Если на выводе Т логический ноль, то выход Q устанавливается в низкий уровень независимо от наличия стробов.

![Схема работы синхронного T-триггера.]()

JK-триггеры

Этот бистабильный элемент относится к категории универсальных. Он может управляться раздельно по входам. Логика работы JK-триггера похожа на работу RS-элемента. Для установки выхода в единицу используется вход J (Job). Появление высокого уровня на выводе K (Keep) сбрасывает выход в ноль. Принципиальным отличием от RS-триггера является то, что одновременное появление единиц на двух управляющих входах не является запретным. В этом случае выход элемента меняет свое состояние на противоположное.

Если выходы Job и Keep соединить, то JK-триггер превращается в асинхронный счётный Т-триггер. Когда на объединённый вход подаётся меандр, на выходе будет в два раза меньшая частота. Как и у RS-элемента, существует тактируемый вариант JK-триггера. На практике применяются, в основном, именно стробируемые элементы такого типа.

Практическое использование

Свойство триггеров сохранять записанную информацию даже при снятии внешних сигналов позволяет применять их в качестве ячеек памяти ёмкостью в 1 бит. Из единичных элементов можно построить матрицу для запоминания двоичных состояний – по такому принципу строятся статические оперативные запоминающие устройства (SRAM). Особенностью такой памяти является простая схемотехника, не требующая дополнительных контроллеров. Поэтому такие SRAM применяются в контроллерах и ПЛМ. Но невысокая плотность записи препятствует использованию таких матриц в ПК и других мощных вычислительных системах.

Выше упоминалось использование триггеров в качестве делителей частоты. Бистабильные элементы можно соединять в цепочки и получать различные коэффициенты деления. Та же цепочка может быть использована в качестве счетчика импульсов. Для этого надо считывать с промежуточных элементов состояние выходов в каждый момент времени – получится двоичный код, соответствующий количеству пришедших на вход первого элемента импульсов.

В зависимости от типа примененных триггеров, счетчики могут быть синхронными и асинхронными. По такому же принципу строятся преобразователи последовательного кода в параллельный, но здесь используются только стробируемые элементы. Также на триггерах строятся цифровые линии задержки и другие элементы двоичной техники.

RS-триггеры используются в качестве фиксаторов уровня (подавителей дребезга контактов). Если в качестве источников логического уровня применяются механические коммутаторы (кнопки, переключатели), то при нажатии эффект дребезга сформирует множество сигналов место одного. RS-триггер с этим успешно борется.

Область применения бистабильных устройств широка. Круг решаемых с их помощью задач во многом зависит от фантазии конструктора, особенно в сфере нетиповых решений.

Что такое компаратор напряжения и для чего он нужен

Режимы работы, описание характеристик и назначение выводов микросхемы NE555

Что такое операционный усилитель?

Что такое термистор, их разновидности, принцип работы и способы проверки на работоспособность

Логические микросхемы. Часть 8. D - триггер

В статье приводится описание D - триггера, его работа в различных режимах, простая и наглядная методика изучения принципа действия.

В предыдущей части статьи было начато изучение триггеров. Самым простым в этом семействе считается RS триггер, о котором и было рассказано в седьмой части статьи. Более широкое применение в устройствах электроники получили D и JK триггеры. По смыслу действия они, как и RS триггер, также являются устройствами с двумя устойчивыми состояниями на выходе, но имеют более сложную логику работы входных сигналов.

Следует отметить, что все сказанное будет справедливо не только для микросхем серии К155, а и для других серий логических микросхем, например, К561 и К176. И не только то, что касается триггеров, в точности также работают все микросхемы логики, отличие лишь в электрических параметрах сигналов – уровнях напряжения и рабочих частотах, мощности потребления и нагрузочной способности.

D триггер

В серии микросхем К155 имеется несколько модификаций D-триггеров, однако наиболее распространена микросхема К155ТМ2. В одном 14-выводном корпусе размещены два независимых D-триггера. Единственное, что их объединяет это общая цепь питания. Каждый триггер имеет четыре входных сигнала логического уровня и, соответственно, два выхода. Это прямой выход и инверсный, с которыми мы уже знакомы по рассказу об RS-триггере. Здесь они выполняют ту же самую функцию. На рисунке 1 представлен D-триггер.

Также имеются микросхемы, содержащие в одном корпусе по четыре D – триггера: это такие микросхемы как К155ТМ5 и К155ТМ7. Иногда в литературе их называют четырехразрядными регистрами.

Рисунок 1. Микросхема К155ТМ2.

Рассмотрим более подробно входные сигналы. Это будет сделано на примере триггера с выводами 1…6. Соответственно, все сказанное будет справедливо и в отношении другого триггера (с номерами выводов 8…13).

Сигналы R и S выполняют ту же функцию, что и аналогичные сигналы RS триггера: при подаче на вход S уровня логического нуля триггер установится в единичное состояние. Это означает, что на прямом выходе (вывод 5) появится логическая единица. Если же теперь подать логический нуль на R-вход, то триггер сбросится. Это значит, что на прямом выходе (вывод 5) появится уровень логического нуля, а на инверсном (вывод 6) будет присутствовать логическая единица.

Вообще, когда говорят о состоянии триггера, имеется в виду состояние его прямого выхода: если триггер установлен, то на его прямом выходе высокий уровень (логическая единица). Соответственно, подразумевается, что на инверсном выходе все с точностью до наоборот, поэтому инверсный выход часто при рассмотрении работы схемы просто не упоминают.

Логическую единицу на входы R и S можно подавать сколько угодно: состояние триггера не изменится. Это говорит о том, что для входов R и S рабочим является низкий уровень. Именно поэтому входы RS начинаются с маленького кружочка, который обозначает, что рабочий уровень сигнала низкий или, что то же самое, инверсный. Такой маленький кружочек у входных сигналов можно встретить не только у триггеров, а и в изображении некоторых других микросхем, например, дешифраторов или мультиплексоров, что также говорит о том, что рабочим уровнем данного сигнала является низкий уровень. Это общее правило для всех условных графических обозначений микросхем.

Кроме RS входов D-триггер имеет еще вход данных D, от английского Data (данные), и вход синхронизации C от английского же Clock (импульс, строб). Используя эти входы можно заставить триггер работать либо как элемент памяти, либо как счетный триггер. Для того, чтобы разобраться в работе D-триггера лучше собрать небольшую схему и провести несложные опыты.

Обратите внимание на изображение входа C: правый по рисунку конец этого вывода заканчивается небольшой наклонной чертой в направлении слева – вверх – направо. Эта черта говорит о том, что переключение триггера по входу C происходит в момент перехода входного сигнала из нуля в единицу. На рисунке 3 показана возможная форма импульсов на входе С.

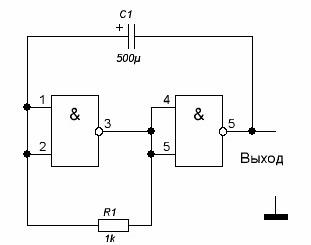

Для того, чтобы более подробно разобраться с работой D – триггера лучше всего собрать схему, как показано на рисунке 2.

Рисунок 2. Схема для изучения работы D – триггера.

Рисунок 3. Варианты импульсов на входе С.

Работа D триггера по RS входам

Сначала попробуем подать низкий уровень на вход S, просто замыкая вывод 4 на общий провод. Что при этом произойдет? На выходах триггера сигналы останутся в том же состоянии, что и были при включении. Почему? Все очень просто: триггер уже находится в единичном состоянии или установлен, и подача управляющего сигнала на вход S просто подтверждает это состояние триггера, изменение состояния не происходит. Такой режим работы для триггера нисколько не вреден и достаточно часто встречается в работе реальных схем.

Теперь с помощью той же проволочки подадим низкий уровень на вход R. Результат не заставит себя ожидать: триггер перейдет в состоянии низкого уровня, или как еще говорят, сбросится. Повторная и последующая подача низкого уровня на вход R также просто подтвердит состояние, на этот раз нулевое, в точности так же, как это было описано чуть выше, для входа S. Из этого состояния его может вывести либо подача низкого уровня на вход S, либо комбинация сигналов на входах C и D.

Следует отметить, что иногда D – триггер может применяться просто как RS – триггер, то есть входы C и D не используются. В этом случае для повышения помехоустойчивости их следует через резисторы сопротивлением 1 КОм подключить к шине +5 В, либо соединить с общим проводом.

Работа триггера по входам C и D

Предположим, что в данный момент триггер установлен, поэтому зажжен светодиод HL3. Что произойдет, если нажать на кнопку SB1? Ровным счетом ничего, состояние выходных сигналов триггера не изменится. Если теперь по входу R сбросить триггер, то будет светить светодиод HL2, а HL3 погаснет. Нажатие на кнопку SB1 и в этом случае состояния триггера не изменит. Это говорит о том, что на входе С нет тактирующих импульсов.

Теперь попробуем на вход C подать тактирующие импульсы. Проще всего это сделать, собрав генератор прямоугольных импульсов, уже знакомый нам по предыдущим частям статьи. Его схема приведена на рисунке 4.

Рисунок 4. Генератор тактовых импульсов.

Чтобы наблюдать за работой схемы визуально, частота генератора должна быть невелика, при указанных на схеме деталях составляет около 1 Гц, то есть 1 колебание (импульс) в секунду. Частоту генератора можно изменять подбором конденсатора С1. Состояние входа С индицирует светодиод HL1: светодиод зажжен – на входе С высокий уровень, если погашен, то уровень низкий. В момент зажигания светодиода HL1 на входе С происходит формирование положительного перепада напряжения (из низкого уровня в высокий). Именно этот переход заставляет срабатывать D – триггер по входу С, а не наличие на этом входе высокого или низкого уровня напряжения. Это следует запомнить, и следить за поведением триггера именно в момент формирования фронта импульса.

Если на вход С подключить генератор импульсов и включить питание, то первым же импульсом триггер установится в единицу, последующие импульсы состояния триггера не изменят. Все сказанное справедливо для случая, когда переключатель SB1 находится в положении, указанном на рисунке.

Теперь давайте переключим SB1 в нижнее по схеме положение, тем самым подав на вход D низкий уровень. Первый же импульс пришедший с генератора переведет триггер в состояние логического нуля или триггер будет сброшен. Об этом нам подскажет светящийся светодиод HL2. Последующие импульсы на входе С также не меняют состояния триггера.

На рисунке 2б показана временная диаграмма работы триггера по CD входам. Предполагается, что состояние входа D меняется как показано на рисунке, а на вход С поступают периодические тактирующие импульсы.

Первый импульс на входе С устанавливает триггер в единичное состояние (вывод 5), а второй импульс состояния триггера не меняет, поскольку на входе С до сих пор уровень остается высоким.

Состояние входа D между вторым и третьим тактирующими импульсами изменяется с высокого уровня на низкий, это видно на рисунке 2. Но переключение триггера в нулевое состояние происходит лишь по началу третьего тактирующего импульса. Четвертый и пятый импульсы на входе С состояния триггера не изменяют.

Следует обратить внимание на тот факт, что сигнал на входе D изменил свое значение с низкого уровня на высокий во время тактирующего импульса на входе С. Однако, изменение состояния триггера не произошло, так как положительный фронт тактирующего импульса был раньше, чем произошло изменение уровня на входе D.

Еще одна временная диаграмма приведена на рисунке 5.

Рисунок 5. Полная временная диаграмма работы D триггера.

На рисунке видно, что триггер может работать в трех режимах, два из которых уже были рассмотрены выше. На рисунке это асинхронный и синхронный режимы. Наибольший интерес на временной диаграмме представляет превалирующий режим: тут видно, что во время низкого уровня на входе R изменения состояния триггера по входам С и D не происходит, что говорит о том, что входы RS являются приоритетными. Также на рисунке 5 приведена таблица истинности для D – триггера.

Из всего сказанного можно сделать следующие выводы: каждый положительный перепад импульса на входе С устанавливает триггер в состояние, которое в этот момент было на входе D, или просто переносит его состояние на прямой выход триггера Q. Отрицательный перепад на импульса на входе С никакого влияния на состояние триггера не оказывает.

На рисунке 3 показаны возможные формы импульсов на С входе: это меандр (3а), короткие импульсы высокого уровня, или положительные (3б), короткие импульсы низкого уровня (отрицательные) (3в). В любом случае срабатывание триггера происходит по положительному перепаду.

В одних случаях это будет фронт импульса, а в других его спад. Это обстоятельство следует учитывать при разработке и анализе схем на D – триггерах. Работа D – триггера в счетном режиме Одним из основных назначений D – триггера является его использование в счетном режиме. Для того, чтобы заставить работать его в качестве счетчика импульсов, достаточно на вход D подать сигнал с его собственного инверсного выхода. Такое соединение показано на рисунке 6.

Рисунок 6. Работа D – триггера в счетном режиме.

В таком режиме по приходу каждого импульса на вход С, триггер будет менять свое состояние на противоположное, как показано на временной диаграмме. И объяснение этому самое простое и логичное: состояние на входе D всегда противоположно, инверсно, по отношению к прямому выходу. Поэтому, в свете предыдущего рассмотрения работы триггера, на прямой выход переносится его инверсное состояние. Один триггер, хоть и в счетном режиме, много не насчитает, всего лишь до двух: 0..1 и снова 0..1, и так далее.

Чтобы получить счетчик, способный считать по – настоящему потребуется соединить последовательно несколько триггеров, работающих в счетном режиме. Об этом будет рассказано несколько позже в отдельной статье. Кроме этого, следует обратить внимание на тот факт, что импульсы на выходе триггера имеют частоту ровно в два раза меньшую, чем входные на входе С. Это свойство используется в тех случаях, когда необходимо поделить частоту сигнала в число раз кратное двум: 2, 4, 8, 16, 32 и так далее.

Форма импульсов после деления триггером всегда есть меандр, даже в случае очень коротких входных импульсов на входе С. На этом рассказ о возможностях применения D триггера можно закончить. В следующей части статьи будет рассказано о применении триггеров типа JK

Читайте также:

- Влияние средств массовой информации на становление самооценки детей младшего школьного возраста

- Аттестационный лист для воспитателей доу образец

- Смотреть мультфильм школа принцесс онлайн бесплатно в хорошем качестве

- Перечень комнатных растений по возрастным группам в доу по фгос

- Организационная и технологическая структура строительно монтажных работ ответ кратко