Арифметико логическое устройство доклад

Обновлено: 04.07.2024

Арифметико-логическое устройство как одна из основных функциональных частей процессора, осуществляющая непосредственное преобразование информации. Последовательные, параллельные, функциональные арифметико-логические устройства, методы их повышения.

| Рубрика | Коммуникации, связь, цифровые приборы и радиоэлектроника |

| Вид | реферат |

| Язык | русский |

| Дата добавления | 22.12.2010 |

| Размер файла | 68,1 K |

Студенты, аспиранты, молодые ученые, использующие базу знаний в своей учебе и работе, будут вам очень благодарны.

АЛУ - одна из основных функциональных частей процессора, осуществляющая непосредственное преобразование информации.

Все операции, выполняемые в АЛУ, можно разделить на следующие группы:

Ё операции двоичной арифметики для чисел с фиксированной точкой;

Ё операции двоичной (шестнадцатеричной) арифметики для чисел с плавающей точкой;

Ё операции десятичной арифметики над числами, представленными в двоично-десятичном коде;

Ё операции адресной арифметики (при модификации адресов команд);

Ё операции специальной арифметики (нормализация, сдвиг);

Ё логические операции;

Ё операции над алфавитно-цифровыми полями.

Для выполнения перечисленных операций в АЛУ включают следующие функциональные узлы:

Ё сумматор (для выполнения суммирования и других действий над кодами операндов);

Ё регистры (для хранения кодов операндов на время выполнения действия над ними);

Ё сдвигатели (для сдвига кода на один или несколько разрядов вправо или влево);

Ё преобразователи (для преобразования прямого кода числа в обратный или дополнительный);

Ё комбинационные схемы (для реализации логических операций, мультиплексирования данных, управляемой передачи информации, формирования признаков результата).

Регистры и в некоторых случаях сумматоры имеют цепи управления приемом, выдачей и сбросом кодов операндов.

Логические операции, операции сдвига и преобразования кодов могут выполняться не только специальными устройствами, но и с помощью дополнительных связей регистров и сумматора.

2. Структура алу

Обобщенная структурная схема АЛУ (рис. 1) включает:

- блок регистров для приема и размещения операндов и результатов;

- операционный блок, в котором осуществляется преобразование операндов в соответствии с реализуемыми алгоритмами;

- схемы контроля, обеспечивающие непрерывный оперативный контроль и диагностирование ошибок;

- блок управления (БУ), в котором после приема кода операции (КОП) из центрального устройства управления формируются управляющие сигналы (УС), координирующие взаимодействие всех узлов АЛУ между собой и с другими блоками процессора.

Блок регистров связан с РОН центрального процессора и кэш-памятью данных.

Иногда АЛУ не содержит своего БР, в этом случае операционный блок непосредственно работает с регистрами общего назначения процессора. Для оперативного управления выполнением операции в ОБ на разных этапах анализируется преобразуемая информация и формируются сигналы признаков (флаги), которые используются в БУ для выработки и посылки в процессор сигнала признака результата (ПРез).

Для оценки АЛУ используются следующие характеристики: множество выполняемых операций, разрядность, время выполнения операций, надежностные и энергетические характеристики.

Рис. 1. Обобщенная структурная схема АЛУ.

3. Сумматоры АЛУ

Ё по типу использования для суммирования базовых элементов (комбинационные и накапливающие);

Ё по способу осуществления операции суммирования (последовательные и параллельные).

Сумматоры последовательного действия выполняются, как правило, на комбинационных элементах; на сегодняшний день устройства такого типа почти не применяются.

В АЛУ современных ЭВМ средней и высокой производительности применяются сумматоры параллельного действия, выполняемые на накапливающих или комбинационных элементах.

Рис. 2. Сумматор параллельного действия (на накапливающих элементах).

В качестве накапливающих элементов могут служить обычные T-триггеры.

Перед суммированием триггеры сумматора устанавливаются в нулевое состояние сигналом сброс. Затем на счетные входы триггеров подается первое слагаемое и запоминается. В следующем такте на входы триггеров подается второе слагаемое.

Триггеры тех разрядов, в которых второе слагаемое равно 1, меняют свое состояние на противоположное. В тех разрядах, в которых триггеры перешли из единичного состояния в нулевое, возникают сигналы переносов, последовательно передаваемые в старшие разряды сумматора. Арифметические операции сумматора выполняются с учетом знаков операндов.

4. Классификация АЛУ

Ё для чисел с фиксированной точкой;

Ё для чисел с плавающей точкой;

Ё для десятичных чисел.

По способу действия над операндами:

Ё последовательные;

В параллельных АЛУ операнды представляются параллельным кодом и операции совершаются параллельно во времени над всеми разрядами операндов.

Ё параллельные.

В последовательных АЛУ операнды представляются в последовательном коде, а операции производятся последовательно во времени над их отдельными разрядами.

Такие АЛУ, как правило, используют конвейерный метод обработки, при котором совмещаются во времени фазы выполнения операции для различных разрядов операндов.

По выполняемым функциям АЛУ подразделяются на:

Ё многофункциональные;

В многофункциональных АЛУ все возможные операции для всех форм представления чисел выполняются одними и теми же схемами, которые коммутируются нужным образом в зависимости от требуемого режима работы.

Ё функциональные (блочные).

В блочном АЛУ операции над числами с фиксированной и плавающей точкой, десятичными и алфавитно-цифровыми полями, операции умножения выполняются в отдельных блоках.

Такой подход позволяет увеличить скорость работы АЛУ за счет использования быстродействующих блоков, а также за счет организации параллельной работы этих блоков. Однако в этом случае значительно увеличиваются затраты на оборудование.

По структурной организации АЛУ подразделяются на устройства, имеющие:

Ё регистровую структуру с непосредственными связями и закрепленной логикой;

Ё магистральную структуру с сосредоточенной памятью и логикой.

В АЛУ с регистровой структурой за каждым из регистров закреплена своя логическая схема, используемая для выполнения микрооперации (см. рис. 3).

Пример:

С регистром Рг1 непосредственно связан преобразователь кода ПК1. С регистром Рг3 объединен КСМ по схеме накапливания сумматора, а с КСМ, в свою очередь, связаны ПК2 и комбинационная схема КС для мультиплексирования входных данных.

На регистре Рг3 выполняются микрооперации сдвига вправо или влево и сброс. Регистр Рг4 выполняет микрооперации сдвига и непосредственно связан с ПК3. Таким образом, в АЛУ с такой структурой функции хранения и преобразования информации выполняются одним и тем же операционным блоком.

Рис. 3. Регистровая структура с закрепленной логикой

В АЛУ с магистральной структурой регистры выделены в отдельный блок, а схемы для преобразования информации выделены также в отдельный операционный блок (ОБ), который связан с блоками регистров по входам и выходам (см. рис. 4).

Блок регистров (БР) осуществляет функции приема, хранения и выдачи операндов и результатов, а ОБ выполняет весь набор микроопераций над словами, хранимыми в блоке регистров.

В АЛУ с такой структурой блок регистров может быть реализован или как СОЗУ, или как совокупность отдельных регистров с индивидуальными схемами управления. Структура же ОБ имеет следующие модификации:

Ё последовательное соединение операционных узлов;

Ё параллельное соединение операционных узлов.

Пример АЛУ с магистральной структурой с последовательным соединением узлов ОБ.

В этом АЛУ преобразователь кода ПК, комбинационный сумматор КСМ и сдвигатель СДВ соединены последовательно, причем ПК и КСМ по входам связаны с выходными шинами блока регистров, а выход СДВ - с входной шиной блока регистров.

Такая организация операционного блока дает возможность выполнять с высокой скоростью последовательности микроопераций, обеспечивающие выполнение одного слова.

Рис. 4. Магистральная структура с последовательным соединением операционных узлов

В случае же параллельного соединения операционных блоков АЛУ все операционные блоки: СМ, СДВ, КС, ПК параллельно соединяются с входными и выходными шинами блока регистров, что позволяет выполнять несколько микроопераций параллельно. Выглядит это так, как показано на рис. 5.

Рис. 5. Магистральная структура с параллельным соединением операционных узлов

устройство информация арифметический логический

Одним из таких методов является реализация принципа локального параллелизма. Суть этого принципа - в распараллеливании во времени алгоритма выполняемой отдельно команды на ряд независимых этапов и их реализации на различных операционных блоках АЛУ.

* Данная работа не является научным трудом, не является выпускной квалификационной работой и представляет собой результат обработки, структурирования и форматирования собранной информации, предназначенной для использования в качестве источника материала при самостоятельной подготовки учебных работ.

ИЗУЧЕНИЕ ПРИНЦИПОВ ОРГАНИЗАЦИИ АРИФМЕТИКО-ЛОГИЧЕСКИХ УСТРОЙСТВ.

СТРУКТУРА АЛУ ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ЧИСЕЛ С ФИКСИРОВАННОЙ ЗАПЯТОЙ

Цель работы: Изучение принципов построения и функционирования АЛУ для сложения и вычитания чисел с фиксированной запятой.

Введение: Обычно в АЛУ операции алгебраического сложения сводятся к арифметическому сложению кодов чисел путем применения дополнительного или обратного кодов для представления отрицательных чисел.

Алгоритм выполнения в АЛУ арифметических операций зависит от того, в каком виде хранятся в памяти ЭВМ отрицательные числа, в прямом или дополнительном коде. В последнем случае сокращается время выполнения операции за счет исключения операции преобразования получаемого в АЛУ дополнительного кода отрицательного результата в прямой код.

Работа АЛУ: При выполнении операции сложения положительные слагаемые представляются в прямом коде, а отрицательные - в дополнительном. Производится сложение двоичных кодов, включая разряды знаков. Если при этом возникает перенос из знакового разряда суммы при отсутствии переноса в этот разряд или перенос в знаковый разряд при отсутствии переноса из разряда знака, то имеется переполнение разрядной сетки соответственно при отрицательной и положительной суммах. Если нет переносов из знакового разряда и в знаковый разряд суммы или есть оба эти переноса, то переполнения нет и при нуле в знаковом разряде сумма положительна и представлена в прямом коде, а при 1 в знаковом разряде сумма отрицательна и представлена в дополнительном коде.

Упрощенная структурная схема АЛУ для операций сложения и вычитания n-разрядных (n-й разряд знаковый) двоичных чисел с фиксированной запятой приведена на рис.1. Предполагается, что отрицательные числа хранятся в памяти в дополнительном коде.

В состав АЛУ входят n-разрядный параллельный комбинационный сумматор См, регистр сумматора PrCм, входные регистры сумматора PrB и PrА, входной регистр АЛУ Pr1.

Из оперативной памяти по входной информационной шине Шивк в АЛУ поступают операнды: положительные числа в прямом коде, а отрицательные в дополнительном. Операнды размещаются в PrB (первое слагаемое или уменьшаемое) и Pr1 (второе слагаемое или вычитаемое); Pr1 связан с PrA цепями прямой и инверсной передачи кода. Результат операции выдается из АЛУ в оперативную память по выходной информационной шине ШИвых. Запись информации в регистры АЛУ осуществляется под управлением сигналов ПрРг1 и ПрРгВ. Слово из Рг1 в РгА передается в прямом коде под действием управляющего сигнала ПрРгАП, в инверсном коде ПрРгАИ. Сигнал ПрРгСм управляет записью результата в регистр сумматора РгСМ, а сигнал ПрИШвых передачей содержимого РгСМ в информационную шину.

Код признака результата формируется комбинационной схемой Пр, на выходы которой поступают выходные сигналы всех разрядов сумматора СМ, а также сигналы переноса из знакового разряда ПнСМ[0] и из старшего цифрового разряда ПнСМ[1].

Признак переполнения (ПР=11) формируется, если выполняется условие

Признак нулевого значения результата Пр=00 формируется если

Признак положительного результата Пр=10 формируется при условии

При выполнении алгебраического сложения поступившие в АЛУ коды операндов находятся в выходных регистрах PrB и PrА сумматора. Код суммы формируется на выходе схемы См и фиксируется в регистре PrCм.

Операция алгебраического вычитания

Z=X-Y=X+(-Y)

может быть сведена к изменению знака вычитаемого Y и операции алгебраического сложения. Изменению знака соответствует следующая процедура: принятый в Pr1 код числа знака передается инверсно в PrА и при сложении осуществляется подсуммирование 1 в младший разряд сумматора.

Выполнение лабораторной работы:

1) 2 + 3 00011 + 00010 = 00101 = 5

2) 9 + 8 01000 + 01001 = 10001 = -1

Пр = 11 -> переполнение

3) –2 + 3 00011 + 10010 = 00011 + 11101 = 00000 + 00001 = 00001 = 1 Пр 10 -> 1 > 0

4) –3 + 2 00010 + 11000 (О.К.) = 11110 + 00001 = 10001 (ПК) = -1

Пр = 01 -> -1 -5 переполнение

Вывод: проведя данную лабораторную работу, я изучил принципы построения и функционирования АЛУ для сложения и вычитания чисел с фиксированной запятой.

Арифметико-логическое устройство (АЛУ) - центральная часть процессора, выполняющая арифметические и логические операции.

АЛУ реализует важную часть процесса обработки данных. Она заключается в выполнении набора простых операций. Операции АЛУ подразделяются на три основные категории: арифметические, логические и операции над битами. Арифметической операцией называют процедуру обработки данных, аргументы и результат которой являются числами (сложение, вычитание, умножение, деление. ). Логической операцией именуют процедуру, осуществляющую построение сложного высказывания (операции И, ИЛИ, НЕ. ). Операции над битами обычно подразумевают сдвиги.

Содержание

История создания

Разработчик компьютера ENIAC, Джон фон Нейман, был первым создателем АЛУ. В 1945 году он опубликовал первые научные работы по новому компьютеру, названному EDVAC (Electronic Discrete Variable Computer). Годом позже он работал со своими коллегами над разработкой компьютера для Принстонского института новейших исследований (IAS). Архитектура этого компьютера позже стала прототипом архитектур большинства последующих компьютеров. В своих работах фон Нейман указывал устройства, которые, как он считал, должны присутствовать в компьютерах. Среди этих устройств присутствовало и АЛУ. Фон Нейман отмечал, что АЛУ необходимо для компьютера, поскольку оно гарантирует, что компьютер будет способен выполнять базовые математические операции включая сложение, вычитание, умножение и деление

Структура АЛУ

АЛУ состоит из регистров, сумматора с соответствующими логическими схемами и элемента управления выполняемым процессом. Устройство работает в соответствии с сообщаемыми ему именами (кодами) операций, которые при пересылке данных нужно выполнить над переменными, помещаемыми в регистры.

Арифметико-логическое устройство функционально можно разделить на две части :

- микропрограммное устройство (устройство управления), задающее последовательность микрокоманд (команд);

- операционное устройство (АЛУ), в котором реализуется заданная последовательность микрокоманд (команд).

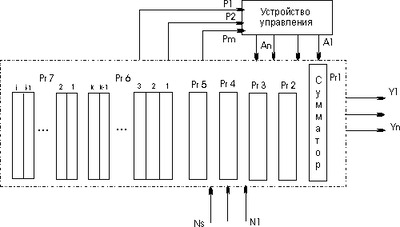

Рисунок 1 - Структурная схема арифметико-логического устройства

Структурная схема АЛУ и его связь с другими блоками машины показаны на рисунке 1. В состав АЛУ входят регистры Рг1 - Рг7, в которых обрабатывается информация , поступающая из оперативной или пассивной памяти N1, N2, . NS; логические схемы, реализующие обработку слов по микрокомандам, поступающим из устройства управления.

Закон переработки информации задает микропрограмма , которая записывается в виде последовательности микрокоманд A1,A2, . Аn-1,An. При этом различают два вида микрокоманд: внешние, то есть такие микрокоманды, которые поступают в АЛУ от внешних источников и вызывают в нем те или иные преобразования информации (на рис. 1 микрокоманды A1,A2. Аn), и внутренние, которые генерируются в АЛУ и воздействуют на микропрограммное устройство, изменяя естественный порядок следования микрокоманд. Например, АЛУ может генерировать признаки в зависимости от результата вычислений: признак переполнения, признак отрицательного числа, признак равенства 0 всех разрядов числа др. На рис. 1 эти микрокоманды обозначены р1, p2. рm.

Результаты вычислений из АЛУ передаются по кодовым шинам записи у1, у2, . уs, в ОЗУ. Функции регистров, входящих в АЛУ:

- Рг1 - сумматор (или сумматоры) - основной регистр АЛУ, в котором образуется результат вычислений;

- Рг2, РгЗ - регистры слагаемых, сомножителей, делимого или делителя (в зависимости от выполняемой операции);

- Рг4 - адресный регистр (или адресные регистры), предназначен для запоминания (иногда и формирования) адреса операндов и результата;

- Ргб - k индексных регистров, содержимое которых используется для формирования адресов;

- Рг7 - i вспомогательных регистров, которые по желанию программиста могут быть аккумуляторами, индексными регистрами или использоваться для запоминания промежуточных результатов.

Часть операционных регистров является программно-доступной, то есть они могут быть адресованы в команде для выполнения операций с их содержимым. К ним относятся : сумматор, индексные регистры, некоторые вспомогательные регистры.

Остальные регистры программно-недоступные, так как они не могут быть адресованы в программе. Операционные устройства можно классифицировать по виду обрабатываемой информации, по способу обработки информации и логической структуре.

АЛУ может оперировать четырьмя типами информационных объектов: булевскими (1 бит), цифровыми (4 бита), байтными (8 бит) и адресными (16 бит). В АЛУ выполняется 51 различная операция пересылки или преобразования этих данных. Так как используется 11 режимов адресации (7 для данных и 4 для адресов), то путем комбинирования "операция/ режим адресации" базовое число команд 111 расширяется до 255 из 256 возможных при однобайтном коде операции.

Классификация АЛУ

- По способу действия над операндами АЛУ делятся на последовательные и параллельные. В последовательных АЛУ операнды представляются в последовательном коде, а операции производятся последовательно во времени над их отдельными разрядами. В параллельных АЛУ операнды представляются параллельным кодом и операции совершаются параллельно во времени над всеми разрядами операндов.

- По способу представления чисел различают АЛУ:

- для чисел с фиксированной точкой;

- для чисел с плавающей точкой;

- для десятичных чисел.

- По характеру использования элементов и узлов АЛУ делятся на блочные и многофункциональные. В блочном АЛУ операции над числами с фиксированной и плавающей точкой, десятичными числами и алфавитно-цифровыми полями выполняются в отдельных блоках, при этом повышается скорость работы, так как блоки могут параллельно выполнять соответствующие операции, но значительно возрастают затраты оборудования. В многофункциональных АЛУ операции для всех форм представления чисел выполняются одними и теми же схемами, которые коммутируются нужным образом в зависимости от требуемого режима работы.

- По своим функциям АЛУ является операционным блоком, выполняющим микрооперации, обеспечивающие приём из других устройств (например, памяти) операндов, их преобразование и выдачу результатов преобразования в другие устройства. Арифметическо-логическое устройство управляется управляющим блоком, генерирующим управляющие сигналы, инициирующие выполнение в АЛУ определённых микроопераций. Генерируемая управляющим блоком последовательность сигналов определяется кодом операции команды и оповещающими сигналами.

Операции в АЛУ

Выполняемые в АЛУ операции можно разделить на следующие группы:

- операции двоичной арифметики для чисел с фиксированной точкой;

- операции двоичной (или шестнадцатеричной) арифметики для чисел с плавающей точкой;

- операции десятичной арифметики;

- операции индексной арифметики (при модификации адресов команд);

- операции специальной арифметики;

- операции над логическими кодами (логические операции);

- операции над алфавитно-цифровыми полями.

АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО: НАЗНАЧЕНИЕ, КЛАССИФИКАЦИЯ, СТРУКТУРА, ФУНКЦИОНИРОВАНИЕ

Текст работы размещён без изображений и формул.

Полная версия работы доступна во вкладке "Файлы работы" в формате PDF

Арифметико-логическое устройство (АЛУ) предназначено для выполнения арифметических и логических преобразований над числами и словами.

В АЛУ кроме классических арифметических операций, логического сложения и логического умножения двух слов выполняются сдвиги слов, преобразования кодов и некоторые другие операции.

Современные АЛУ выполняют:

функции двоичной арифметики для данных в формате с фиксированной точкой;

функции двоичной арифметики для данных в формате с плавающей точкой;

функции арифметики двоично-десятичного представления данных;

логические операций (в том числе сдвиги арифметические и логические);

операции пересылки данных;

работу с символьными данными;

работу с графическими данными.

Основные характеристики АЛУ можно разделить на количественные и качественные.

Количественные характеристики определяют скорость выполнения операций, время выполнения одной операции, точность представления данных, количество выполняемых операций.

Среднюю скорость выполнения операций Vср. в АЛУ можно определить как отношение N(T)- количества операций, выполненных за отрезок времени Т к данному отрезку времени:

Среднее время, которое АЛУ тратит на выполнение операции равно: Tср = 1/Vср (2)

Точность представления данных в АЛУ зависит от разрядной сетки АЛУ и выбранного формата данных.

К качественным характеристикам АЛУ относятся:

структурные особенности АЛУ;

форматы представления данных (с фиксированной или плавающей точкой);

способы кодирования данных.

АЛУ можно классифицировать по ряду признаков, приведенных ниже.

1. Классификация по способу представления данных:

с фиксированной запятой;

с плавающей запятой.

2. Классификация по способу действия над операндами:

·последовательные АЛУ, где каждая операция выполняется последовательно над каждым разрядом;

·параллельные АЛУ, операция выполняется над всеми разрядами данных одновременно;

·последовательно - параллельные АЛУ, где слово данных делится на слоги, обработка данных ведется параллельно над разрядами слога и последовательно над слогами.

3. Классификация по использованию систем счисления:

4. Классификация по характеру использования элементов и узлов:

блочные - для выполнения отдельных арифметических операций в структуру АЛУ вводят специальные блоки, что позволяет процесс обработки информации вести параллельно;

конвейерные - в конвейерных АЛУ операция разбивается на последовательность микроопераций, выполняемых за одинаковые промежутки времени (такты) на разных ступенях конвейера, что позволяет выполнять операцию над потоком операндов каждый такт;

многофункциональные - это универсальные АЛУ, выполняющие множество операций в одном устройстве. В таких АЛУ требуется настройка на выполнение данной операции при помощи кода операции.

5.Классификация по временным характеристикам.

По временным характеристикам АЛУ делятся на:

синхронные - в синхронных АЛУ каждая операция выполняется за один такт.

Асинхронные - не тактируемые АЛУ, обеспечивающие высокое быстродействие, так как выполняются на комбинационных схемах.

6.Классификация по структуре устройства управления:

АЛУ с жесткой логикой устройства управления;

АЛУ с микропрограммным управлением.

Структура АЛУ представлена на рисунке 1.

Рисунок 1 – Структура АЛУ

Исходные данные (операнды) по командам УУ (см выше) считываются из ОЗУ в регистры первого и второго операндов (связь 1).

Из УУ в блок управления АЛУ поступает команда на выполнение той или иной операции (связь 2), которая передается им в операционную часть (связь 3).

В соответствии с этой командой операционная часть выполняет нужное действие с данными, которые выбираются из регистров первого и второго операндов (связь 6). Результат заносится в регистр результата (связь 4), откуда – в ОЗУ (связь 5).

Структура регистров АЛУ, куда помещаются исходные и результирующие данные, а также размер регистров (число двоичных разрядов t) формируют понятие разрядной сетки (далее – сетки), которое используется ниже.

Таким образом, структура АЛУ определяется набором микроопераций, необходимых для выполнения заданных арифметических, логических и специальных операций, а задачу построения АЛУ можно свести к задаче определения набора микроопераций, который позволяет составить микропрограмму любой из заданных операций. Такой набор легко получить, если записать микропрограммы всех операций, выполняемых в АЛУ, и выбрать из них все микрооперации, входящие в микропрограммы хотя бы один раз. Однако, если при этом алгоритм операций выбирать произвольно, то количество микроопераций, входящих в полный набор, может оказаться слишком большим и, следовательно, АЛУ будет сложным.

Рассмотрим особенность реализации арифметико-логического устройства компьютера на примере проектирования АЛУ для выполнения логических операций. Классическая ЭВМ состоит из трех основных устройств: арифметико-логического устройства, устройства управления и запоминающего устройства. Рассмотрим особенность структуры арифметико-логического устройства. В современных ЭВМ арифметико-логическое устройство не является самостоятельным схемотехническим блоком. Оно входит в состав микропроцессора, на котором строится компьютер. Однако знание структуры и принципов работы АЛУ весьма важно для понимания работы компьютера в целом.

В микропроцессорной системе есть арифметико-логическое устройство для выполнения логических операций над числами (операндами, словами) выполняются в главной части процессора - арифметико-логическом устройстве (АЛУ)

Все арифметические действия с двумя числами (сложение, вычитание, умножение, деление) сводятся в АЛУ к операции сложения или вычитание.

Упрощенная структура ЭВМ содержит следующие основные устройства: арифметико-логическое устройство, память, управляющее устройство, устройство ввода данных в машину, устройство вывода из нее результатов расчета и пульт ручного управления.

В данном курсовом проекте я буду рассматривать работу многофункционального арифметико-логического устройства (АЛУ). АЛУ для выполнения логических операций, они служат для выполнения арифметических и логических преобразований над словами, называемыми в этом случае операндами, а также арифметические операции.

Быстродействие АЛУ во многом определяет производительность процессора.

Целью данной курсовой работы является исследование и принцип работы арифметико-логического устройства для выполнения логических операций.

Основными задачами являются:

1. исследовать арифметико-логического устройства для выполнения логических операций;

2. привести условно–графическое обозначение микросхемы регистра, входящего в состав арифметико-логического устройства;

3. описать принцип работы арифметико-логического устройства;

4. рассмотреть логическую схему регистра;

5. проанализировать принцип записи, чтения и хранения информации в регистре;

6. указать на схеме сигналы, передаваемы на информационные входы регистра; указать номера и типы входов, на которые подаются управляющие сигналы в режиме записи; указать на выходах двоичное число, зафиксированное в регистре после выполнения сдвига влево на 4 разряда; указать номер входа, на который поступают импульсы сдвига;

7. проанализировать работу сумматора входящего в арифметико-логического устройства;

8. построить логическую схему сумматора;

9. описать принцип работы сумматора

1. ОПИСАНИЕ АРИФМЕТИКО–ЛОГИЧЕСКОГО УСТРОЙСТВА

Арифметико-логическое устройство (АЛУ) - центральная часть процессора, выполняющая арифметические и логические операции.

АЛУ реализует важную часть процесса обработки данных. Она заключается в выполнении набора простых операций. Операции АЛУ подразделяются на три основные категории: арифметические, логические и операции над битами. Арифметической операцией называют процедуру обработки данных, аргументы и результат которой являются числами (сложение, вычитание, умножение, деление. ). Логической операцией именуют процедуру, осуществляющую построение сложного высказывания (операции И, ИЛИ, НЕ. ). Операции над битами обычно подразумевают сдвиги.

АЛУ состоит из регистров, сумматора с соответствующими логическими схемами и элемента управления выполняемым процессом. Устройство работает в соответствии с сообщаемыми ему именами (кодами) операций, которые при пересылке данных нужно выполнить над переменными, помещаемыми в регистры.

Арифметико-логическое устройство функционально можно разделить на две части:

а) микропрограммное устройство (устройство управления), задающее последовательность микрокоманд (команд);

б) операционное устройство (АЛУ), в котором реализуется заданная последовательность микрокоманд (команд).

Рисунок. 1 Структурная схема АЛУ

Структурная схема АЛУ и его связь с другими блоками машины показаны на рисунке 1. В состав АЛУ входят регистры Рг1 - Рг7, в которых обрабатывается информация, поступающая из оперативной или пассивной памяти N1, N2, . NS; логические схемы, реализующие обработку слов по микрокомандам, поступающим из устройства управления.

Закон переработки информации задает микропрограмма, которая записывается в виде последовательности микрокоманд A1,A2, . Аn-1,An. При этом различают два вида микрокоманд: внешние, то есть такие микрокоманды, которые поступают в АЛУ от внешних источников и вызывают в нем те или иные преобразования информации (на рис. 1 микрокоманды A1,A2. Аn), и внутренние, которые генерируются в АЛУ и воздействуют на микропрограммное устройство, изменяя естественный порядок следования микрокоманд. Например, АЛУ может генерировать признаки в зависимости от результата вычислений: признак переполнения, признак отрицательного числа, признак равенства 0 всех разрядов числа др. На рис. 1 эти микрокоманды обозначены р1, p2. рm.

Результаты вычислений из АЛУ передаются по кодовым шинам записи у1, у2, . уs, в ОЗУ. Функции регистров, входящих в АЛУ: Рг1 – регистр (или сумматоры) - основной регистр АЛУ, в котором образуется результат вычислений; Рг2, РгЗ - регистры слагаемых, сомножителей, делимого или делителя (в зависимости от выполняемой операции); Рг4 - адресный регистр (или адресные регистры), предназначен для запоминания (иногда и формирования) адреса операндов и результата; Ргб - k индексных регистров, содержимое которых используется для формирования адресов; Рг7 - i вспомогательных регистров, которые по желанию программиста могут быть аккумуляторами, индексными регистрами или использоваться для запоминания промежуточных результатов.

Часть операционных регистров является программно-доступной, то есть они могут быть адресованы в команде для выполнения операций с их содержимым. К ним относятся: сумматор, индексные регистры, некоторые вспомогательные регистры.

Остальные регистры программно-недоступные, так как они не могут быть адресованы в программе. Операционные устройства можно классифицировать по виду обрабатываемой информации, по способу обработки информации и логической структуре.

АЛУ может оперировать четырьмя типами информационных объектов: булевскими (1 бит), цифровыми (4 бита), байтными (8 бит) и адресными (16 бит). В АЛУ выполняется не сколько различных операций пересылки или преобразования этих данных. Так как используется 11 режимов адресации (7 для данных и 4 для адресов), то путем комбинирования "операция/ режим адресации" базовое число команд 111 расширяется до 255 из 256 возможных при однобайтном коде операции.

2. ОПИСАНИЕ БЛОКА РЕГИСТРА

В задании используются универсальные регистры, разрядность которых (n) можно определить по количеству выходов. В регистре к1500ир141 имеется 4 выходов следовательно разрядность регистра (n) будет равна 4 Микросхема к1500ир141 представляет собой регистр, состоящий из 4 D-тиггеров. Выходы М01 и М02 позволяют выбрать один из четырех режимов работы регистра: загрузка данных, хранение данных, сдвиг данных в лево или в право. Все операции (кроме хранения) происходят по положительному перепаду на тактовом входе С. Регистр имеет 2 последовательных входа SIL (вход данных для сдвига в право) и SIR (вход данных для сдвига влево). При напряжении высокого уровня на входах М01 и М02 регистр хранит данные независимо от сигналов на других входах. Условно графическое обозначение микросхемы к1500ир141 представлено на рисунке 2.

Рисунок 2-Условно графическое обозначение микросхемы к1500ир141 и обозначение входов и выходов

Для данной микросхемы существуют 2 способа записи информации последовательный и параллельный. При последовательном способе записи сигнал V должен быть низкого уровня, а код, который записывается, должен поступать на вход D0. С каждым тактовым импульсом М01 входной код продвигается на один разряд в сторону старшего разряда. При параллельном способе записи код подается на входы D4-D1. Запись проводится в паузе между тактовыми импульсами М01 при V=1 импульсом М02. Если после записи число нужно сдвинуть, то регистр переводят в режим сдвига сигналом V=0 и руководят с помощью импульсов М01. При условии, что Q1 - выход младшего разряда, а Q4 - старшего, информация в регистре сдвигает влево (обратной сдвиг). Но он может быть преобразован и в регистр со сдвигом вправо (прямой сдвиг). Для этого необходимо выполнить следующие внешние соединения: D3 с Q4, D2 с Q3, D1 с Q2. Код записывают по входу D4 при V = 1, а руководят регистром тактовыми импульсами М02. Таким образом, в рассмотренном регистре выполняются условия как прямого, так и обратного сдвигов. Регистр имеет выходы от всех разрядов, что позволяет считывать записанный код как в последовательной, так и в параллельной формах представления информации во времени.

Рисунок 3 – Логическая схема регистра к1500ир141

Регистр к1500ир141 является универсальными (регистр общего назначения), он может использоваться для временного хранения любых данных, при этом позволять работать как с регистром целиком, так и отдельно и с каждой его половиной, (регистры АН, ВН, СН, DH -- старшие (High) байты, а регистры AL, BL, CL, DL -- младшие (Low) байты, соответствующих двухбайтовых регистров). Но также универсальный регистр к1500ир141 может использоваться и как специальный при выполнении некоторых конкретных команд программы.

В данной работе требуется рассчитать сигналы на выходе микросхемы к1500ир141 после подачи на вход двоичного сигнала 1110 при сдвиге влево на 4 разряда. При сдвиге влево происходит смещение операнда на более уровень а на его место устанавливается сигнал 0. Процесс сдвига показан в таблице 2.

Таблица 2 – процесс сдвига влево на 4 разряда.

Число сдвига 1 1 1 0

Число после 1-го сдвига 1 1 0 0

Число после 2-го сдвига 1 0 0 0

Число после 3-го сдвига 0 0 0 0

Число после 4-го сдвига 0 0 0 0

Результатом сдвига будет двоичное число 0000.

3. ПРОЕКТИРОВАНИЕ СУММАТОРА

Параллельные четырехразрядных сумматоры предназначены для одновременного суммирования двух четырехразрядных чисел и характеризуются различными способами передачи сигналов переноса от младших разрядов сумматора к старшим.

Четырехразрядные сумматоры выполняют операцию арифметического сложения двух четырехразрядных двоичных чисел. Количество входов и выходов сумматора определяется разрядностью слагаемых. Быстродействие сумматора определяется временами распространение сигнала через все его элементы, и потому оно значительно ниже быстродействия элементов.

Рисунок 4 – Двоичный сумматор К555ИМ3

13-ввход переноса; 10,11,8,7,3,4,1,16-входы ;12-общий; 9,6, 2, 15-выходы суммы; 5-UЛ выход переноса.

Необходимо спроектировать сумматор, который имеет модель типа К555ИМ3. Для того чтобы узнать сигналы на выходе четырехразрядного сумматора К555ИМ3 при подаче на входы сигналов 0100 и 1101, необходимо сложить эти числа.

С = 0011 - первое слагаемое

D = 1100 - второе слагаемое

_ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _

С+D = 01111 - сумма

Таблица 1 – сигналы на сумматоре поле выполнения операции

Сумма этих чисел и будет на выходе сумматора. Сигналы на входе и выходе сумматора показаны на рисунке 5

| DD2 | A4 | 0 | P4 | 0 |

| B4 | 1 | |||

| A3 | 1 | S4 | 1 | |

| B3 | 1 | |||

| A2 | 1 | S3 | 1 | |

| B2 | 1 | |||

| A1 | 0 | S2 | 1 | |

| B1 | 1 | |||

| P0 | 0 | S1 | 1 |

Для построение 8 разрядного сумматора необходимо соединить 2 четырехразрядных сумматора К555ИМ3, способом, показанным на рисунке 5

Рисунок 5 – Способ построения 8 разрядного сумматора на базе двух четырехразрядных сумматора К555ИМ3

При построении сумматора для восьмиразрядных чисел нужно учитывать, что на входы этого сумматора слагаемые поступают параллельно, а перенос между разрядами передается последовательно.

Для расчета сигналов на выходе восьмиразрядного сумматора при подаче на вход сигналов 11110000 и,00000001 необходимо сложить эти числа.

Выполним сложение двух восьмиразрядных чисел С и D.

С = 1111 0000 - первое слагаемое

D = 0000 001 - второе слагаемое

_ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _

С+D = 01111 0001 - сумма

2 тетрада 1 тетрада

1 тетрада – 4 младших разряда числа

2 тетрада – 4 старших разряда числа

Для сложения старшие разряды чисел С и D поступают на информационные входы микросхемы DD2, а цифры младших разрядов – на входы DD1 параллельным способом. Сигналы на выходах и входах микросхему после выполнения операции показаны на таблице 2

Таблица 2 – Значения сигналов на выходах и входах микросхему К555ИМ3 после выполнения сложения 11110000 и 00000001.

| DD2 | A4 | 0 | P4 | 0 |

| B4 | 1 | |||

| A3 | 0 | S4 | 1 | |

| B3 | 1 | |||

| A2 | 1 | S3 | 1 | |

| B2 | 0 | |||

| A1 | 1 | S2 | 1 | |

| B1 | 0 | |||

| P0 | 1 | S1 | 1 | |

| DD1 | A4 | 0 | P4 | 0 |

| B4 | 1 | |||

| A3 | 0 | S4 | 0 | |

| B3 | 1 | |||

| A2 | 1 | S3 | 0 | |

| B2 | 0 | |||

| A1 | 1 | S2 | 0 | |

| B1 | 0 | |||

| P0 | 0 | S1 | 1 |

Выполним перевод результата сложения из двоичной системы счисления в десятичную, восьмеричную и шестнадцатеричную системы счисления. Для удобства сначала переведем число в шестнадцатеричную систему счисления, затем в десятичную и восьмеричную системы счисления.

Для перевода двоичного числа в шестнадцатеричную систему счисления необходимо разложить число на тетрады и перевести его в шестнадцатеричную систему счисления, затем сложить их согласно приоритету тетрада.

Для перевода в десятичную систему счисления необходимо разложить шестнадцатеричное число на разряды, затем каждый разряд, начиная с младшего умножить на 16 в степени старшинства разряда начиная с нулевой степени, после чего сложить результат.

Для перевода из десятичной системы счисления в восьмеричную необходимо разделить десятичное число на 8 до деления без остатка, результатом будет число сложное из остатков от деления, начиная с последнего остатка

|

241 8 |

| 240 30 8 |

1 24 3 |

| 6 |

011110001 (2) 24110) 361F1(16)

Заключение

Исследуя в данной курсовой работе многофункциональное арифметическо-логическое устройство, я пришел к выводу, что АЛУ реализует важную часть процесса обработки данных вычислительных операций. В результате работы были рассмотрены схемы обобщенной структуры АЛУ процессоров, построены структурная и логическая схемы, был произведен анализ и построение блоков, составляющих важную часть АЛУ. Исходя из задания, спроектирован регистр левого сдвига К1500ИР141, приведена логическая схема четырехразрядного регистра К1500ИР141, перечислены основные функции, выполняемые заданным регистром. регистра, на схеме указаны сигналы, подаваемые на информационные входы регистра. Спроектирован и рассчитан четырехразрядный двоичный сумматор. Приведено условное графическое обозначение микросхемы данного двоичного сумматора. Описан принцип работы. Построена логическая схема четырехразрядного сумматора последовательного действия на базе полусумматоров и логических элементов ИЛИ. Приведена схема соединения микросхем

1. Калабеков Б.А., Мамзелев И.А. Цифровые устройства и микропроцессорные системв. – М.: Радио и связь. 2004.

2. Коган И.Л., Гитлиц Э.В., Еремина О.В. Микропроцессорные устройства. Сборник методических указаний. – М.: ВЗТС, 2003.

3. Мышляева И.М. Цифровая схемотехника. Учебник для сред. проф. образования. – М.: 2005.

4. Основы микропроцессорной техники. Курс лекций/ Новиков Ю.В., Скоробогатов П.К. – М.: 2003.

6. Цифровая и вычислительная техника: Уч. для вузов / Э.В. Евреинов, Ю.Т. Бутыльский, И.А. Мамзелев и др.; Под ред. Э.В. Евреинова. - М.: Радио и связь, 1991.

Читайте также: