Что такое прерывание в информатике сообщение

Обновлено: 08.07.2024

Прерывание – прекращение линейного выполнения задач и принудительная передача управления от выполняемой программы ОС-ме при возникновении какого-либо события.

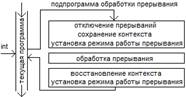

Этапы обработки прерывания:

1) Установление факта прерывания и его идентификация; 2) Запоминание состояния прерванного процесса (аппаратное сохранение); 3) Передача управления в обработчик прерывания; 4) Программное сохранение информации о прерванном процессе; 5) Обработка прерываний; 6) Программное восстановление контекста прерванного процесса; 7) Возврат управления прерванной программе (аппаратное восстановление).

Данный механизм обработки прерываний выполняется независимо от архитектуры вычислительной системы и реализуется при помощи аппаратно-программных средств.

Прерывания можно разделить на 2 основные группы:

1) Внешние (асинхронные) – возникающие вне МП (прерывания клавиатуры, таймера и других внешних устройств);

2) Внутренние (синхронные) – возникающие внутри МП и являющиеся синхронными с его операциями (деление на 0, нарушение правила адресации и пр.).

Зачастую прерывания можно использовать для обращения к супервизору ОС (21h). Однако такая схема используется только в самых простых программных средах. В современных ОСр управление супервизором происходит по другим схемам.

Основные функции механизма прерываний: 1) распознавание и классификация прерываний; 2) передача управления обработчику; 3) корректный возврат в прерванную программу.

Для быстрого перехода в обработчик прерывания используются таблицы, содержащие перечень всех прерываний и адреса их обработчиков. Для корректного возврата из процедуры обработчика необходимо сохранение контекста задачи в спец. области памяти или системный стек.

Физическая структура микропроцессора

Физическая структура микропроцессора достаточно сложна. Ядро процессора содержит главный управляющий и исполняющие модули — блоки выполнения операций над целочисленными данными. К локальным управляющим схемам относятся: блок плавающей запятой, модуль предсказания ветвлений, модуль преобразования CISC-инструкций во внутренний RISC-микрокод, регистры микропроцессорной памяти (в МП типа VLIW до 256 регистров), регистры кэш памяти 1-го уровня (отдельно для данных и инструкций), шинный интерфейс и многое другое.

В состав микропроцессора Pentium обычно входят следующие физические компоненты:

Core — ядро МП;

Execution Unit — исполняющий модуль;

Integer ALU — АЛУ для операций с целыми числами (с фиксированной запятой);

Registers — регистры;

Floating Point Unit — блок для работы с числами с плавающей запятой;

Primary Cache — кэш первого уровня, в том числе кэш данных (Data Cache) и кэш команд (Code Cache);

Instruction Decode and Prefetch Unit и Branch Predictor - блоки декодирования инструкций, опережающего их исполнения и предсказания ветвлений;

Bus Interface — интерфейсные шины, в том числе 64- и 32-битовая, и выход на системную шину к оперативной памяти.

Функционально МП можно разделить на две части:

операционную часть, содержащую устройство управления (УУ), арифметико-логическое устройство (АЛУ) и микропроцессорную память (МПП) (за исключением нескольких адресных регистров);

интерфейсную часть, содержащую адресные регистры МПП; блок регистров команд — регистры памяти для хранения кодов команд, выполняемых в ближайшие такты; схемы управления шиной и портами.

Обе части МП работают параллельно, причем интерфейсная часть опережает операционную, так что выборка очередной команды из памяти (ее запись в блок регистров команд и предварительный анализ) выполняется во время выполнения операционной частью предыдущей команды. Современные микропроцессоры имеют несколько групп регистров в интерфейсной части, работающих с различной степенью опережения, что позволяет выполнять операции в конвейерном режиме. Такая организация МП позволяет существенно повысить его эффективное быстродействие.

32.

РЕГИСТРЫ

Регистры — это последовательностные устройства, предназначенные для приема, хранения, простых преобразований и передачи двоичных чисел. Под простыми преобразованиями понимаются сдвиг чисел на заданное количество разрядов, а также преобразование последовательностного двоичного кода в парачлельный и параллельного в последовательностный., разовыми элементами регистров являются триггеры, когорые дополняются комбинационными логическими элементами для реализации различных связей между разрядами регистра и управления приемом и передачей операндов. Основное функциональное назначение регистров — оперативная память для многоразрядных двоичных чисел.

В зависимости от способа приема и передачи двоичной информации различают параллельные, последовательные, последовательно-параллельные, параллельно-последовательные и универсальные регистры.

В параллельных регистрах или регистрах памяти вывод всех разрядов числа производится одновременно один такт. Для построения -разрядного регистра памяти требуется триггеров.

Параллельные регистры служат основным функциональным элементом для построения оперативных запоминающих устройств.

В последовательных регистрах ввод/вывод информации осуществляется через один информационный вход и один выход поразрядно со сдвигом числа. Поэтому последовательные регистры называют сдвигающими (или сдвиговыми). За один такт вводимая или выводимая информация сдвигается на один разряд вправо или влево. Сдвигающие регистры, реализующие по команде управления сдвиги информации вправо или влево, называют реверсивными.

Последовательно-параллельные регистры имеют один информационный вход для последовательного ввода числа в режиме сдвига и выходные вентили для выдачи -разрядного числа параллельным кодом. Такие регистры выполняют преобразование последовательного кода в параллельный.

В параллельно-последовательные регистры информация вводится параллельным кодом за один такт через тактируемые входные вентили, а выводится из них последовательно по одному разряду в каждом тактовом интервале. Тем самым реализуется операция преобразования параллельного кода в последовательный.

Универсальные регистры сочетают в себе возможности вышеперечисленных типов регистров и, кроме того, обеспечивают режимы отключения входов и выходов (третье логическое состояние) регистра от общей информационной шины, перекоммутацию местами входов и выходов регистра и тем самым переключение функций прием передача информации в общую информационную шину.

Технические параметры регистров определяются параметрами их основного фуикциоиального узла — триггера и разрядностью операнда.

Параллельные регистры. При построении параллельных регистров обычно используются простейшие асинхронные -триггеры и синхронные RS- и На рис. 6.22 представлены варианты параллельных регистров, отличающиеся типом триггеров и составом входных выходных информационных . Регистр на основе асинхронных -триггеров (рис. ) перед занесением очередного -разрядного числа входов требует предварительного сброса всех триггеров в нулевое состояние. Сброс производится сигналом . Ввод информации в регистр происходит по сигналу .

Для этого на входе регистра требуется вдвое больше логических элементов и лнний связи. В схеме показан способ выдачи информации в прямом коде (команда и/или в обратном коде (команда . Асинхронные -триггеры в сочетании со входными вентилями (рис. 6.22,а, в) но существу образуют варианты синхронных -триггеров.

На рис. 6.22,в показана схема параллельного регистра на основе синхронных -триггеров. Здесь в качестве входных используются логические элементы, входящие в схему -триггеров. Ввод информации происходит на интервале синхронизации при .

В качестве выходных использованы логические элементы И—ИЛИ—НЕ, которые формируют выходные сигналы согласно выражению

т. е. при информация из регистра выдается в прямом коде, а при — в обратном.

Если выражение (6.16) тождественно преобразовать к одной из форм

то выходную цепь регистра (рис. 6.22,в) можно реализовать на логических элементах ИСКЛЮЧАЮЩЕЕ ИЛИ (рис. 6.22,г). Выбор способа ввода информации в регистр или ее вывода обычно обусловлен требованиями быстродействия и условиями реализации регистра в цифровом устройстве.

Сдвигающие регистры. Рассмотрим последовательные, последовательно-параллельные и параллельно-последовательные регистры, которые должны выполнять операцию сдвига при последовательном вводе и/или выводе информации.

Сдвиг числа реализуется перезаписью состояний между соседними триггерами регистра в направлении сдвига. Таким образом, каждый разряд регистра одновременно принимает информацию из предыдущего разряда и передает информацию в последующий. Во избежание явления гонок эти процессы должны быть разделены во времени. Это достигается включением элементов линий задержек в связи между разрядами либо использованием двухтактных триггеров. В интегральной схемотехнике статические сдвигаюющие регистры строятся преимущественно на двухтактных D- и -триггерах.

При однонаправленном сдвиге информации достаточно реализовать непосредственные связи между выходами предыдущего и входами последующего триггера -типа (рис. 6.23,а, б). В сдвигающем регистре на -триггерах (рис. ) для передачи информации между разрядами требуется связь между , а в случае использования -триггеров (рис. ) — двойные связи; .

В остальном структуры, принцип работы и параметры данных регистров аналогичны. Ввод информации может производиться последовательно со входа X с последующим сдвигом информации вправо на один разряд по каждому синхроимпульсу С либо параллельно со входов А по сигналу асинхронной записи числа в предварительно очищенный региар (сигналом асинхронного сброса триггеров в состояние ) По положительному фронту синхроимпульса происходит запись информации со входов D и X в триггеры первых ступеней М. Выходные уровни триггеров при этом остаются неизменными (см. рис. 6.23,в). По отрицательному фронту синхроимпульса входы ступени М блокируются и записанная в них информация передается в триггеры ступени S. Происходит переключение выгодных уровней -трнггеров. Таким образом, реализуется чисто последовательный регистр со сдвигом числа вправо (показано стрелкой на рис. 6.23,в, вход — X, выход — ), последовательно-параллельный (вход — X, выходы — ) и параллельно-последовательный (входы — , выход — ). Кроме того, при замыкании выхода последнего разряда с последовательным входом X (штриховая линия) реализуется кольцевой сдвигающий регистр. Информация в кольцевой регистр вводится параллельным кодом со входов и затей циркулирует в замкнутом кольце под действием тактовых синхроимпульсов С.

Кольцевые регистры удобно использовать для построения, например, тактовых генераторов цифровых устройств.

В реверсивных сдвигающих регистрах для обеспечения возможности сдвига информации в обоих направлениях выход каждого разряда должен быть связан через логические элементы переключения направления сдвига со входами предыдущего и последующего разрядов. Пусть направление сдвига задается логическим уровнем сигнала Е так, что при осуществляется сдвиг вправо. , а при происходит сдвиг влево; . Тогда триггер реверсивного сдвигающего регистра должен управляться сигналом который формируется логическим элементом И—ИЛИ—НЕ (рис. 6.24, а) либо на логических элементах .

Для сигнала в соотношении (6.17) используется сигнал последовательного входа при сдвиге вправо или при построении кольцевого сдвигающего вправо регистра. Аналогично , в качестве сигнала используется последовательный вход У при сдвиге влево или , для кольцевого сдвигающего влево регистра. На рис. 6.24, б показан тождественный согласно выражению (6.17) вариант схемы управления разрядом реверсивного сдаигающего регистра.

На рис. 6.25 показан вариант реверсивного сдвигающего регистра на основе -триггеров. Сигнал на входах определяется аналогично согласно выражению (6.17), а на выходах всегда благодаря инверторам во входных цепях.

Параллельный ввод информации в асинхронном режиме в сдвигающие регистры возможен, например, через несинхронизируемые входы R и S. Синхронный параллельный ввод реализуется через систему логических элементов управления сдвигом. Так как в данном случае предусматриваются состояния регистра (параллельный ввод, сдвиг вправо, сдвиг влево), одного двоичного управляющего сигнала Е уже недостаточно для управления ими. Пусть два управляющих режимом работы сигнала кодируют состояние регистра в соответствии с табл. 6.4.

Тогда входы D и С разряда определяются следующими логическими уравнениями:

Соответствующий сдвигающий регистр на основе -триггеров показан на рис. 6.26. Здесь — входы параллельного ввода информации, X — последовательный вход для сдвига вправо, Y — последовательный вход для сдвига влево.

Динамические регистры — регистры, для которых определена верхняя граница временного интервала хранения информации без восстановления. Чаще всего в них физическим носителем информации является заряд некоторой емкости или зарядовый пакет в объеме полупроводника [4; 14]. Для управления зарядом используют МДП-транзисторы, обладающие весьма большим сопротивлением в запертом состоянии Ом). Используя логические элементы на МДП-транзисторах, можно по заданному алгоритму управлять зарядом и напряжением на некоторой паразитной емкости.

На рис. показана схема -тактного динамического регистра на -МДП-транзисторах, каждый разряд которого выполнен на шести транзисторах . Каждый разряд содержит два тактируемых ключа на транзисторах соответственно — эквивалентные входные емкости ключей.

Пусть на вход разряда поступает от разряда логический сигнал , которому соответствует электрический сигнал , и все остальйые емкости разряжены.

Прерывание — сигнал к процессору , испускаемый аппаратными средствами или программным обеспечением, и указывающий на событие, которое требует немедленного внимания. Прерывание предупреждает процессор о высокоприоритетном состоянии, требующем прерывания текущего кода, выполняемого процессором. Процессор отвечает, приостанавливая свои текущие действия, сохраняя свое состояние и выполняя функцию, называемую обработчиком прерываний (или подпрограммой обработки прерываний, ISR) для обработки события. Это прерывание является временным, и после завершения обработки обработчика прерывания процессор возобновляет обычную работу. Существует два типа прерываний: аппаратные прерывания и программные прерывания. [1]

Каждое прерывание имеет свой собственный обработчик прерываний. Количество аппаратных прерываний ограничено числом строк запроса прерывания (IRQ) для процессора, но могут быть сотни различных программных прерываний. Прерывания — это широко используемая техника многозадачности компьютеров, в первую очередь в реальном времени. Такая система называется управляемой прерываниями.

Содержание

История

Типы прерываний

Прерывания могут быть разделены на следующие типы:

- Маскируемое прерывание (IRQ): аппаратное прерывание, которое можно игнорировать, устанавливая бит в битовой маске регистра маски прерываний (IMR).

- Немаскируемое прерывание (NMI): аппаратное прерывание, в котором отсутствует связанная битовая маска, поэтому ее нельзя игнорировать. NMI используются для задач с высшим приоритетом, например таких как таймеры.

- Межпроцессорное прерывание (IPI): особый случай прерывания, которое генерируется одним процессором для прерывания другого процессора в многопроцессорной системе.

- Программное прерывание: прерывание, генерируемое в процессоре путем выполнения инструкции. Программные прерывания часто используются для реализации системных вызовов, поскольку они приводят к вызову подпрограммы с изменением уровня вызова ЦП.

- Ложное прерывание: нежелательное аппаратное прерывание. Как правило, такие прерывания генерируются системными условиями, такими как электрические помехи в линии прерывания или из-за технически неправильно разработанного оборудования.

Процессоры обычно имеют внутреннюю маску прерываний, которая позволяет программному обеспечению игнорировать все внешние аппаратные прерывания, пока она установлена. Установка или очистка этой маски может быть быстрее, чем доступ к регистру маски прерываний (IMR) в PIC или отключение прерываний в самом устройстве. В некоторых случаях, например в случае архитектуры x86, отключение и включение прерываний на самом процессоре действует как барьер памяти.

Прерывание, которое оставляет машину в четко определенном состоянии, называется точным прерыванием. Такое прерывание имеет четыре свойства:

- Счетчик программ (PC — Program Counter) сохраняется в известном месте.

- Все инструкции перед тем, на который указывает счетчик программ, полностью выполнены.

- Никакая инструкция, кроме той, на которую указывает счетчик программ, не была выполнена, или любые такие инструкции отменяются до обработки прерывания.

- Состояние выполнения инструкции, на которую указывает счетчик программ, известно.

Прерывание, которое не соответствует указанным выше требованиям, называется неточным прерыванием.

Аппаратные прерывания

Аппаратные прерывания используются устройствами для передачи информации о том, что они требуют внимания со стороны операционной системы. [4] Внутренние аппаратные прерывания реализуются с использованием электронных сигналов оповещения, которые отправляются процессору от внешнего устройства, которое является частью самого компьютера, например контроллер диска, или внешнее периферийное устройство. К слову, нажатие клавиши на клавиатуре или перемещение мыши вызывают аппаратные прерывания, которые заставляют процессор считывать нажатие клавиши или положение мыши. В отличие от типа программного обеспечения, аппаратные прерывания являются асинхронными и могут произойти в середине выполнения инструкции, что требует дополнительного внимания при программировании. Акт инициирования аппаратного прерывания называется запросом прерывания (IRQ). [1]

Программные прерывания

Сложность с разделением линий прерывания

Некоторые устройства с плохо разработанным программным интерфейсом не позволяют определить, запросили ли они обслуживание. Они могут запереться или иным образом плохо себя вести, если их обслуживают, когда они этого не хотят. Такие устройства не могут терпеть паразитные прерывания, а также не могут терпеть совместное использование линии прерывания. Карты ISA , из-за зачастую дешевого дизайна и конструкции, печально известны этой проблемой. Такие устройства становятся все более редкими, поскольку аппаратная логика становится дешевле, а новые системные архитектуры требуют разделяемых прерываний. [1]

Проблемы с производительностью

Прерывания обеспечивают низкую нагрузку и хорошую задержку при низкой нагрузке, но значительно ухудшаются при высокой частоте прерываний, если не предпринимаются меры для предотвращения нескольких патологий. Это различные формы живых блокировок , когда система тратит все свое время на обработку прерываний, исключая другие необходимые задачи. В экстремальных условиях большое количество прерываний (например, очень высокий сетевой трафик) может полностью остановить систему. Чтобы избежать таких проблем, операционная система должна планировать обработку сетевых прерываний так же тщательно, как и планирование выполнения процесса.

С многоядерными процессорами, дополнительные улучшения производительности в обработке прерываний могут быть достигнуты с помощью масштабирования на стороне приема (RSS), когда используются сетевые адаптеры с несколькими очередями. Такие NIC предоставляют несколько очередей приема, связанных с отдельными прерываниями; путем маршрутизации каждого из этих прерываний на разные ядра обработка запросов на прерывание, запускаемых сетевым трафиком, полученным одним NIC, может быть распределена между несколькими ядрами. Распределение прерываний между ядрами может выполняться операционной системой автоматически, либо маршрутизация прерываний (обычно называемая привязкой IRQ) может быть настроена вручную.

Чисто программная реализация распределения принимаемого трафика, известная как управление приемными пакетами (RPS), распределяет принятый трафик между ядрами позже в тракте данных как часть функциональности обработчика прерываний. Преимущества RPS по RSS не включают требований к конкретному оборудованию, более продвинутым фильтрам распределения трафика и уменьшенной частоте прерываний, создаваемых NIC. Как недостаток, RPS увеличивает частоту межпроцессорных прерываний (IPI). Управление потоком приема (RFS) расширяет программный подход, учитывая локальность приложений; Дальнейшее улучшение производительности достигается за счет обработки запросов на прерывание теми же ядрами, на которых конкретные сетевые пакеты будут использоваться целевым приложением. [1]

Типичное использование

Типичное использование прерываний включает в себя следующее: системные таймеры, дисковый ввод / вывод, сигналы-выключение и ловушки. Существуют прерывания для передачи байтов данных с использованием UART или Ethernet; для чувствительных нажатий клавиш, управления двигателями и т.д.

Другое типичное использование состоит в том, чтобы генерировать периодические прерывания путем деления выходного сигнала кварцевого генератора и с помощью обработчика прерываний подсчитывать прерывания, чтобы процессор мог сохранять время. Эти периодические прерывания часто используются планировщиком задач ОС для перепланирования приоритетов запущенных процессов. Некоторые старые компьютеры генерировали периодические прерывания от частоты линии электропередачи, потому что она контролировалась коммунальными службами, чтобы исключить длительный дрейф электрических часов.

Например, прерывание диска сигнализирует о завершении передачи данных с или на периферийное устройство диска; процесс, ожидающий чтения или записи файла, запускается снова. В качестве другого примера — прерывание при отключении питания прогнозирует или запрашивает потерю мощности, позволяя компьютерному оборудованию выполнять упорядоченное завершение работы. Кроме того, прерывания используются в функциях "typeahead" для буферизации событий, таких как нажатия клавиш .

Прерывания используются для эмуляции инструкций, которые не реализованы на определенных моделях в компьютерной линии. Например, инструкции с плавающей запятой могут быть реализованы в аппаратных средствах в некоторых системах и эмулироваться в более дешевых системах. Выполнение невыполненной инструкции вызовет прерывание. Обработчик прерываний операционной системы распознает возникновение невыполненной инструкции, интерпретирует инструкцию в программной подпрограмме и затем вернется к программе прерывания, как если бы инструкция была выполнена. Это обеспечивает переносимость прикладного программного обеспечения по всей линии. [1]

Мы подошли к моменту, когда без изучения прерываний дальнейшее изучение микроконтроллеров будет делом сложным. Но и сами прерывания являются одной из самых сложных для изучения тем.

Поэтому соберитесь и запаситесь терпением. Прерываниям будет посвящено несколько статей, в которых мы рассмотрим и аппаратные, и программные вопросы. И, разумеется, особенности реализации прерываний в различных семействах микроконтроллеров.

Кроме того, будет полезно вспомнить статью " Микроконтроллеры для начинающих. Часть 2. Процессор микроконтроллера ". В ней показано, в частности, как формируется адрес команды, которую будет исполнять процессор. А так же статью " Микроконтроллеры для начинающих. Часть 3. Процессор микроконтроллера. Тактирование и синхронизация. ". Здесь показано, как организована совместная работа узлов процессора.

Что такое прерывания

Прежде всего, нам надо разобраться, что же такое прерывания. Собственно говоря ответ на этот вопрос кроется в самом термине. Прерывание действительно прерывает нормальное выполнение программы. А управление получает процедура обработки (обслуживания) прерывания, которую кратко называют ISR - Interrupt service routine.

После завершения обработки прерывания выполнение программы продолжается как обычно, с того самого места, в котором прерывание возникло.

Очень похоже на вызов подпрограмм? Да, похоже. Но есть одно важнейшее отличие - программа не должна знать, что прерывание вообще возникало. Программа не должна зависеть от того, возникло прерывание, или нет. За исключением случаев, когда программист такую зависимость предусматривает в явном виде.

А это означает, что переход к обработке прерывания требует дополнительных действий, которые могут выполняться или аппаратно, или программно.

Программные прерывания, синхронные

В микроконтроллерах, тех, что мы рассматриваем, программные прерывания есть только в STM8. Это команда TRAP. Но в микроконтроллерах вообще, тем более, в микропроцессорах, может быть несколько различных программных прерываний.

Программные прерывания всегда синхронные. То есть, они возникают синхронно с ходом выполнения программы, всегда в одном и том же месте - при выполнении команды прерывания.

Программные прерывания можно рассматривать как простой вызов подпрограммы, но адрес этой подпрограммы всегда предопределен и изменить его нельзя. И нельзя передать такой подпрограмме параметры, иначе чем заранее предусмотренные программистом переменные, обычно, глобальные.

Поскольку программные прерывания вызываем мы сами, не требуется сохранение состояния (контекста) процессора. Но поведение конкретного процессора при обработке программных прерываний нужно искать в документации.

Мы не будем рассматривать программные прерывания в рамках данного цикла статей.

Аппаратные прерывания, асинхронные

Сегодня аппаратные прерывания есть в подавляющем большинстве микроконтроллеров. Но исключения все таки есть, например, линейка BaseLine микроконтроллеров PIC.

Аппаратные прерывания всегда асинхронные. То есть, момент их возникновения никак не связан с выполнением программы. Может возникнуть вопрос, как так не связан, а, например, АЦП? Мы же сами запрашиваем преобразование, а значит, возникающее при завершении преобразования прерывание вызвано именно нами, синхронно.

Нет, совсем не синхронно и не нами. Да, мы сами запросили преобразование. Но сколько для преобразования потребуется времени мы не знаем, количество тактов преобразования может зависеть от многих параметров. Поэтому и прерывание все равно возникнет асинхронно.

Аппаратные прерывания могут быть вызваны и внутренними модулями микроконтроллера, и внешними цепями (через специальный вход INT). Кроме того, аппаратные прерывания могут возникать и при выполнении программы, команды. Например, деление на 0. И это тоже асинхронное прерывание.

Приоритеты прерываний

Некоторые аппаратные прерывания могут быть более важными, чем другие. Например, готовность байта полученного из канала связи более важна, чем нажатие кнопки. При этом говорят о приоритете прерываний.

Уровней приоритета может быть несколько. Но возможно и полное отсутствие деления на приоритеты. Если одновременно возникает несколько запросов прерывания, то обрабатываться они будут в порядке убывания приоритета. Реализуется приоретизация аппаратно.

Прерывание может возникнуть во время обработки другого прерывания. В этом случае говорят о вложенности прерываний.

Вложенные прерывания

Процедура обработки прерывания тоже может быть прервана новым прерыванием, но только если его приоритет выше, чем у обрабатываемого. То есть, мы получаем обработку прерывания внутри обработки другого прерывания. Это и есть вложенность.

В большинстве случаев с вложенными прерываниями проблем не возникает. После завершения обработчика более высокого приоритета управление вернется в прерванный обработчик.

Контроллер прерываний

Теперь становится понятным, что обработка прерываний не такой простой процесс. Запуск процедуры обработки прерывания, безусловно, будет процессор. Но вот разбираться с приоритетами, запретами (маскированием) прерываний, другой вспомогательной (но важной!) работой будет специальный модуль - контроллер прерываний. Этот контроллер может быть и очень простым, и очень сложным. И может быть выполнен как в виде модуля внутри микроконтроллера, так и быть внешней микросхемой.

И сегодня основное внимание я буду уделять именно контроллеру прерываний.

Контроллер прерываний

И начнем мы с самого простого случая. Сегодня он скорее гипотетический, но зато позволит начать разбираться с тем, что лежит в самой глубине процессов

Единственный источник прерываний

Сейчас мы будем рассматривать собственно процессор. Причем процессор имеющий единственный вход запроса прерывания.

Простейший контроллер прерываний с единственным источником, фиксированным адресом обработчика, без приоритетов. Иллюстрация моя

Простейший контроллер прерываний с единственным источником, фиксированным адресом обработчика, без приоритетов. Иллюстрация моя

Я не стал показывать всю функциональную схему процессора. Она есть в статьях, ссылки на которые я дал ранее. Здесь же я показал только регистр адреса команды PC и дополнительные узлы, которые используются для обработки прерывания.

Но сначала о регистре PC. Как Вы уже знаете, этот регистр автоматически инкрементируется для перехода к следующей команде. Так же, в него можно загрузить адрес из команд перехода и вызова. Разумеется, этот регистр можно и прочитать.

Я показал, что запись и чтение регистра выполняется через ALU, подписав соответствующие цепи. Все остальные сигналы просто идут к/от других узлов процессора, которые нам сегодня не важны.

Триггер IE_TRIG отвечает за разрешение/запрет прохождения запроса прерывания в процессор. Он может быть частью регистра состояния процессора или частью иного регистра. В данном случае, если он установлен, прерывания разрешены, а если сброшен запрещены.

Триггер INT_TRIG отвечает за хранение запроса прерывания, так как я показал, что вход INT, собственно вывод на который поступает запрос из внешнего мира, является не потенциальным, а импульсным.

Как все это работает. Когда на вход INT поступает импульс запроса прерывания в INT_TRIG записывается 1 (триггер устанавливается). И это выполняется независимо от того, разрешены прерывания или нет. Если прерывания запрещены, то обработка просто будет отложена до момента разрешения. Триггер будет хранить запрос.

На вход процессора сигнал запроса прерывания IF попадет лишь в том случае, если триггер IE_TRIG будет установлен. То есть, если прерывания будут разрешены.

Теперь в игру вступает процессор. И первым делом он запрещает прерывания сбросив IE_TRIG. Теперь нам не важно состояние INT_TRIG поэтому сбрасывается и он. Заодно это позволяет зафиксировать запрос прерывания, который может придти во время обработки текущего прерывания. Далее, обязательно, сохраняет регистр PC.

Выполнив всю дополнительную работу, например, сохранив состояние процессора, процессор записывает в PC адрес процедуры обработки прерывания. Когда процедура обработки завершится она выполнит не команду RET (возврат), а специальную команду IRET (возврат из прерывания).

Теперь процессор снова выполняет всю дополнительную работу, например, восстанавливает состояние процессора. После чего можно восстановить регистр PC. Остается разрешить прерывания.

Теперь программа продолжит работать с того места, где ее выполнение было прервано.

В документации и книгах часто пишут, что восстанавливается состояние разрешения обработки прерываний. Это верно, но не совсем точно. Дело в том, что если уж мы попали в обработчик прерывания, значит прерывания точно были разрешены. И мы можем просто установить IE_TRIG без дополнительных раздумий.

А теперь начнем усложнять нашу задачу. Для начала увеличим количество источников прерывания, но оставим единственный обработчик.

Несколько источников прерываний, единственный обработчик

Ярким представителем такого подхода являются микроконтроллеры PIC, за исключением BaseLine и PIC18.

Контроллер прерываний для нескольких источников, но с единственным обработчиком.Без приоритетов. Цепи сброса триггеров INT_REG не показаны. Иллюстрация моя

Контроллер прерываний для нескольких источников, но с единственным обработчиком.Без приоритетов. Цепи сброса триггеров INT_REG не показаны. Иллюстрация моя

Основное отличие здесь в замене INT_TRIG на INT_REG и появлении дополнительного регистра IE_REG. Кроме того, теперь у нас не IE_TRIG, а GIE_TRIG. Дело в том, что теперь он управляет глобальным разрешением/запретом прерываний. А вот запретить/разрешить конкретный источник мы можем через IE_REG.

В целом, обработка прерываний не изменилась. Автоматически сбрасывается GIE_TRIG, что запрещает все прерывания, глобально. IE_REG автоматически не изменяется, только программно, если это программист это предусмотрел.

А вот со сбросом INT_REG все сложнее и интереснее. Сбросить регистр целиком нельзя, можно только триггер соответствующий обрабатываемому запросу. Но как этот триггер найти? Ответ простой - никак.

Поэтому в подобных контроллерах запросы прерываний от источников не сбрасываются автоматически. Их обязательно нужно сбрасывать вручную.

А как мы можем найти источник запроса, вызвавшего прерывание? У нас ведь обработчик один на всех. Довольно просто - прочитав содержимое INT_REG и проанализировав его биты. Это позволит определить источник и вызвать соответствующую подпроцедуру обработки. Именно она потом и сбросит флаг запроса.

Кстати последовательность анализа битов INT_REG определяет и приоритетность прерывания. Такой вот дополнительный программный бонус. Считаете невозможным, так как прерывания запрещаются автоматически?

Возможно! Достаточно держать прерывания запрещенными глобально. При этом триггеры INT_REG будут фиксировать поступающие запросы. Теперь, разрешив в нужный момент прерывания (глобально) мы можем обработать их все сразу. В нужном нам порядке.

Безусловно, это далеко не универсальный метод. Но это и чистая теория, как может показаться. Дело в том, что несколько запросов (они же асинхронные!) могут придти одновременно. Кроме того, мы можем запрещать прерывания на время выполнения критических участков программы по необходимости. А после их разрешения получить как раз такую вот ситуацию.

Несколько источников, несколько обработчиков

Продолжаем усложнять нашу задачу. Давайте добавим отдельные обработчики для каждого источника прерывания. Это не так просто, как может показаться.

Но сначала нам надо вспомнить, что такое вектор прерывания. В своем первоначальном варианте вектором называлась ячейка памяти хранившая адрес обработчика. Содержимое этой ячейки загружалось в PC, что и приводило к переходу на обработчик. И мы могли спокойно изменять адрес обработчика, просто занеся его в вектор.

Однако, в микроконтроллерах (по крайней мере тех, что мы изучаем) вектор это просто определенный набор ячеек памяти команд на начало которого и передается управление. А программист размещает в векторе команду перехода на нужный обработчик.

Преобразовать номер прерывания (номер источника) в адрес перехода (вектора) достаточно легко. Например, можно сдвинуть номер вектора влево на два разряда и сбросить два младших разряда. И мы получим вектор позволяющий разместить 4 команды.

Фрагмент контроллера прерываний обеспечивающего для каждого источника свой обработчик. Иллюстрация моя

Фрагмент контроллера прерываний обеспечивающего для каждого источника свой обработчик. Иллюстрация моя

Я не стал показывать всю функциональную схему контроллера прерываний, для наглядности. Что у нас здесь добавилось? Во первых, шифратор, причем шифратор приоритетный, что бы корректно обрабатывать ситуацию с несколькими конкурирующими запросами прерываний. Во вторых, мультиплексор, который определяет источник адреса для занесения в регистр PC.

Источниками адресам могут быть адрес команды из ALU, для команд перехода, или адрес вектора из нашего контроллера прерываний.

Запрос прерывания из источника с помощью приоритетного шифратора превращается в номер прерывания. У нас 4 источника, поэтому достаточно 2 бит адреса. Но вектор должен вмещать более одной команды. Поэтому номер вектора мы помещаем в биты 3 и 2 адреса, а биты 1 и 0 сбрасываем, что и показано на иллюстрации.

Это позволяет нам разместить в каждом векторе до 4 команд, а адрес вектора (адрес первой команды) будет равен номеру прерывания умноженному на 4.

В остальном обработка прерываний не изменилась. Но теперь у нас появилась возможность автоматически сбрасывать соответствующий триггер в INT_REG, ведь мы теперь знаем его номер. Я не буду показывать, как это выполняется на функциональной схеме.

Контроллер прерываний с приоритетами

Приоритетный шифратор в предыдущем случае не означает, что у прерываний есть приоритет. Да, он позволяет выбрать из нескольких прерываний одно, с наименьшим номером (наибольшим приоритетом). Но это не делает возможным прервать текущий обработчик прерывания с меньшим приоритетом.

Причина проста, при возникновении прерывания у нас прерывания запрещаются глобально. Я не буду приводить иллюстрацию, она сложна для начинающих, я просто расскажу, как это работает.

Вводится дополнительный регистр, который хранит приоритет текущего обрабатываемого прерывания. Причем, в общем случае, приоритет не равен номеру прерывания. Например, прерывания могут быть сгруппированы по несколько штук в пределах одного приоритета.

Прерывания не запрещаются глобально. Прерывания запрещаются для приоритета текущего прерывания и меньших приоритетов. При поступлении нового запроса специальный компаратор сравнивает его приоритет с текущим (хранится в специальном регистре, как я говорил). Если приоритет нового запроса выше, он поступает в процессор, что приводит к прерыванию текущего обработчика.

Причем это простейший случай. Могут быть предусмотрены дополнительные режимы работы. Например, циклическая смена приоритетов. Причем и приоритетов в группе, и групп приоритетов.

Когда мы будет изучать реализацию контроллеров прерываний в конкретных семействам микроконтроллеров, мы вернемся к приоретизации.

Заключение

Прерывание (interrupt) – событие, требующие немедленной реакции со стороны процессора. Реакция состоит в том, что процессор прерывает обработку текущей программы ( прерываемой программы ) и переходит к выполнению некоторой другой программы ( прерывающей программы ), специально предназначенной для данного события. По завершении этой программы процессор возвращается к выполнению прерванной программы.

Каждое событие, требующее прерывания, сопровождается сигналом прерывания , оповещающим об этом вычислительную машину, и называемым запросом прерывания .

Состояние программы представляет собой совокупность состояний всех запоминающих элементов в соответствующий момент времени (например, после выполнения последней команды). При возникновении прерывания микроконтроллер сохраняет в стеке содержимое счетчика команд и загружает в него адрес соответствующего вектора прерывания. Последней командой подпрограммы обработки прерывания должна быть команда, которая осуществляет возврат в основную программу и восстановление предварительно сохраненного счетчика команд. Во время выполнения обработчика прерывания некоторая информация может подвергнуться изменению. Поэтому при переходе к обработчику прерывания необходимо сохранить элементы, подвергающиеся изменению. Набор таких элементов представляет собой вектор состояния программы . При этом другая информация о состоянии ячеек памяти не существенна или может быть восстановлена программным путем.

Вектор начального состояния содержит всю необходимую информацию для начального запуска программы. Во многих случаях вектор начального состояния содержит только один элемент – начальный адрес запускаемой программы.

Вектор прерывания является вектором начального состояния прерывающей программы (обработчика) и содержит всю необходимую информацию для перехода к обработчику, в том числе его начальный адрес. Каждому типу прерываний соответствует свой вектор прерывания, который инициализирует выполнение соответствующего обработчика. Обычно векторы прерывания хранятся в специально выделенных фиксированных ячейках памяти с короткими адресами, представляющих собой таблицу векторов прерываний . Для перехода к соответствующей прерывающей программе процессор должен располагать вектором прерывания и адресом этого вектора. По этому адресу, как правило, находится команда безусловного перехода к подпрограмме обработки прерывания.

Как правило, управление запоминанием и возвратом возложено на обработчик прерывания. В этом случае обработчик состоит из трех частей – подготовительной ( пролог ) и заключительной ( эпилог ), обеспечивающих переключение программ, и собственно прерывающей программы, выполняющей затребованные запросом операции. Время реакции определяется как временной интервал от момента поступления запроса прерывания до начала выполнения прерывающей программы.

tp – время реакции системы на прерывание;

tз – время запоминания состояния прерываемой программы;

tппр – время собственно прерывающей программы;

tв – время восстановления состояния прерванной программы

При наличии нескольких источников запросов должен быть установлен определенный порядок обслуживания поступающих запросов, называемый приоритетными соотношениями или дисциплиной обслуживания . Совокупность всех возможных типов прерывания процессора представляет собой систему прерывания микроконтроллера. Дисциплина обслуживания определяет, какой из нескольких запросов, поступивших одновременно, подлежит обработке в первую очередь, и имеет ли право данный запрос прерывать тот или иной обработчик прерывания.

В случае если во время обработки прерывания поступает запрос на прерывание с более высоким уровнем приоритета, управление передается обработчику прерывания более высокого приоритета, при этом работа обработчика прерывания с более низким уровнем приоритета приостанавливается. Возникает вложенность прерываний . Максимальное число программ, которые могут приостанавливать друг друга называется глубиной прерываний .

Если запрос прерывания окажется не обслуженным к моменту прихода нового запроса от того же источника (того же приоритета), то возникает насыщение системы прерываний . При этом часть запросов прерывания будет утрачена, что для нормальной работы микроконтроллера недопустимо.

Характеристиками системы прерывания являются:

- общее количество запросов прерывания – количество источников запросов прерывания;

- тип представления прерывания – как правило, запрос прерывания представлен логическим уровнем сигнала;

- приоритет прерывания – определяет очередность обработки каждого запроса прерывания, чем выше приоритет, тем меньше задержка в исполнении прерывающей программы для него;

- время реакции – временной интервал между появлением запроса прерывания и началом выполнения прерывающей программы;

- задержка прерывания – определяется суммарным временем на запоминание и восстановление программы;

- глубина, обычно совпадает с числом уровней приоритетов в системе прерывания;

- насыщение системы прерывания;

- допустимые моменты прерывания программ (как правило, окончание выполнения следующей команды).

Читайте также: