Реферат на тему регистры

Обновлено: 18.05.2024

Регистры сдвига предназначены для выполнения операций приема, хранения и выдачи двоичных чисел в последовательном или параллельном кодах, сдвига кода вправо или влево на заданное число разрядов, задержки передаваемой информации на т тактов. В этих регистрах каждый тактовый импульс инициирует введение разряда двоичного числа в первый триггер и сдвиг содержимого последующих триггеров на один разряд… Читать ещё >

Регистры. Электротехника и электроника ( реферат , курсовая , диплом , контрольная )

Регистром называют устройство, предназначенное для хранения цифровых кодов, сдвига чисел, преобразования параллельного кода в последовательный и выполнения других операций с двоичными числами. Структура регистра представляет собой упорядочснную последовательность триггерных ячеек и комбинационную схему, обеспечивающую ввод, вывод и выполнение логических преобразований. Обычно в регистрах используют универсальные //(-триггеры или //-триггеры задержки. По способу ввода чисел регистры делят на последовательные, параллельные и комбинированные, а, но функциональному назначению выделяют регистры памяти (накопительные) и сдвига.

Регистры памяти предназначены для хранения двоичной информации небольшого объема: байта (8 бит) или двухбайтового слова (16 бит). Структурно они представляют собой п синхронных D-триггеров для хранения одного разряда двоичного числа и комбинационных схем совпадения для разделения операций записи и чтения (рис. 14.8).

Рис. 14.8. Структура регистра памяти.

Ввод кода двоичного числа X = (хп…Х2Хi) осуществляется одновременно во все разряды при подаче единичного сигнала на вход синхронизации С. Вывод хранимого кода на шину Y производят через выходные схемы совпадения при подаче единичного сигнала на вход разрешения чтения с2.

Наращивание разрядности регистров памяти получают добавлением аналогичных регистров и объединением соответствующих входов синхроимпульсов и сброса.

Регистры сдвига предназначены для выполнения операций приема, хранения и выдачи двоичных чисел в последовательном или параллельном кодах, сдвига кода вправо или влево на заданное число разрядов, задержки передаваемой информации на т тактов. В этих регистрах каждый тактовый импульс инициирует введение разряда двоичного числа в первый триггер и сдвиг содержимого последующих триггеров на один разряд вправо. Структура регистра сдвига содержит п двухступенчатых триггеров (рис. 14.9, а).

В трехразрядном регистре сдвига вправо младший разряд вводимого числаХ = (х2ХХ0), например X = 101, подается на вход и записывается в первую ячейку в момент окончания первого синхроимпульса. С приходом следующего сигнала синхронизации (рис. 14.9, б) единица из ячейки первого разряда переносится в следующую, а в нее заносится следующий разряд числах! = 0. За три такта в ре;

Рис. 14.9. Структура однонаправленного регистра сдвига (а) и временная диаграмма (б).

гистр будет записано трехразрядное число, т. е. на выходах ячеек образуются сигналы Q2 = 1, Q = О, Q0 = 1. За следующие три такта хранимое число будет выведено в последовательном коде на выход Y. Для параллельного вывода данных к выходам Q2, QuQo следует подключить схемы совпадения, открываемые разрешающим чтение сигналом. Для построения регистра, смещающего код числа влево, выходы последующего триггера соединяют с входами предыдущего.

Использование в цепях межкаскадных связей комбинационных схем совпадения обеспечивает возможность электрического управления порядком соединения ячеек для получения реверсивного регистра, осуществляющего сдвиг числа влево и вправо. Одной из областей применения реверсивных регистров служит программная организация операций умножения и деления, основанных на том, что сдвиг двоичного числа на один разряд вправо или влево соответствует его умножению или делению на два. Получили распространение комбинированные (универсальные) регистры, в которых управляющие комбинационные схемы обеспечивают параллельный или последовательный ввод и вывод данных с возможностью сдвига вправо и влево.

Регистром называется последовательностное функциональное устройство, предназначенное для хранения двоичной комбинации заданное время. Регистры можно построить на базе RS, JK и Dтриггеров. Наиболее удобно строить регистры на базе D-триггер, потому что они имеют один информационный вход. Число разрядов регистра равно числу используемых триггеров т.к. один триггер хранит один разряд двоичной комбинации. Одиночный триггер можно рассматривать как одноразрядный регистр памяти.

Регистры по способу записи и считывания информации делятся на параллельные (памяти) и последовательные (сдвиговые).

Регистры прежде всего используются для хранения информации. Но на базе регистров также можно построить различные устройства.

На регистрах сдвига наиболее просто реализовать преобразователь последовательного кода в параллельный и наоборот. Их применяют в устройствах аппаратного умножения и деления двоичных чисел, в кодирующих устройствах для синтеза помехоустойчивых кодов, которые могут обнаруживать и исправлять ошибки и т.д.

Регистры сдвига можно использовать также для построения счётчиков, которые носят обще название кольцевые. Часто их еще называют по имени используемого кода.

2 Параллельные регистры

Параллельным (памяти) регистром называется последовательностное функциональное устройство, состоящее из набора синхронных триггеров с независимыми информационными выходами и общим синхронизирующим входом и предназначенное для хранения двоичной комбинации. Число информационных входов и выходов (разрядов) равно числу используемых триггеров.

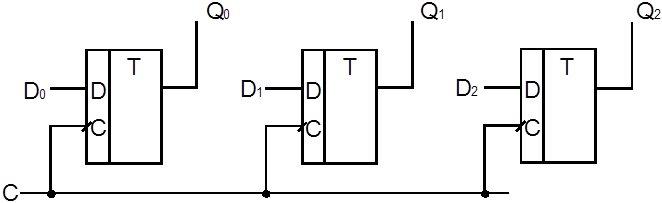

Для создания регистров памяти в интегральном исполнении используются D - триггеры статических и динамических и называют их соответственно статическими и динамическими регистрами. Схема трехразрядного динамического регистра памяти, построенного из динамических D - триггеров показана на рисунке 1.

Данный регистр работает следующим образом. При появлении на синхронизирующем входе C перепада с 0 на 1 информация, находящаяся на выходах D2. D0 записывается в триггеры и хранится там до появления следующего перепада с 0 на 1 на входе C. Запись информации в регистр памяти, построенный из статистических D - триггеров осуществляется так же, как и в одиночный статический.

Рисунок 1 Параллельный регистр

Запись и считывание информации происходит за один такт.

В некоторых регистрах памяти предусмотрена возможность высокоомного состояния выходов и установка выходов в нуль (сброс).

Регистры памяти применяют для промежуточного кратковременного хранения данных и для организации параллельного ввода-вывода в информационно-измерительных и вычислительных устройствах.

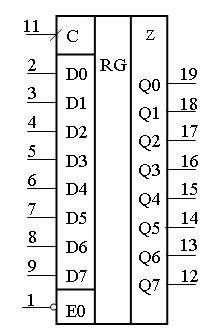

Примером параллельного регистра в интегральном исполнении может служить регистр 1533ИР37, УГО которого показано на рисунке 2.

Рисунок 2 Параллельный регистр 1533ИР37

Он представляет собой восьмиразрядный буферный регистр. Регистр построен на динамических D-триггерах, переключение производится положительным фронтом тактового импульса. Регистр имеет восемь входов данных D0 – D7 и восемь выходов Q0 – Q7. Когда на специальный вход подается низкий уровень, то после поступления положительного перепада на тактовый вход С входная информация появляется на выходах Q. Если на установлен высокий уровень, то выходные буферные каскады переводятся в высокоимпедансное состояние (состояние Z). При низком уровне тактового сигнала С триггеры регистра находятся в режиме хранения информации, зафиксированной при прохождении предыдущего положительного фронта импульса С.

3 Сдвиговые регистр

Регистром сдвига называется последовательностное функциональное устройство, состоящее из соединенных последовательно синхронных триггеров с общим синхронизирующим входом, и в этом устройстве происходит сдвиг записанной в него двоичной комбинации на один разряд при появлении активного перепада сигнала на синхронизирующем входе. Разрядность регистра равна числу используемых триггеров.

Регистры сдвига в интегральном исполнении создаются, в основном, из динамических D - триггеров и могут сдвигать записанную в них информацию в сторону старших разрядов (вправо), или в обе стороны. В последнем случае они называются реверсивными.У любого регистра сдвига обязательно есть вход последовательного ввода информации. У реверсивных регистров таких входов два: один для ввода информации при сдвиге вправо, другой - для ввода при сдвиге влево. Возможность последовательного вывода информации так же существует у любого регистра сдвига. Для этого у него имеется специальный выход последовательного вывода, а если предусмотрен параллельный вывод информации, то в качестве выхода для последовательного вывода используется выход последнего (старшего) разряда регистра.

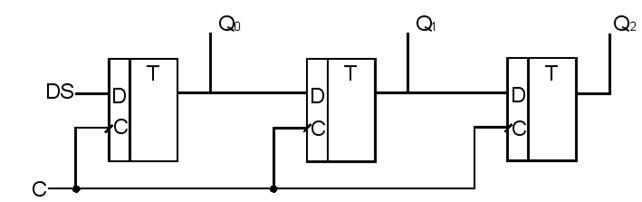

Схема трехразрядного регистра сдвига с последовательным вводом, параллельным выводом и сдвигом информации в сторону старших разрядов (вправо), построенная из D - триггеров показана на рисунке 3.

Рисунок 3 Регистр сдвига

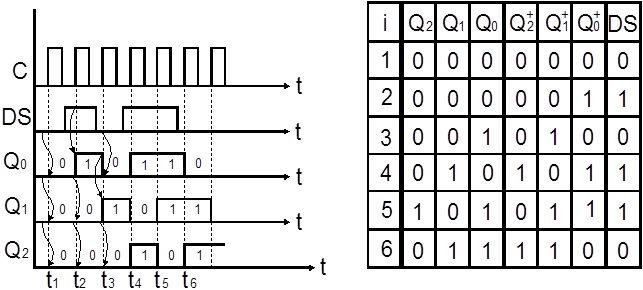

Работу схемы удобнее пояснять с помощью временной диаграммы, показанной на рисунке 4. При появлении активного перепада импульса на синхронизирующем входе C (в данном случае это перепад с 0 на 1) информация, находящаяся в этот момент на входе каждого триггера переписывается на его выход. Стрелки на рисунке 4 показывают, какая именно информация (0 или 1) переписывается.

Рисунок 4 Временная диаграмма Рисунок 5 Таблица переходов

Выход первого триггера считается младшим разрядом, а выход последнего триггера - старшим разрядом регистра.

Пускай перед началом работы на выходах всех триггеров и на входе DS находятся нули, т.е. в регистре записана комбинация 000. В момент на входах каждого триггера находился нуль, поэтому он и перепишется на выходы всех триггеров. Комбинация в регистре после - 000. В момент (когда но входе С появился перепад с 0 на 1) на входе DS находилась единица, а на выходах остальных триггеров нули, поэтому в первый триггер запишется единица, а во второй и третий нули. Комбинация в регистре после - 001. В момент на входе DS и на входе третьего триггера находились нули, а на входе второго -единица, поэтому в первый и третий триггер запишутся нули, а во второй - единица. Комбинация в регистре после - 010 и т.д. Информацию на входе DS необходимо установить до появления активного перепада на входе C.

Работу регистра сдвига можно пояснить и с помощью таблицы состояний (функций перехода), приведенной на рисунке 5. Каждая строка таблицы соответствует состоянию выходов регистра до появления активного перепада (столбцы . ) и после его появления (столбцы . ). В столбце DS обозначен уровень сигнала на входе DS перед самым появлением активного перепада, а в столбце - номер импульса, который вызвал состояние . .

Временная диаграмма и таблица состояния наглядно демонстрирует движение информации в регистре сдвига.

Для расширения функциональных возможностей у регистра сдвига может предусматриваться параллельный ввод информации, переключение в высокоомное состояние выходов, установка в нулевое состояние и др.

Регистр сдвига можно использовать и как регистр памяти. Только в этом случае для ввода информации через последовательный вход требуется число тактов равное разрядности регистра, а не один, как у регистров памяти.

Примером универсального регистра может служить микросхема К155ИР13 (рисунок 6). Режим ее работы задается уровнями сигналов на входах SR и SL (см. таблицу состояний регистра). При сдвиге вправо сигнал со входа DR переписывается в младший разряд DO0 по фронту каждого тактового импульса, а старая информация выхода DO7 теряется. При сдвиге влево информация с входа DL записывается на выход DO7, а информация с выхода DO0 теряется. При SL = SR = 1 микросхема работает как параллельный регистр, запись информации в который с входов DIпроисходит по фронту тактового импульса. При подаче 0 на вход все триггеры регистра сбрасываются в нулевое состояние.

Регистр предназначен для хранения многоразрядных двоичных чисел (слов). Поэтому его основу составляют запоминающие эле-менты – триггеры. В каждом из них хранится цифра разряда числа.

Кроме хранения, регистр может осуществлять сдвиг принятого слова, преобразование параллельного кода в последовательный и наоборот, преобразование кода из прямого в обратный (когда единицы заменяются нулями, а нули – единицами) и наоборот, и не-которые арифметические и логические операции.

В соответствии со способом ввода и вывода разрядов числа различают регистры параллельные, последовательные и комбиниро-ванные.

В параллельном регистре (регистре памяти) ввод и вывод слова осуществляется в параллельной форме – одновременно всех раз-рядов, в последовательном (сдвиговом) регистре разряды числа вводятся и выводятся последовательно, в комбинированном реги-стре ввод числа осуществляется в параллельной форме, а вывод в последовательной или наоборот.

Изучив материал этого модуля, студент сможет разрабатывать схемы уст- ройств, правильно выбирая регистры в соответствии с их назначением и конкрет-ными требованиями.

Параллельный регистр

Рис. 8.2,а Рис. 8.2,б

На рис.8.2,а приведена функциональная схема па-раллельного регистра (регистра памяти) на RS-триггерах при однофазном способе приема числа xn ….x2, x1.

Так как сигналы, поступающие только на входы S, не могут установить соответствующие триггеры в состояния 0 (из-за чего число будет записано с ошибкой), то перед приемом числа все триггеры ре-гистра обнуляются. Для этого на линию “0” подает-ся логическая 1. Подготовка к приему новой ин-формации составляет первый такт.

Во втором такте по сигналу 1 на линии “П” (“Прием”) двоичное число всеми разрядами одновременно (параллельно) через конъюнкторы запи- сывается в разряды регистра. Выдача числа в прямом коде осуществля-ется по сигналу лог. 1 на линии Впр, а в обратном – по сигналу лог.1 на линии Вобр.

Ввод информации в рассматриваемом регистре может осуществлять-ся и парафазным способом, когда i-ый разряд числа на вход S поступает непосредственно, а на R-вход – через инвертор. Этим исключается необходимость предварительной установки триггеров в 0, так как теперь его состояние целиком определяется сигналами на S- и R-входах, т. е. цифрой в разряде кода. Такая запись числа осуще-ствляется в один такт и производится намного быстрее, чем двухтактная.

Параллельный регистр может быть реализован и на других типах триггеров, имеющих информационные входы.

Условное изображение параллельного четырехразрядного регистра приведено на рис.8.2,б, где Q1. Q4 – выходы разрядов реги-стра, D1. D4 – входы, с которых в регистр одновременно записываются все разряды заносимого слова при поступлении импульса разрешения на С-вход

Последовательный регистр

В последовательных регистрах число вводится и выво-дится последовательно разряд за разрядом. Разряды такого регистра соединены последовательно. Каждый разряд вы-дает информацию в следующий и одновременно принимает новую информацию из предыдущего. Для этого каждый разряд должен иметь два запоминающих элемента. В пер-вый передается информация из предыдущего разряда, од-новременно второй запоминающий элемент передает свою информацию в последующий разряд; затем информация, принятая первым запоминающим элементом, передается во второй, а первый освобождается для приема новой информации.

Двухступенчатый триггер (например, JK-триггер, D-триггер) представляет совокупность двух запоминающих элементов, поэтому он один может составлять разряд последовательного регистра.

Если в цепи таких триггеров выходы одного триггера соединить с входами другого, то по фронту тактового импульса во входную ступень каждого триггера будет заноситься информация из выходной ступени предыдущего триггера, а по спаду импульса она

будет переписываться в выходную ступень. Теперь (по фронту следующего тактового импульса) во входной ступени триггера ин-формация может быть заменена новой (из предыдущего триггера) без опасения, что предыдущая будет потеряна.

Функциональная схема последовательного регистра приведена на рис.8.3, где, к примеру, левый триггер предназначен для хране-ния старшего разряда числа, а правый – для хранения младшего разряда. Разряды двоичного числа (высокие и низкие потенциалы), начиная с его младшего разряда, последовательно поступают на входы старшего разряда регистра. Поступление разрядов числа че-редуется с поступлением импульсов сдвига, которыми вводимые разряды продвигаются вдоль регистра, пока младший разряд n-разрядного числа не окажется в младшем разряде регистра.

Для выдачи записанного числа в последовательной форме надо на входы старшего разряда регистра подать хi=0, xi=1, а на ли-нию импульсов сдвига – n импульсов. Первый импульс выдвинет из младшего разряда регистра младший разряд числа, на его ме-сто передвинется второй разряд числа и т. д. – все число сдвинется вдоль регистра на один разряд. Одновременно с входов в стар-ший разряд регистра будет записан 0. Второй импульс сдвига выдвинет из регистра второй разряд числа и продвинет 0 из старшего разряда регистра в соседний, более младший и т.д. После n импульсов сдвига число будет полностью выведено из регистра, в раз-ряды которого окажутся записанными нули. В соответствии с механизмом перемещения разрядов числа вдоль регистра последова-тельный регистр называют сдвигающим (сдвиговым). Он может быть однонаправленным (для сдвига числа в сторону младшего разряда – правый сдвиг, в сторону старшего разряда – левый сдвиг), а также реверсивным, обеспечивающим сдвиг в обе стороны.

Схема реверсивного сдвигового регистра изображена на рис.8.4. При V=1 верхний ряд конъюнкторов заблокирован и в регистр сдвиговыми импульсами могут вдвигаться разряды слова слева направо с входа D1. При V=0 блокируется нижний ряд конъюнкто-ров и слово может вдвигаться в регистр с входа D2 справа налево.

Параллельно-последовательный регистр

Параллельно-последовательные регистры используются, в частности, для преобразования параллельной формы кода в последова-тельную и наоборот. Для решения первой задачи регистр, выполненный по схеме рис. 8.3, должен иметь триггеры с нетакти-руемыми входами S и R для записи слова в параллельном коде. С подачей импульсов сдвига этот код разряд за разрядом будет по-являться на выходе триггера младшего разряда. При решении второй задачи число вводится в регистр последовательно разряд за разрядом, а снимается одновременно с выходов всех триггеров.

Если выходы последнего триггера (см. рис. 8.3) соединить с входами первого, то получится кольцевой регистр сдвига. Записан-ная в его разряды информация под воздействием сдвигающих импульсов будет циркулировать по замкнутому кольцу. Кольцевой регистр иначе называют кольцевым счетчиком. Его коэффициент пересчета равен числу разрядов n: единица, записанная в один из разрядов, периодически появляется в нем после того, как пройдут n сдвигающих импульсов.

Приведем еще одно применение регистра. Пусть в регистр (см., например, рис. 8.3) записано число так, что его крайние разряды свободны от разрядов числа. При этом сдвиг числа влево (в сторону старших разрядов) увеличивает число вдвое, а сдвиг вправо уменьшает число в два раза. Это легко проследить на примере. Число 00111002 = 2810. При сдвиге влево оно будет равно 01110002=5610, а при сдвиге вправо составит 00011102 =1410.

Промышленность выпускает многие типы регистров в интегральном исполнении.

На рис. 8.4 приведено условное изображение 4-х разрядного параллельно-последовательного регистра со сдвигом вправо. Выбор режима (последовательный или параллельный ввод числа) определяется сигналом на входе V2: при логическом 0 регистр работает как сдвигающий, а при логической 1 - как параллельный. Через вход VI в первый разряд регистра последовательно вводятся разряды двоичного числа. Синхроимпульсы, пос-тупающие на вход С1, обеспечивают их сдвиг. По входам D1. D4 в регистр может быть занесено двоичное число в параллельной форме всеми разрядами одновременно. Его запись происходит с поступлением синхро-импульса на вход С2.

В условных обозначениях регистров со сдвигом влево стрелка обращена в сторону, противоположную изображенной на рис. 8.4, а в реверсив-ных сдвигающих регистрах она показы-вается двунаправленной.

На рис. 8.5 показано наращивание раз-рядов последовательно-параллельного регистра (с последовательным вводом и параллельным выводом числа). По каж-дому импульсу на входе С разряды вво-димого слова с входа D вдвигаются в ре-гистр. С выхода последнего разряда (Q4) предыдущего регистра разряд слова по-ступает на вход D последующего регист-ра, составляющих как бы непрерывную цепочку последовательно включенных триггеров.

Заключение по теме модуля "Регистры"

По способу занесения числа регистры разделяются на параллельные (регистры памяти), последовательные (сдвиговые регистры) и параллельно- последовательные (комбинированные).

Кроме хранения числа, последовательные и параллельно-последовательные регистры могут осуществлять сдвиг чисел, что соот-ветствует их умножению или делению.

На параллельно-последовательных регистрах осуществляют преобразование параллельного кода в последовательный и наоборот.

Регистр предназначен для хранения многоразрядных двоичных чисел (слов). Поэтому его основу составляют запоминающие эле-менты – триггеры. В каждом из них хранится цифра разряда числа.

Кроме хранения, регистр может осуществлять сдвиг принятого слова, преобразование параллельного кода в последовательный и наоборот, преобразование кода из прямого в обратный (когда единицызаменяются нулями, а нули – единицами) и наоборот, и не-которые арифметические и логические операции.

В соответствии со способом ввода и вывода разрядов числа различают регистры параллельные, последовательные и комбиниро-ванные.

В параллельном регистре (регистре памяти) ввод и вывод слова осуществляется в параллельной форме – одновременно всех раз-рядов, в последовательном (сдвиговом) регистре разрядычисла вводятся и выводятся последовательно, в комбинированном реги-стре ввод числа осуществляется в параллельной форме, а вывод в последовательной или наоборот.

Изучив материал этого модуля, студент сможет разрабатывать схемы уст-ройств, правильно выбирая регистры в соответствии с их назначением и конкрет-ными требованиями.

Блок 8.2. Параллельный регистр

На приведенафункциональная схема па-раллельного регистра (регистра памяти) на RS-триггерах при однофазном способе приема числа xn ….x2, x1.

Так как сигналы, поступающие только на входы S, не могут установить соответствующие триггеры в состояния 0 (из-за чего число будет записано с ошибкой), то перед приемом числа все триггеры ре-гистра обнуляются. Для этого на линию “0” подает-ся логическая 1. Подготовка к приему новой ин-формациисоставляет первый такт.

Во втором такте по сигналу 1 на линии “П” (“Прием”) двоичное число всеми разрядами одновременно (параллельно) через конъюнкторы запи-сывается в разряды регистра. Выдача числа в прямом коде осуществля-ется по сигналу лог. 1 на линии Впр, а в обратном – по сигналу лог.1 на линии Вобр.

Ввод информации в рассматриваемом регистре может осуществлять-ся и парафазнымспособом, когда i-ый разряд числа на вход S поступает непосредственно, а на R-вход – через инвертор. Этим исключается необходимость предварительной установки триггеров в 0, так как теперь его состояние целиком определяется сигналами на S- и R-входах, т. е. цифрой в разряде кода. Такая запись числа осуще-ствляется в один такт и производится намного быстрее, чем двухтактная.

Параллельный регистр может бытьреализован и на других типах триггеров, имеющих информационные входы.

Условное изображение параллельного четырехразрядного регистра приведено на рис.8.2,б, где Q1. Q4 – выходы разрядов реги-стра, D1. D4 – входы, с которых в регистр одновременно записываются все разряды заносимого слова при поступлении импульса разрешения на С-вход

Блок 8.3. Последовательный регистр

В последовательныхрегистрах число вводится и выво-дится последовательно разряд за разрядом. Разряды такого регистра соединены последовательно. Каждый разряд вы-дает информацию в следующий и одновременно принимает новую информацию из предыдущего. Для этого каждый разряд должен иметь два запоминающих элемента. В пер-вый передается информация из предыдущего разряда, од-новременно второй запоминающий элемент передает свою информациюв последующий разряд; затем информация, принятая первым запоминающим элементом, передается во второй, а первый освобождается для приема новой инфор-мации.

Двухступенчатый триггер (например, JK-триггер, D-триггер) представляет совокупность двух запоминающих элементов, поэтому он один может составлять разряд последовательного регистра.

Регистры с параллельным приемом и выдачей информации. Количество разрядов записываемой цифровой информации. Разрядность регистров сдвига, памяти и хранения. Синхроимпульсы для последовательного считывания. Реализация межрегистровых связей по общей шине.

| Рубрика | Программирование, компьютеры и кибернетика |

| Вид | лекция |

| Язык | русский |

| Дата добавления | 23.07.2013 |

| Размер файла | 119,3 K |

Студенты, аспиранты, молодые ученые, использующие базу знаний в своей учебе и работе, будут вам очень благодарны.

Наиболее распространенным узлом цифровой техники и устройств автоматики являются регистры. Регистром называют последовательное устройство, предназначенное для хранения небольшого объёма цифровой информации (числа) или ее преобразования. Регистр представляет собой упорядоченную последовательность триггеров, число которых соответствует числу разрядов в слове. Процедура ввода числа в регистр называется записью. Процедура вывода числа называется считыванием. По способу записи и считывания различают следующие типы регистров: 1. Параллельный регистр, в котором и запись, и считывание производят в параллельном коде, т.е. во все разряды одновременно записывается число и одновременно со всех разрядов считывается. 2. Последовательный регистр, в котором и запись, и считывание производятся в последовательном коде, т.е. последовательно разряд за разрядом. 3. Параллельно - последовательный регистр, в котором запись производится в параллельном коде, а считывание в последовательном. 4. Последовательно - параллельный регистр, в котором запись производится в последовательном коде, а считывание в параллельном.

Рассмотрим примеры построения схем перечисленных типов регистров.

Регистры с параллельным приемом и выдачей информации служат для хранения информации и называются регистрами памяти или хранения. . Количество разрядов записываемой цифровой информации определяется разрядностью регистра, а разрядность регистра, в свою очередь, определяется количеством триггеров, образующих этот регистр. В качестве разрядных триггеров регистра памяти используются синхронизируемые уровнем или фронтом триггеры. Регистры памяти могут быть реализованы на D-триггерах, если информация поступает на входы регистра в виде однофазных сигналов и на RS-триггерах, если информация поступает в виде парафазных сигналов. В некоторых случаях регистры могут иметь вход для установки выходов в состояние “0”. Этот асинхронный вход называют входом R “сброса” триггеров регистра. Параллельный регистр на D-триггерах приведен на рис.13.1.

Регистры с последовательным приемом или выдачей информации называются сдвиговыми регистрами или регистрами сдвига. Регистры сдвига могут выполнять функции хранения и преобразования информации. Они могут быть использованы для построения умножителей и делителей чисел двоичной системы счисления, т.к. сдвиг двоичного числа влево на один разряд соответствует умножению его на два, а сдвиг вправо - делению на два. Регистры сдвига широко используются для выполнения различных временных преобразований цифровой информации: последовательное накопление последовательной цифровой информации с последующей одновременной выдачей (преобразование последовательной цифровой информации в параллельный код) или одновременный прием (параллельный прием) информации с последующей последовательной выдачей (преобразование параллельного кода в последовательный). Регистры сдвига могут служить также в качестве элементов задержки сигнала, представленного в цифровой форме. Действительно, регистры с последовательным приемом (вводом) и выводом осуществляют задержку передачи информации на m+1 тактов ( m+1 - число разрядов регистра) машинного времени.

Регистры сдвига обычно реализуются на D-триггерах или на RS-триггерах. Следует отметить, что все регистры сдвига строятся на базе триггеров, синхронизируемых фронтом синхроимпульса. Разрядность регистров сдвига, как и у регистров хранения, определяется количеством триггеров, входящих в их состав.

Первым тактовым импульсом первая единица старшего разряда числа 101 записывается в первый триггер. Вторым тактовым импульсом в первый триггер записывается значение следующего разряда (в нашем примере 0), а во второй триггер записывается единица, которая была перед приходом второго тактового импульса на выходе первого триггера.

Таким образом, каждым тактовым импульсом в регистре происходит сдвиг числа на один разряд. Трехразрядное число будет полностью записано в регистр после третьего тактового импульса. При этом на выходе регистра можно просчитать значения разряда, который был записан первым. Для считывания значений следующих двух разрядов нужно подать ещё два тактового импульса. В двоичной системе счисления при сдвиге числа на один разряд в сторону старших разрядов происходит увеличения числа в два раза. При сдвиге числа в сторону младших разрядов число, записываемое в регистр, уменьшается в два раза. Таким образом, сдвигающий регистр можно использовать для умножения или деления числа на 2n , где n - количество сдвигов равное количеству тактовых импульсов.

регистр информация хранение память

Параллельно - последовательный регистр

В параллельно - последовательном регистре запись информации происходит в параллельном коде, а считывание в последовательном. На рис 13.3 показан пример построения такого регистра на JK - триггерах.

В приведенной схеме JK - триггеры дважды превращены в D - триггеры. Одно превращение осуществлено для организации записи с использованием вспомогательных инверсных входов S и R и, добавлением двух элементов И -НЕ. Этот способ построения триггера рассмотрен на предыдущей лекции.

Разрешение на параллельный ввод (запись по S-входам)

Последовательно - параллельный регистр

Для построения последовательно - параллельного регистра достаточно в последовательном регистре организовать параллельное считывание используя дополнительные элементы И - НЕ, как это показано на рис 13.4.

При последовательном выводе информация не сохраняется в регистре, а сдвигается поразрядно на выход. В некоторых случаях бывает необходимо сохранить информацию. Для этого регистр дополняют цепью обратной связи. Одним из наиболее распространенных устройств содержащих регистр с обратной связью является кольцевой счетчик, принципиальная схема которого приведена на рис.13.5. Информация в устройство записывается последовательным образом по входу DS, а управляется процесс записи входом V.

Управляющий вход V своим высоким уровнем запирает ЛЭ2 и исключает из работы схемы обратную связь, но разрешает ввод информации по входу DS. После записи двоичного кода, вход V переводится в низкий уровень. Записанный трехразрядный код при каждом поступлении синхроимпульса (вход С) будет не только считываться, но и порязрядно поступать на вход регистра. Запись новой информации по входу DS будет возможна только при подаче единицы на вход V.

Изученные ранее схемы обеспечивают какой-либо один вид ввода информации.

Схема, представленная на рис.13.6, позволяет осуществлять как последовательный, так и параллельный ввод. Режим ввода определяется уровнем сигнала на входе S/P. Если на входе S/P единица, то на входы тройки верхних и нижних ЛЭ И-НЕ на рис.13.6 поступают нули, что закрывает их, а на R,S-входы триггеров - единицы, что переводит регистры в синхронный режим работы. Синхроимпульсы на входе С (на входе S/P единица) разрешают запись информации со входа DS, а также ее поразрядный сдвиг вправо.

Если на вход S/P подать ноль, то тактирование триггеров становится невозможным, а сами триггеры превращаются в D-триггеры с информационными входами D1, D2, D3. Становиться возможным параллельная запись информации в регистр. Для последовательного считывания необходимо снова подать на управляющий вход S/P единицу.

ОРГАНИЗАЦИЯ МЕЖРЕГИСТОРВЫХ СВЯЗЕЙ

Информация, хранящаяся в регистре, подлежит дальнейшей обработке, для чего она должна передаваться от одного регистра другому. Передача осуществляется различными способами. При небольшом количестве регистров в ЛУ реализуется пространственное разделение цепей связи, при котором обмен информацией может осуществляться одновременно. С увеличением числа регистров резко возрастает количество линий связи. В таких случаях реализуют временное разделение сигналов, при котором для обмена используется единственная линия связи - общая шина. В определенный момент времени возможен обмен информацией только между двумя регистрами, а путь передачи сигнала определяется значениями управляющих сигналов.

Рис.13.7 Реализация межрегистровых связей по общей шине

Подобные документы

реферат [579,6 K], добавлен 17.07.2008

Характеристика регистров памяти как устройств временного хранения данных. Различия между прерываниями и исключениями команд, их обработка. Вычисление производительности ЭВМ. Программа с использованием отложенного запуска команд. Виды компьютерных сетей.

контрольная работа [24,9 K], добавлен 09.11.2010

Схема и программное обеспечение модуля генератора последовательностей на шине ISA IBM PС AT. Операция "Запись в 16-и разрядное устройство ввода-вывода". Использование триггера для хранения информации в селекторе адреса. Увеличения разрядности счетчика.

контрольная работа [363,3 K], добавлен 05.01.2013

Способы передачи и хранения информации наиболее надежными и экономными методами. Связь между вероятностью и информацией. Понятие меры количества информации. Энтропия и ее свойства. Формула для вычисления энтропии. Среднее количество информации.

реферат [99,7 K], добавлен 19.08.2015

Модель целочисленного MMX-расширения и особенности работы сопроцессора. Отображение ММХ-регистров на регистры стека сопроцессора. Система команд MMX: команды пересылки, сложения и вычитания, сравнения, логических операций, сдвига, упаковки и распаковки.

Читайте также: