Характеристика шины pci кратко

Обновлено: 05.07.2024

PCI (Peripheral Component Interconnect) (Межсетевое соединение периферийных компонентов) - это аппаратная шина, используемая для добавления внутренних компонентов в компьютер. Например, плата PCI может быть вставлена в слот PCI на материнской плате, обеспечивая дополнительные порты ввода-вывода на задней панели компьютера.

PCI и PCI-X были заменены PCI Express, который был представлен в 2004 году. [Источник 1]

Содержание

История

Корпорация Intel начала работу над интерфейсом периферийных компонентов или PCI в 1990 году. 22 июня 1992 года PCI 1.0 был представлен в компьютерном мире. PCI 1.0 был только спецификацией на уровне компонентов. PCI 2.0, выпущенный в следующем году, был первым, кто установил стандарты для разъема и разъема материнской платы. PCI был реализован на серверах, и в итоге он заменил MCA и EISA и стал шиной расширения сервера.

Тем не менее, PCI потребовалось некоторое время, чтобы заменить VESA Local Bus, широко известную как VLB; также потребовалось некоторое время, чтобы стать базовым стандартом шины ввода-вывода на компьютерах второго поколения Pentium. К 1996 году VESA Local Bus перестал существовать, и PCI был принят почти всеми производителями даже на 486 компьютерах. Но EISA пережила немного дольше, до 2000 года. PCI был также принят Apple Computer для своих профессиональных компьютеров Power Macintosh в середине 1995 года. Потребительская линейка продуктов Performa также приняла PCI в середине 1996 года, заменив LC PDS.

PCI добавила несколько новых функций и улучшений производительности в своих последних версиях. Это включает в себя 66 МГц 3,3 В и 133 МГц PCI-X. Другим улучшением является адаптация сигнализации PCI к другим форм-факторам. Последовательный стандарт PCI Express, представленный в 2004 году, является последним выпуском на компьютерном рынке и получил хорошие результаты. [Источник 2]

Принцип работы

Рисунок 1 - Aрхитектура PC с шиной PCI

Шина обладает процессоро-независимостью (в отличие от VLbus) и может работать параллельно с шиной процессора, не обращаясь к ней за запросами. Например, процессор работает с кэшем или системной памятью, а в это время по сети на ЖД производится запись информации, тем самым загрузка шины процессора значительно снижается. Кроме того, стандарт шины был объявлен открытым и передан PCI Special Interest Group, которая продолжила работу по совершенствованию шины (в настоящее время доступен R2.1).

Основные возможности

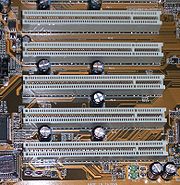

Рисунок 2 - Разъемы

Синхронный 32-х или 64-х разрядный обмен данными (однако 64-разрядная шина в настоящее время используется только в Alpha-системах и серверах на базе процессоров Intel Xeon). При этом для уменьшения числа контактов (и стоимости) используется мультиплексирование, то есть адрес и данные передаются по одним и тем же линиям.

Поддержка 5V и 3.3V логики. Разъемы для 5 и 3.3V плат различаются расположением ключей.

Разъемы

Существуют и универсальные платы, поддерживающие оба напряжения. Заметим, что частота 66MHz поддерживается только 3.3V логикой. Частота работы шины 33MHz или 66MHz (в версии 2.1) позволяет обеспечить широкий диапазон пропускных способностей (с использованием пакетного режима):

- 132 МВ/сек при 32-bit/33MHz;

- 264 MB/сек при 32-bit/66MHz;

- 264 MB/сек при 64-bit/33MHz;

- 528 МВ/сек при 64-bit/66MHz.

При этом для работы шины на частоте 66MHz необходимо, чтобы все периферийные устройства работали на этой частоте.

Полная поддержка multiply bus master (например, несколько контроллеров жестких дисков могут одновременно работать на шине).

Поддержка write-back и write-through кэша.

Автоматическое конфигурирование карт расширения при включении питания.

Спецификация шины позволяет комбинировать до восьми функций на одной карте (например, видео + звук и т.д.).

Шина позволяет устанавливать до 4 слотов расширения, однако возможно использование моста PCI-PCI для увеличения количества карт расширения.

PCI-устройства оборудованы таймером, который используется для определения максимального промежутка времени, в течении которого устройство может занимать шину.

При разработке шины в ее архитектуру были заложены передовые технические решения, позволяющие повысить пропускную способность.

Шина поддерживает метод передачи данных, называемый "linear burst" (метод линейных пакетов). Этот метод предполагает, что пакет информации считывается (или записывается) "одним куском", то есть адрес автоматически увеличивается для следующего байта. Естественным образом при этом увеличивается скорость передачи собственно данных за счет уменьшения числа передаваемых адресов.

Шина PCI является той черепахой, на которой стоят слоны, поддерживающие "Землю" — архитектуру Microsoft/Intel Plug and Play (PnP) PC architecture. Спецификация шины PCI определяет три типа ресурсов: два обычных (диапазон памяти и диапазон ввода/вывода, как их называет компания Microsoft) и configuration space — "конфигурационное пространство".

Рисунок 3 - Конфигурационное пространство

Конфигурационное пространство состоит из трех регионов(см. рис. 3):

- заголовка, независимого от устройства (device-independent header region);

- региона, определяемого типом устройства (header-type region);

- региона, определяемого пользователем (user-defined region).

В заголовке содержится информация о производителе и типе устройства — поле Class Code (сетевой адаптер, контроллер диска, мультимедиа и т.д.) и прочая служебная информация.

Следующий регион содержит регистры диапазонов памяти и ввода/вывода, которые позволяют динамически выделять устройству область системной памяти и адресного пространства. В зависимости от реализации системы конфигурация устройств производится либо BIOS (при выполнении POST — power-on self test), либо программно. Базовый регистр expansion ROM аналогично позволяет отображать ROM устройства в системную память. Поле CIS (Card Information Structure) pointer используется картами cardbus (PCMCIA R3.0). С Subsystem vendor/Subsystem ID все понятно, а последние 4 байта региона используются для определения прерывания и времени запроса/владения. [Источник 3]

Архитектура

Адресные пространства

ЦП и устройства PCI должны иметь доступ к памяти, которая совместно используется между ними. Эта память используется драйверами устройств для управления устройствами PCI и для передачи информации между ними. Обычно разделяемая память содержит регистры управления и состояния для устройства. Эти регистры используются для управления устройством и считывания его состояния. Например, драйвер устройства PCI SCSI должен был прочитать свой регистр состояния, чтобы узнать, было ли устройство SCSI готово записать блок данных на диск SCSI. Или он может записать в регистр управления, чтобы запустить устройство после его включения.

Системная память ЦП может использоваться для этой общей памяти, но если это так, то каждый раз, когда устройство PCI получает доступ к памяти, CPU должен останавливаться, ожидая завершения работы устройства PCI. Доступ к памяти обычно ограничен одним системным компонентом за раз. Это замедлит работу системы. Также не рекомендуется позволять периферийным устройствам системы получать доступ к основной памяти неконтролируемым образом. Это было бы очень опасно; устройство-изгои может сделать систему очень неустойчивой.

Периферийные устройства имеют свои собственные пространства памяти. ЦП может получить доступ к этим пространствам, но доступ к устройствам в память системы очень строго контролируется с использованием каналов DMA (прямой доступ к памяти). У устройств ISA есть доступ к двум адресным пространствам, ISA I / O (вход / выход) и ISA-памяти. PCI имеет три; PCI I / O, PCI Memory и PCI Configuration.

Процессор Alpha AXP не имеет естественного доступа к адресным пространствам, отличным от адресного пространства системы. Он использует чипсеты поддержки для доступа к другим адресным пространствам, таким как пространство конфигурации PCI. Он использует схему разреженного адреса, которая крадет часть большого виртуального адресного пространства и сопоставляет ее с адресными пространствами PCI.

Структура передаваемой информации

Каждое PCI-устройство в системе, включая мосты PCI-PCI, имеет структуру данных конфигурации, которая находится где-то в адресном пространстве конфигурации PCI. Заголовок конфигурации PCI позволяет системе идентифицировать и управлять устройством. Точно там, где заголовок находится в адресном пространстве конфигурации PCI, зависит от того, где в топологии PCI это устройство. Например, видеокарта PCI, подключенная к одному слоту PCI на материнской плате ПК, будет иметь свой заголовок конфигурации в одном месте, и если он подключен к другому слоту PCI, его заголовок появится в другом месте в конфигурационной памяти PCI. Это не имеет значения, поскольку везде, где находятся устройства и мосты PCI, система найдет и настроит их, используя регистры состояния и конфигурации в своих конфигурационных заголовках.

| Идентификация поставщика | Уникальный номер, описывающий создателя устройства PCI. Цифровая идентификация поставщика PCI - 0x1011, а у Intel - 0x8086. |

| Идентификация устройства | Уникальный номер, описывающий само устройство. Например, устройство быстрого доступа Ethernet 21141 Digital имеет идентификатор устройства 0x0009. |

| Статус | Это поле дает статус устройства со значением бит этого поля, установленным стандартом. |

| Команда | При записи в это поле система управляет устройством, например, позволяя устройству получать доступ к памяти PCI I/O |

| Код класса | Это определяет тип устройства, которым это является. Существуют стандартные классы для всех типов устройств; видео, SCSI и т. д. Код класса для SCSI равен 0x0100. |

| Регистры базового адреса | Эти регистры используются для определения и распределения типа, количества и местоположения PCI I/O и памяти PCI, которые устройство может использовать. |

| Вывод прерывания | Четыре физических контакта на плате PCI несут прерывания от платы до шины PCI. Стандартные метки обозначают их как A, B, C и D. Поле Pin прерывания описывает, какой из этих контактов этот PCI-устройство использует. Как правило, он предназначен для устройства с парификатором. То есть, каждый раз, когда система загружается, устройство использует один и тот же вывод прерывания. Эта информация позволяет подсистеме обработки прерываний управлять прерываниями с этого устройства. |

| Линия прерывания | Поле Interrupt Line заголовка PCI Configuration устройства используется для передачи дескриптора прерывания между кодом инициализации PCI, драйвером устройства и подсистемой обработки прерываний операционной системы. Число, написанное там, не имеет смысла для драйвера устройства, но позволяет обработчику прерываний правильно маршрутизировать прерывание с устройства PCI на правильный код обработки прерываний драйвера устройства в операционной системе. |

Инициализация

Код инициализации PCI можно разбить на три логические части:

- Драйвер устройства PCI. Этот драйвер псевдо-устройства выполняет поиск в системе PCI, начиная с шины 0, и находит все устройства PCI и мосты в системе. Он создает связанный список структур данных, описывающих топологию системы. Кроме того, он отображает все найденные мосты.

- PCI BIOS. Это программный уровень, который должен предоставлять различные услуги, необходимые для pci. Это снова зависит от операционной системы и отличается от всех остальных

- PCI Fixup. Код исправления, специфичный для системы, отображает системные специфические свободные окончания инициализации PCI.

Драйвер устройства PCI

Драйвер устройства PCI на самом деле не является драйвером устройства, а функцией операционной системы, вызываемой при инициализации системы. Код инициализации PCI должен сканировать все шины PCI в системе, которые ищут все устройства PCI в системе (включая мостовые устройства PCI-PCI).

Он использует код PCI BIOS, чтобы выяснить, занят ли каждый слот в текущей шине PCI, которую он сканирует. Если слот PCI занят, он создает структуру данных pci_dev, описывающую устройство, и ссылки в список известных устройств PCI (на которые указывают pci_devices).

Код инициализации PCI начинается с сканирования PCI-шины 0. Он пытается прочитать поля идентификации идентификации и идентификации устройства для каждого возможного устройства PCI в каждом возможном слоте PCI. Когда он находит занятый слот, он создает структуру данных pci_dev, описывающую устройство. Все структуры данных pci_dev, созданные кодом инициализации PCI (включая все PCI-PCI Bridges), связаны в односвязный список; pci_devices.

Если PCI-устройство, которое было найдено, было мостом PCI-PCI, то структура данных pci_bus построена и связана с деревом структур данных pci_bus и pci_dev, на которые указывает pci_root. Код инициализации PCI может определить, является ли PCI-устройство PCI-PCI Bridge, поскольку он имеет код класса 0x060400. Затем ядро конфигурирует PCI-шину на другой (ниже по потоку) стороне PCI-PCI Bridge, которую он только что нашел. Если будет найдено больше PCI-PCI Bridges, они также будут настроены. Этот процесс известен как алгоритм глубины; топология PCI системы полностью отображается в глубину перед поиском по ширине. Когда операционная система ищет шины PCI по нисходящей линии связи, она также должна настраивать промежуточные и подчиненные шины шины PCI-PCI. [Источник 4]

Итак, переходим к самому интересному. Что же находится на сегодняшний день внутри большинства наших компьютеров? Естественно, шина PCI. Другой вопрос, почему именно эта шина. Попробуем разобраться.

Итак, разработка шины PCI началась весной 1991 года как внутренний проект корпорации Intel (Release 0.1). Специалисты компании поставили перед собой цель разработать недорогое решение, которое бы позволило полностью реализовать возможности нового поколения процессоров 486/Pentium/P6 (вот уже половина ответа). Особенно подчеркивалось, что разработка проводилась "с нуля", а не была попыткой установки новых "заплат" на существующие решения. В результате шина PCI появилась в июне 1992 года (R1.0). Разработчики Intel отказались от использования шины процессора и ввели еще одну "антресольную" (mezzanine) шину.

Благодаря такому решению шина получилась, во-первых, процессоро-независимой (в отличие от VLbus), а во-вторых, могла работать параллельно с шиной процессора, не обращаясь к ней за запросами. Например, процессор работает себе с кэшем или системной памятью, а в это время по сети на винчестер пишется информация. Просто здорово! На самом деле идиллии, конечно, не получается, но загрузка шины процессора снижается здорово. Кроме того, стандарт шины был объявлен открытым и передан PCI Special Interest Group, которая продолжила работу по совершенствованию шины (в настоящее время доступен R2.1), и в этом, пожалуй, вторая половина ответа на вопрос "почему PCI?"

- Синхронный 32-х или 64-х разрядный обмен данными (правда, насколько мне известно, 64-разрядная шина в настоящее время используется только в Alpha-системах и серверах на базе процессоров Intel Xeon, но, в принципе, за ней будущее). При этом для уменьшения числа контактов (и стоимости) используется мультиплексирование, то есть адрес и данные передаются по одним и тем же линиям.

- Поддержка 5V и 3.3V логики. Разъемы для 5 и 3.3V плат различаются расположением ключей

- 132 МВ/сек при 32-bit/33MHz;

- 264 MB/сек при 32-bit/66MHz;

- 264 MB/сек при 64-bit/33MHz;

- 528 МВ/сек при 64-bit/66MHz.

При разработке шины в ее архитектуру были заложены передовые технические решения, позволяющие повысить пропускную способность.

Шина поддерживает метод передачи данных, называемый "linear burst" (метод линейных пакетов). Этот метод предполагает, что пакет информации считывается (или записывается) "одним куском", то есть адрес автоматически увеличивается для следующего байта. Естественным образом при этом увеличивается скорость передачи собственно данных за счет уменьшения числа передаваемых адресов.

Шина PCI является той черепахой, на которой стоят слоны, поддерживающие "Землю" — архитектуру Microsoft/Intel Plug and Play (PnP) PC architecture. Спецификация шины PCI определяет три типа ресурсов: два обычных (диапазон памяти и диапазон ввода/вывода, как их называет компания Microsoft) и configuration space — "конфигурационное пространство".

- заголовка, независимого от устройства (device-independent header region);

- региона, определяемого типом устройства (header-type region);

- региона, определяемого пользователем (user-defined region).

В заголовке содержится информация о производителе и типе устройства — поле Class Code (сетевой адаптер, контроллер диска, мультимедиа и т.д.) и прочая служебная информация.

Следующий регион содержит регистры диапазонов памяти и ввода/вывода, которые позволяют динамически выделять устройству область системной памяти и адресного пространства. В зависимости от реализации системы конфигурация устройств производится либо BIOS (при выполнении POST — power-on self test), либо программно. Базовый регистр expansion ROM аналогично позволяет отображать ROM устройства в системную память. Поле CIS (Card Information Structure) pointer используется картами cardbus (PCMCIA R3.0). С Subsystem vendor/Subsystem ID все понятно, а последние 4 байта региона используются для определения прерывания и времени запроса/владения.

PCI (англ. Peripheral component interconnect , дословно — взаимосвязь периферийных компонентов) — шина ввода/вывода для подключения периферийных устройств к материнской плате компьютера.

Стандарт на шину PCI определяет:

- физические параметры (например, разъёмы и разводку сигнальных линий);

- электрические параметры (например, напряжения);

- логическую модель (например, типы циклов шины, адресацию на шине).

Развитием стандарта PCI занимается организация PCI Special Interest Group.

Содержание

История создания

Весной 1991 года компания 486, Pentium Pro. Кроме того, было необходимо учесть ошибки допущенные VLB (электрическая нагрузка не позволяла подключать более 3 плат расширения), а также реализовать автоконфигурирование устройств по примеру протокола Amiga.

В 1992 году появляется первая версия шины PCI, Intel объявляет, что стандарт шины будет открытым и создаёт PCI Special Interest Group. Благодаря этому, любой заинтересованный разработчик получает возможность создавать устройства для шины PCI без необходимости приобретения лицензии. Первая версия шины имела тактовую частоту 33 МГц, могла быть 32 или 64 битной, а устройства могли работать с сигналами в 5 В или 3,3 В. Теоретически, пропускная способность шины 133 Мбайт/с, однако в реальности пропускная способность составляла около 80 Мбайт/с.

В середине 1993 года компания Intel выходит из ассоциации VESA и начинает предпринимать активные шаги по продвижению шины PCI на рынке. Ответом на критику со стороны специалистов из конференций

В 1997 году, в связи с развитием компьютерной графики и разработкой шины видеокартам и перестала использоваться для установки видеокарт. Смысла приобретать PCI-видеокарту нет уже более 10 лет.

В настоящее время интерфейс PCI постепенно вытесняется интерфейсами PCI Express и 2008 год) устанавливается всего лишь 2-3 разъёма PCI вместо 5-6, устанавливавшихся ранее.

Основные сведения

Первоначально 32 проводника адрес/данные на частоте 33 МГц. Позже появились версии с 64 проводниками (используется дополнительная колодка разъема) и частотой 66 МГц.

Специальные типы транзакций используются для обращений к конфигурационному пространству устройства.

Богатая поддержка межшинных мостов. Богатая поддержка режимов кэширования, таких, как:

Конфигурирование

PCI-устройства с точки зрения пользователя самонастраиваемы (Plug and Play). После старта компьютера системное программное обеспечение обследует конфигурационное пространство PCI каждого устройства, подключённого к шине, и распределяет ресурсы.

Каждое устройство может затребовать до семи диапазонов в адресном пространстве памяти PCI или в адресном пространстве ввода-вывода PCI.

Кроме того, устройства могут иметь ПЗУ, содержащее исполняемый код для процессоров PA-RISC, Open Firmware (системное ПО компьютеров на базе PowerPC) или драйвер EFI.

Настройка прерываний осуществляется также системным программным обеспечением (в отличие от шины IRQ, поэтому имеется возможность работы нескольких устройств с одной линией запроса прерывания; обычно системное ПО пытается выделить каждому устройству отдельное прерывание для увеличения производительности.

Итак, переходим к самому интересному. Что же находится на сегодняшний день внутри большинства наших компьютеров? Естественно, шина PCI. Другой вопрос, почему именно эта шина. Попробуем разобраться.

Основные возможности шины следующие.

- Синхронный 32-х или 64-х разрядный обмен данными (правда, насколько мне известно, 64-разрядная шина в настоящее время используется только в Alpha-системах и серверах на базе процессоров Intel Xeon, но, в принципе, за ней будущее). При этом для уменьшения числа контактов (и стоимости) используется мультиплексирование, то есть адрес и данные передаются по одним и тем же линиям.

- Поддержка 5V и 3.3V логики. Разъемы для 5 и 3.3V плат различаются расположением ключей

- 132 МВ/сек при 32-bit/33MHz;

- 264 MB/сек при 32-bit/66MHz;

- 264 MB/сек при 64-bit/33MHz;

- 528 МВ/сек при 64-bit/66MHz.

При разработке шины в ее архитектуру были заложены передовые технические решения, позволяющие повысить пропускную способность.

Конфигурационное пространство состоит из трех регионов:

- заголовка, независимого от устройства (device-independent header region);

- региона, определяемого типом устройства (header-type region);

- региона, определяемого пользователем (user-defined region).

В заголовке содержится информация о производителе и типе устройства — поле Class Code (сетевой адаптер, контроллер диска, мультимедиа и т.д.) и прочая служебная информация.

Следующий регион содержит регистры диапазонов памяти и ввода/вывода, которые позволяют динамически выделять устройству область системной памяти и адресного пространства. В зависимости от реализации системы конфигурация устройств производится либо BIOS (при выполнении POST — power-on self test), либо программно. Базовый регистр expansion ROM аналогично позволяет отображать ROM устройства в системную память. Поле CIS (Card Information Structure) pointer используется картами cardbus (PCMCIA R3.0). С Subsystem vendor/Subsystem ID все понятно, а последние 4 байта региона используются для определения прерывания и времени запроса/владения.

Общая характеристика шины PCI

PCI (Peripheral Component Interconnect) local bus- шина соединения периферийных компонентов. Она разрабатывалась в расчете на шинный интерфейс процессоров Pentium. В архитектуре ЭВМ эта шина стала центральной, через которую процессор взаимодействует со всеми остальными шинами (см. рисунок 8.7). Первая версия стандарта шины PCI 1.0 появилась в 1992 г., PCI 2.1 — в 1995 г.

Шина PCI является синхронной шиной, в которой фиксация всех сигналов выполняется по нарастающему фронту сигнала синхронизации CLK (см. рисунок 8.4.3). Номинальное значение частоты синхронизации CLK равно 33 МГц. Начиная с версии 2.1 допускается повышение частоты CLK до 66 МГц.

Шина PCI относится к мультиплексированным шинам, в которой для передачи адреса и данных (последовательно во времени) используются одни и те же линии. Номинальная разрядность ШД и ША- 32бита, возможно увеличение их разрядности до 64 бит. При частоте шины 33 МГц пропускная способность шины равна 132 Мбайт/с для 32 разрядной шины и 264 Мбайт/с для 64- битной шины.

Подключенные к шине устройства (функции) представляются процессору непосредственно подключенными к его шине. Им назначаются адреса из адресного пространства памяти или УВВ. Дешифрирование адреса на шине PCI распределено, т.е. выполняется в каждом устройстве. Каждое устройство отвечает только на свой адрес. Спецификация PCI требует перемещаемости всех занимаемых ресурсов в пределах доступного пространства адресации, что обеспечивает их бесконфликтное распределение для многих устройств.

С устройствами PCI процессор может взаимодействовать командами обращения к памяти и портам ввода-вывода, адресованным к областям, выделенным данному устройству при конфигурировании системы. Устройства могут вырабатывать запросы маскируемых и немаскируемых прерываний. Понятие каналов ПДП для шины PCI не вводится, но устройство может выступать в роли задатчика, поддерживая высокопроизводительный обмен с памятью без привлечения процессора. Так может быть реализован обмен в режиме ПДП с устройствами IDE, подключенными к мосту PCI- ISA (см. рисунок 8.5).

Основные сигналы шины

AD[31::00]- сигналы адреса данных. Адрес и данные последовательно во времени выдаются (мультиплексированы) на одни и те же линии шины PCI. Транзакция (обмен) шины состоит из фазы адреса, сопровождаемой одним или большим количеством фаз данных. В течение фазы адреса на линии AD[31::00] выдается физический адрес (32 бита) устройства. В фазе данных на лини AD[31::00] выдаются данные, при этом разряды AD[07::00] содержат младший значащий байт, а AD[31::24] содержат старший значащий байт.

Протокол шины PCI

В каждой транзакции (обмене по шине) участвуют два устройства- инициатор (initiator) обмена, он же мастер (master) или ведущее устройство и целевое (target) устройство (ЦУ), оно же ведомое (slave). Шина PCI все транзакции трактует как пакетные. Каждая транзакция начинается фазой адреса, за которой могут следовать одна или несколько фаз данных (см. рисунок 8.7).

Рисунок 8.7 — Цикл обмена шины PCI

1. Перечислите названия шин, входящих в состав системной платы ЭВМ IBM PC/AT 286.

2. Назовите разрядность ША и ШД периферийной шины и шины ISA.

3. Чем обусловлено использование в архитектуре ПК IBM PC/AT 286 четырех шин?

5. Какое основное отличие ШФ ША и ШД?

6. Количество кварцевых резонаторов в системной плате IBM PC/AT 286.

7. На каких микросхемах построена подсистема прерываний IBM PC/AT 286.

8. Каково назначение порта B в ЭВМ IBM PC/AT 286.

9. Каково назначение CMOS – памяти .

10. Перечислите названия шин, входящих в состав системной платы ЭВМ IBM PC/AT Pentium.

11. К какому типу шин относится шина PCI?

13. Количество прерываний, используемых в ЭВМ IBM PC/AT 286?

14. Назначение прерываний IRQ0 и IRQ1?

15. Значения тактовых частот шины PCI?

Библиографический список

- Каган Б.М. Электронные вычислительные машины и системы: Учеб. пособие для вузов. – 2-е изд. перераб. и доп. – М.: Энергоатомиздат, 1985. – 552с., ил.

2. Организация ЭВМ. 5-е изд./К. Хамахер, З. Вранешич, С. Заки.- СПб.: Питер; Киев: Издательская группа BHV, 2003. – 848 с.: ил.

3. Цилькер Б. Я., Орлов С. А. Организация ЭВМ и систем: Учебник для вузов. – СПб.: Питер, 2004. – 668 с.: ил.

4. Гук М. Аппаратные средства IBM PC. Энциклопедия. 2-е изд. – СПб.: Питер. 2001. – 928 с.: ил.

5. Сергеев Н.П., Вашкевич Н.П. Основы вычислительной техники: Учеб. пособие для электротехн. специальн. вузов. – 2-е изд. перераб. и доп. – М.: Высш. шк., 1988. – 311с., ил.

6. Балашов Е.П. и др. Микро- и мини ЭВМ: Учеб. пособие для вузов. — Л.: Энергоатомиздат, Ленингр. отд-ние, 1984. – 376с., ил.

7. Балашов Е.П., Пузанков Д.В. Микропроцессоры и микропроцессорные системы: Учеб. пособие для вузов/Под ред. В.Б. Смолова.- М., ”Радио и связь”,1981. – 328с., ил.

8. Бикташев Р.А., Князьков В.С. Многопроцессорные системы. Архитектура, топология, анализ производительности: Учеб. пособие.- Пенза: Пенз. гос. ун-т, 2003. — 217 с.

9. Компьютеры на СБИС: В 2-х кн. Кн. 2: Пер. с япон./ Мотоока Т., Сакаути М., Харикоси Х. И др.- М.: Мир, 1988.- 336с.

10. Сетевые операционные системы/ В.Г. Олифер, Н.А. Олифер.- СПб.: Питер. 2001. –544 с.

11. Шагурин И.И., Бердышев Е.М. Процессоры семейства Intel P6. Архитектура, программирование, интерфейс.- М.: Горячая линия — Телеком, 2000.- 248 с.

12. Корнев В.В., Кисилев А.В. Современные микропроцессоры.- М.: Нолидж, 1988. — 240 с.

13. Карасев В. В., Кисилев А.В. Современные микропроцессоры- 3-е изд., перераб и доп. СПб.: БХВ- Петербург, 2003. -448 с.

14. Таненбаум Э. Архитектура компьютера. 4-е изд. СПб.: Питер, 2003.-704 с.

1.3 Классификация средств ЭВТ………………………….10

1.4.1 Обобщенная структура ЭВМ……………………..…12

1.4.2 Структура ЭВМ на основе общей шины…………. 13

1.4.3 Структура ЭВМ на основе множества шин………. 14

2 АРХИТЕКТУРА КЛАССИЧЕСКОЙ ЭВМ…………….18

2.1 Принцип программного управления………………….18

2.2 Принцип хранимой в памяти программы…………….19

2.3 Обобщенный формат команд………………………….20

2.4 Способы адресации команд……………………………21

2.4.1 Процессоры с принудительным порядком выполнения команд………………………………………………………………22

2.4.2 Процессоры с естественной адресацией команд……24

2.5 Способы адресации операндов…………………………25

2.5.2 Регистровая адресация ……………………………….27

2.5.3 Косвенная адресация …………………………………27

2.5.4 Непосредственная адресация…………………………28

2.5.6 Относительная (базовая) адресация………………….29

2.5.7 Индексная (автоинкрементная или автодекрементная) адресация…………………………………………………………. 30

3. ЗАПОРМИНАЮЩИЕ УСТРОЙСТВА ЭВМ………….33

3.3 ОЗУ с произвольным доступом………………………..37

3.4 Организация микросхем SRAM ……………………….40

3.5 Организация динамической памяти …………………. 42

3.6 Особенности микросхем синхронной динамической памяти……………………………………………………………….45

3.7 Основные характеристики ЗУ…………………………..46

3.8 ОЗУ магазинного типа (стековая память)……………..48

3.10 Контрольные вопросы…………………………………54

4. ПРИНЦИПЫ ОРГАНИЗАЦИИ ПРОЦЕССОРОВ……56

4.1 Обобщенные структуры процессоров с непосредственными и магистральными связям…………………56

4.2 Декомпозиция процессора на УА и ОУ……………….58

4.3 Арифметико-логические устройства…………………..59

4.3.1 Классификация арифметико-логических устройств..59

4.3.2 АЛУ для сложения и вычитания чисел с фиксированной запятой……………………………………………60

4.3.3 АЛУ для умножения двоичных чисел……………….64

4.3.4 Методы ускорения умнож.ения………………………70

4.3.5 Особенности операций десятичной арифметики…. 72

4.3.6 Операции над числами с плавающей запятой………74

4.4 Устройства управления………………………………. 76

4.4.3 Микропрограммные УУ……………………………. 79

4.5 Структурно — функциональная организация классического процессора………………………………………. 83

4.6 Рабочий цикл процессора………………………………86

4.7 Понятие о слове состояния процессора (PSW)………87

4.8 Процедура выполнения команд перехода (условного и безусловного)………………………………………………………88

4.9 Процедура выполнения команд вызова подпрограмм..………………………………………………….…..89

4.10 Контрольные вопросы………………………………. 91

5. СИСТЕМЫ ПРЕРЫВАНИЯ ПРОГРАММ……………..92

5.2 Характеристики систем прерываний…………………..95

5.3 Схема выполнения процедуры прерывания…………. 96

5.4 Способы реализации систем прерываний……………..97

5.4.1 Схема прерывания с опросом по вектору…………. 97

5.4.2 Прерывания с программно — управляемым приоритетом………………………………………………………..98

6. ОРГАНИЗАЦИЯ ВВОДА – ВЫВОДА………………. 100

6.1 Общие сведения о вводе-выводе в ЭВМ……………..100

6.2 Основные способы ввода-вывода…………………….100

6.2.1 Программно — управляемый ввод – вывод…………101

6.2.2 Ввод — вывод с прерыванием программы…………..103

6.2.3 Ввод – вывод в режиме ПДП………………………..103

6.3.1 Характеристики интерфейсов……………………….105

6.3.2 Шины интерфейсов ввода-вывода…………………105

6.4 Контрольные вопросы…………………………………109

7. ОРГАНИЗАЦИЯ ПАМЯТИ ЭВМ С МАГИСТРАЛЬНОЙ СТРУКТУРОЙ…………………………………………………….110

7.1 Организация адресного пространства памяти и ввода-вывода. Изолированная и совмещенная адресные пространства………………………………………………………110

7.1.1 Изолированное адресное пространство памяти и ввода- вывода……………………………………………………. 110

7.1.2. Совмещенное адресное пространство памяти и ввода- вывода……………………………………………………………. 112

7.2 Организация ПЗУ. Проектирование памяти ЭВМ…. 113

7.3 Построение оперативной памяти на микросхемах статического типа…………………………………………………116

7.4 Построение оперативной памяти на микросхемах DRAM……………………………………………………………. 118

7.5 Память с чередованием адресов………………………119

7.6 Регенерация динамической памяти…………………..121

7.7.1 КЭШ прямого отображения ………………………. 124

7.7.2 Наборно — ассоциативный КЭШ…………………….127

7.8 Контрольные вопросы………………………………. 128

8.1 Структурная схема системной платы ЭВМ IBM PC/AT 286………………………………………………………………….129

8.1.1 Система шин системной платы ЭВМ IBM PC/AT 286 ……………………………………………………………………. 129

8.1.2 Состав и назначение основных устройств системной платы ЭВМ IBM PC/AT 286……………………………………. 131

8.1.2.1 Назначение и характеристики процессора и сопроцессора………………………………………………………131

8.1.2.2 Назначение и характеристики генераторов тактовых сигналов……………………………………………………………132

8.1.2.3 Назначение шинных формирователей…………. 132

8.1.2.4 Формирование управляющих сигналов и работа подсистемы памяти……………………………………………….133

8.1.2.5 Назначение и характеристики периферийных устройств системной платы……………………………………. 133

8.1.2.6 Назначение ПЗУ BIOS……………………………..137

8.1.3.1 Особенности шины ISA……………………………137

8.1.3.2 Основные сигналы шины ISA……………………..138

8.1.3.3 Шинные циклы магистрали ISA…………………..142

8.1.3.4 Электрические и конструктивные характеристики шины ISA………………………………………………………….145

8.1.3.5 Конвейеризация шины…………………………….146

8.2 Структурная схема системной платы ЭВМ IBM PC/AT Pentium…………………………………………. 147

8.2.1 Локальные шины ввода – вывода………………….147

8.2.2 Состав и назначение основных устройств системной платы ЭВМ IBM PC/AT Pentium………………………………..148

8.3 Основные сигналы шинного интерфейса процессора Pentium…………………………………………………………….149

В этой статье мы расскажем о причинах успеха шины PCI и дадим описание высокопроизводительной технологии, которая приходит ей на смену – шины PCI Express. Также мы рассмотрим историю развития, аппаратные и программные уровни шины PCI Express, особенности её реализации и перечислим ее преимущества.

История шины PCI и ее проблемы

Когда в начале 1990-x гг. она появилась, то по своим техническим характеристикам значительно превосходила все существовавшие до того момента шины, такие, как ISA, EISA, MCA и VL-bus. В то время шина PCI(Peripheral Component Interconnect — взаимодействие периферийных компонентов), работавшая на частоте 33 Мгц, хорошо подходила для большинства периферийных устройств. Но сегодня ситуация во многом изменилась. Прежде всего, значительно возросли тактовые частоты процессора и памяти. Например, тактовая частота процессоров увеличились с 33 МГц до нескольких ГГц, в то время как рабочая частота PCI увеличилась всего до 66 МГц. Появление таких технологий, как Gigabit Ethernet и IEEE 1394B грозило тем, что вся пропускная способность шины PCI может уйти на обслуживание одного-единственного устройства на основе данных технологий.

При этом архитектура PCI имеет ряд преимуществ по сравнению с предшественниками, поэтому полностью пересматривать было нерационально. Прежде всего, она не зависит от типа процессора, поддерживает буферную изоляцию, технологию bus mastering (захват шины) и технологию PnP в полном объеме. Буферная изоляция означает, что шина PCI действует независимо от внутренней шины процессора, что дает возможность шине процессора функционировать независимо от скорости и загруженности системной шины. Благодаря технологии захвата шины периферийные устройства получили возможность непосредственно управлять процессом передачи данных по шине, вместо того, чтобы ожидать помощи от центрального процессора, что отразилось бы на производительности системы. Наконец, поддержка Plug and Play позволяет осуществлять автоматическую настройку и конфигурирование пользующихся ею устройств и избежать возни с джамперами и переключателями, которая изрядно портила жизнь владельцам ISA-устройств.

Несмотря на несомненный успех PCI, в нынешнее время она сталкивается с серьезными проблемами. Среди них – ограниченная пропускная способность, недостаток функций передачи данных в реальном времени и отсутствие поддержки сетевых технологий нового поколения.

Сравнительные характеристики различных стандартов PCI

| Разрядность шины (бит) | Частота (МГц) | Пропускная способность (МБ/c) | Целевой рынок |

| 32 | 33 | 132 | Десктопы/мобильные системы |

| 32 | 66 | 264 | Серверы |

| 64 | 33 | 264 | Серверы |

| 64 | 66 | 512 | Серверы |

Следует учесть, что реальная пропускная способность может быть меньше теоретической из-за принципа работы протокола и особенностей топологии шины. К тому же общая пропускная способность распределяется между всеми подключенными к ней устройствами, поэтому, чем больше устройств сидит на шине, тем меньшая пропускная способность достается каждому из них.

Такие усовершенствования стандарта, как PCI-X и AGP были призваны устранить ее главный недостаток – низкую тактовую частоту. Однако увеличение тактовой частоты в этих реализациях повлекло за собой уменьшение эффективной длины шины и количества разъемов.

Новое поколение шины — PCI Express (или сокращенно PCI-E), было впервые представлено в 2004 году и было призвано решить все те проблемы, с которыми столкнулась её предшественница. Сегодня большая часть новых компьютеров снабжается шиной PCI Express. Хотя стандартные слоты PCI в них тоже присутствуют, однако не за горами то время, когда шина станет достоянием истории.

Архитектура PCI Express

Архитектура шины имеет многоуровневую структуру, как показано на рисунке.

Шина поддерживает модель адресации PCI, что позволяет работать с ней всем существующим на данный момент драйверам и приложениям. Кроме того, шина PCI Express использует стандартный механизм PnP, предусмотренный предыдущим стандартом.

Рассмотрим предназначение различных уровней организации PCI-E. На программном уровне шины формируются запросы чтения/записи, которые передаются на транспортном уровне при помощи специального пакетного протокола. Уровень данных отвечает за помехоустойчивое кодирование и обеспечивает целостность данных. Базовый аппаратный уровень состоит из двойного симплексного канала, состоящего из передающей и принимающей пары, которые вместе называются линией. Общая скорость шины в 2,5 Гб/с означает, что пропускная способность для каждой линии PCI Express составляет 250 Мб/c в каждую сторону. Если принять во внимание потери на накладные расходы протокола, то для каждого устройства доступно около 200 Мб/c. Эта пропускная способность в 2-4 раза выше, чем та, которая была доступна для устройств PCI. И, в отличие от PCI, в том случае, если пропускная способность распределяется между всеми устройствами, то она в полном объеме достается каждому устройству.

На сегодняшний день существует несколько версий стандарта PCI Express, различающихся своей пропускной способностью.

Пропускная способность шины PCI Express x16 для разных версий PCI-E, Гб/c:

Форматы шины PCI-E

На данный момент доступны различные варианты форматов PCI Express, в зависимости от предназначения платформы – настольный компьютер, ноутбук или сервер. Серверы, требующие большую пропускную способность, имеют больше слотов PCI-E, и эти слоты имеют большее число соединительных линий. В противоположность этому ноутбуки могут иметь лишь одну линию для среднескоростных устройств.

Видеокарта с интерфейсом PCI Express x16.

Платы расширения PCI Express очень похожи на платы PCI, однако разъемы PCI-E отличаются повышенным сцеплением, что позволяет быть уверенным в том, что плата не выскользнет из слота из-за вибрации или при транспортировке. Существует несколько форм-факторов слотов PCI Express, размер которых зависит от количества используемых линий. Например, шина, имеющая 16 линий, обозначается как PCI Express x16. Хотя общее количество линий может достигать 32, на практике большинство материнских плат в настоящее время оснащены шиной PCI Express x16.

Карты меньших форм-факторов могут подключаться в разъемы для больших без ущерба для работоспособности. Например, карта PCI Express х1 может подключаться в разъем PCI Express x16. Как и в случае шины PCI, для подключения устройств при необходимости можно использовать РCI Express-удлинитель.

Внешний вид разъемов различных типов на материнской плате. Сверху вниз: слот PCI-X, слот PCI Express х8, слот PCI, слот PCI Express х16.

Express Card

Стандарт Express Card предлагает очень простой способ добавления оборудования в систему. Целевым рынком для модулей Express Card являются ноутбуки и небольшие ПК. В отличие от традиционных плат расширения настольных компьютеров, карта Express может подключаться к системе в любой момент во время работы компьютера.

Одной из популярных разновидностей Express Card является карта PCI Express Mini Card, разработанная в качестве замены карт форм-фактора Mini PCI. Карта, созданная в этом формате, поддерживает как PCI Express, так и USB 2.0. Размеры PCI Express Mini Card составляют 30×56 мм. Карта PCI Express Mini Card может подключаться к PCI Express х1.

Преимущества PCI-E

Технология PCI Express позволила получить преимущество по сравнению с PCI в следующих пяти областях:

- Более высокая производительность. При наличии всего одной линии пропускная способность PCI Express в два раза выше, чем у PCI. При этом пропускная способность увеличивается пропорционально количеству линий в шине, максимальное количество которых может достигать 32. Дополнительным преимуществом является то, что информация по шине может передаваться одновременно в обоих направлениях.

- Упрощение ввода-вывода. PCI Express использует преимущества таких шин, как AGP и PCI-X и обладает при этом менее сложной архитектурой, а также сравнительной простотой реализации.

- Многоуровневая архитектура. PCI Express предлагает архитектуру, которая может подстраиваться к новым технологиям и не требует значительного обновления ПО.

- Технологии ввода/вывода нового поколения. PCI Express дает новые возможности получения данных при помощи технологии одновременных передач данных, обеспечивающей своевременное получение информации.

- Простота использования. PCI-E значительно упрощает обновление и расширение системы пользователем. Дополнительные форматы плат Express, такие, как ExpressCard, значительно увеличивают возможности добавления высокоскоростных периферийных устройств в серверы и ноутбуки.

Заключение

PCI Express – это технология шины для подключения периферийных устройств, пришедшая на смену таким технологиям как ISA, AGP и PCI. Её применение значительно увеличивает производительность компьютера, а также возможности пользователя по расширению и обновлению системы.

Читайте также: